集成电路(IC)先进封装按照技术特点主要分为扇入型(Fan-in)封装和扇出型(Fan-out)封装两种。传统的晶圆级封装以扇入型结构为主,主要应用于I/O引脚数量较少的集成电路芯片,通过扇入型封装完成再布线并形成与外部互连的焊球或铜柱凸点。随着基带处理器、电源管理芯片、汽车安全系统毫米波雷达模组、5G芯片、生物/医疗器件和应用处理器要求的不断提高,使得芯片I/O的需求数量越来越多,传统扇入型封装已经不能完成在其芯片面积内的多层再布线和凸点阵列排布,由此扇出型晶圆级封装(Fan-out Wafer Level Packaging,FoWLP)方式应运而生。

扇出型晶圆级封装通过圆片/晶圆重构增加单个封装体的面积,应用硅通孔(TSV)、凸点(Bumping)等先进制造工艺完成多层再布线和凸点制备,切割分离后得到能够与外部电性能互连的封装体。2010年,有行业研究机构就已经指出未来FoWLP封装主要是替换更高I/O(>1000引脚)的BGA封装型式。

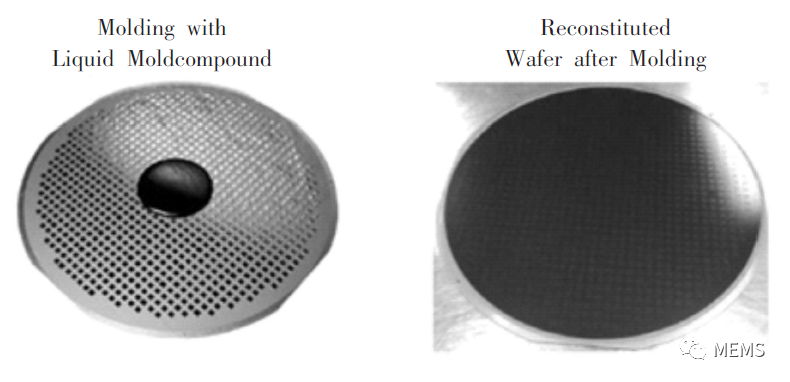

扇出型晶圆级塑封前后对比

据麦姆斯咨询报道,近期,富仕三佳机器有限公司汪洋等人在《模具制造》期刊上发表了以“扇出型晶圆级塑封过程中芯片偏移的研究综述”为主题的论文。文章介绍了近10年来扇出型晶圆级塑封压缩成型工艺对制品性能,尤其是芯片偏移(die-shift)的影响。从工艺、材料和设备等方面进行了参数化研究,并提出了扇出型晶圆级塑封设备的设计要求。

对扇入/扇出型晶圆级封装的研究,主要是基于8寸硅基载板。随着塑封工艺和技术的不断成熟,以及低成本的需求,12寸晶圆级载板、载板和环氧树脂塑封料CTE值对芯片偏移的研究逐渐增多。研究者通过注射成型工艺和压缩成型工艺设备的研发,对比两种不同成型工艺,压缩成型工艺在控制12寸晶圆芯片偏移方面具有明显优势,塑封后产品的厚度一致性<20μm。

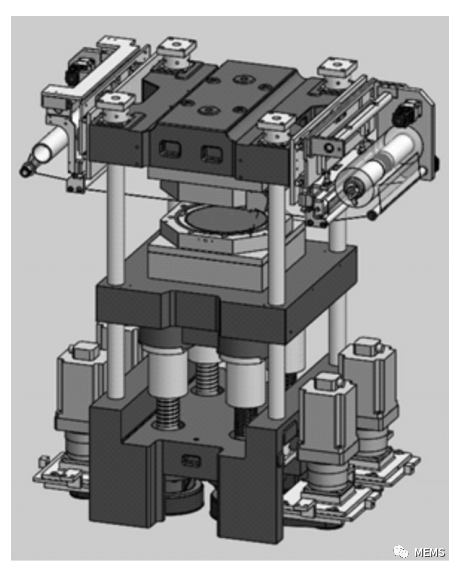

四轴同步晶圆级压缩成型设备

关于芯片偏移的研究经历了从单一参数到复合参数的过程,从材料、工艺和设备多角度进行了深入的研究。随着低CTE玻璃载板和液体、颗粒、栅格状环氧树脂逐渐成熟的应用,未来扇出型面板级封装将会有较大的发展和研究空间,取代扇出型晶圆级封装的部分市场,成为新的研究热点。

从扇出型封装在手机基带芯片封装中的首次应用(英飞凌嵌入式晶圆级球栅阵列eWLB)到现在已经过去15年的时间,期间由于BGA封装形式的快速发展,经历了一段时间的低谷。但是随着传统摩尔定律逐渐走到尽头、先进系统级封装逐渐成为延续摩尔定律,甚至超越摩尔定律的重要解决方案。基于低芯片偏移量的设计,未来扇出型晶圆级塑封设备需要能够实现以下功能:稳定低速的压缩速度(10μm/s),甚至更稳定更低速,模面匀温性液体树脂125°±3°,模具型腔的高真空功能(<100pa)和高平面精度的模面加工技术(600mm x 600mm的模面平面度<5μm)。