我们研究了一些经典的运算放大器电路。这些电路中运用了负反馈,因此通常就可以使运算放大器工作在线性区域内。

我们研究了一些经典的运算放大器电路。这些电路中运用了负反馈,因此通常就可以使运算放大器工作在线性区域内。

但是,也可以将运算放大器用作比较器,从而使其以非线性方式工作。由于其输入受到硬驱动,因此其输出电压会对电源轨产生猛烈的冲击。如下文所示,这可能并不总是一种好的设计方法。

在线性应用中,可以对运算放大器做如下理想假设:无限增益和带宽、零输出阻抗、无限输入阻抗,以及输入之间为零伏。也可以将运算放大器以非线性方式使用,但有一些地方要特别注意和处理。

一种常见的配置是仅使用开环运算放大器(无反馈),从而让其高增益产生比较器工作。没有负反馈,两个输入就不一定保持相同的电压,因此上述第四点理想运算放大器假设也就无效。

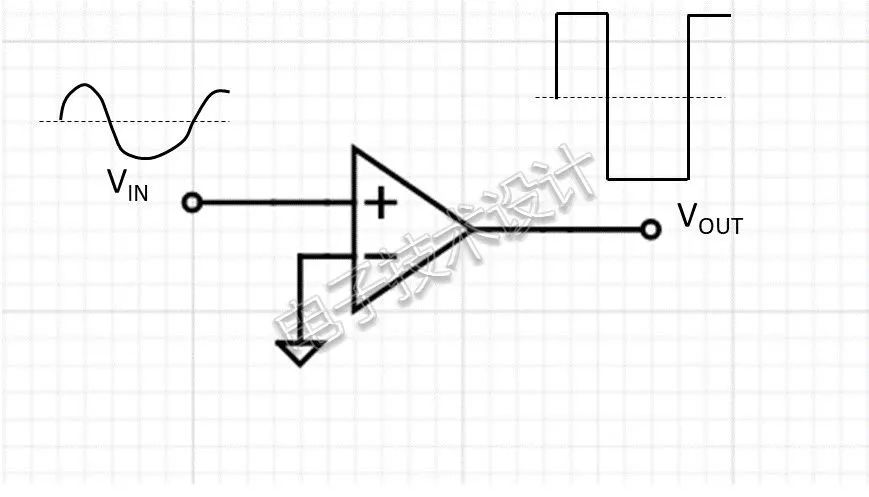

图1显示了开环配置的运算放大器。当VIN大于零时,输出电压变高,并被限制在正电源电压附近。当输入电压变为负值时,运算放大器输出将摆动为负值,并再次被限制在负电源电压附近。这里假设运算放大器是由常规的正负电源电压供电。

图1:将运算放大器用作零阈值电压比较器。

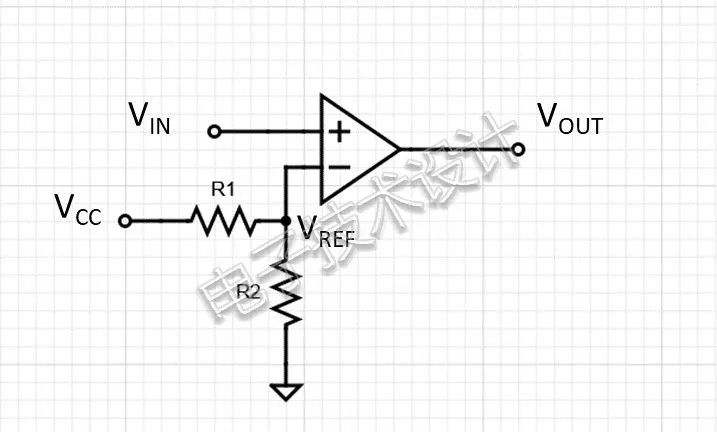

上述比较器电路在零伏附近工作。图2在该电路中增加了一个电阻分压器,对反相输入端的电压进行设置,从而提供了一种控制比较器参考电压VREF的方法。

图2:带有电阻分压器的运放比较器,可对阈值电压进行设置。

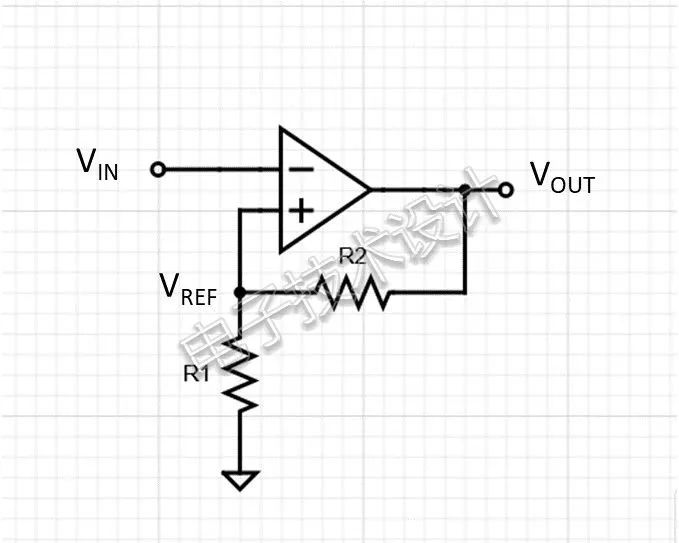

图3显示了另一种常见的设计技术,即向比较器添加迟滞。在这种情况下,输入电压对运算放大器的反相输入进行驱动,VREF则连接至同相输入。R1-R2电阻分压器从输出VOUT产生VREF。当VIN降至VREF以下时,输出电压变高,从而导致VREF变成更高的电压。

图3:运放比较器电路通过正反馈来增加迟滞。

类似地,当VIN转换为高于VREF时,VOUT变为最大负输出电压,从而将VREF拉低。这种迟滞效应在输入信号上存在有任何噪声时,就可以防止其在过VREF转换时造成比较器工作反向。

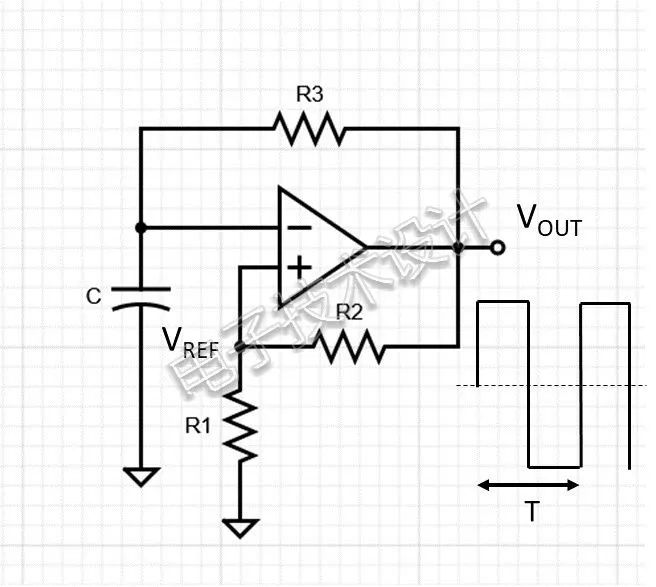

图4中的多谐振荡器电路使用图3中的R1-R2迟滞电路以及RC定时电路来产生方波输出。实际上,它不是比较器电路。取而代之的是,它将运算放大器用作比较器来创建所需的输出波形。假设VOUT一开始为高电压,那么它就会通过R3为C充电。电容器电压就会增加,同时这个过程与时间常数R3-C保持一致。

图4:多谐振荡器电路添加RC定时电路以产生方波输出。

当电容器电压变得大于VREF时,输出电压将摆动至负电源电压。这将导致电容器电压被驱动为负,这个过程同样与时间常数R3-C保持一致。R1-R2分压器将在同相输入上提供一定的迟滞,从而使运放实现平稳过渡。欲知有关元件值如何确定多谐振荡器频率的详细信息,请参见参考文献4。

网上有很多关于这类非线性运放电路的文章。但是,当我查看一些IC供应商的网站时,我注意到他们强烈警告不要将运算放大器用作比较器[参考文献1和参考文献2]。其主要问题包括:

一些运算放大器的输入上有钳位二极管,因此会限制两个输入之间的最大电压。这可以通过精心设计或选择其他运算放大器来解决。

比较器应用会将运算放大器驱动到饱和状态。从饱和状态恢复过来可能很慢,而且通常没有指定。

大多数运算放大器的输出电压摆幅可能接近正负电源电压。这可能有所指定也可能没有,而且可能无法实现很好的控制。

与为该特定应用设计的“真实比较器”相比,运算放大器的开关时间趋于较慢。

运算放大器的输出通常不设置为对数字逻辑进行驱动,因此可能需要使用其他电路来对其进行调整。

想要将运放用作比较器的主要原因可能是,有时使用一个多运放器件,正好剩余了其中一个放大器。毕竟,它就在那里,可以免费使用。如果您决定采用这种方法,则需要对数据手册进行仔细研究,并评估实际电路性能是否井然有序。然后就是要确保运放电路具有相当大的内置裕量。

上述非线性运放工作的考虑因素,也可能有助于我们理解线性应用中可能出现的一些问题。是否有可能运放的输出被驱动到轨电压?如果是这样,恢复需要多长时间?这对电路的性能有影响吗?

因此,许多IC供应商都建议用户使用真实的比较器而不是运算放大器。毕竟,比较器就是设计用作比较器。它具有指定的开关特性和输出驱动,通常设置为用来驱动逻辑器件。有许多经济型器件可供选择。

点击关注,每天学电

▼