本文由半导体产业纵横编译自nextplatform

世界上为其他所有人构建服务器的超大规模者、云构建者、HPC 中心和 OEM 服务器制造商都希望,最重要的是,组件供应商之间的竞争以及定期、可预测、几乎无聊的新组件推出节奏。通过这种方式,每个人都可以定期消费,而那些实际制造每年消耗的 1200 万台服务器(并且还在增长)的 ODM 和 OEM 可以预测需求并管理他们的供应链。

然而,正如许多聪明人所说,IT 组织购买路线图,他们不购买单点产品,因为他们必须管理风险。

在英特尔最终推出出色的 64 位服务器芯片设计之后,AMD 于 2010 年在服务器的市场开始出现瓶颈——2009 年初推出的“Nehalem”Xeon E5500 架构很大程度上是从 AMD 大获成功的 Opteron 系列中复制而来的的芯片。AMD 早期的 Opteron 具有创新性,支持 64 位、多核、HyperTransport 互连和芯片上的多核,从本质上讲,英特尔看起来像是一个只推出 32 位 Xeon 并试图让企业采用 64 位的安腾( Itanium)芯片。但到2010年,AMD已经推迟了几代Opterons的交付,并且做出了一个架构分叉,但没有成功。当英特尔放弃安腾,设计了许多代具有竞争力的64位Xeon服务器芯片时,AMD基本上被挤出了数据中心。但到2015年,英特尔的创新步伐开始疲软,市场要求更多的竞争,因此,AMD进行了重组,并开始创造其Epyc的回归——这一次再次恰逢英特尔因其10纳米和7纳米芯片制造过程的延迟,而让对手抓到了机会。

在首席执行官帕特·盖辛格 (Pat Gelsinger) 的指导下,英特尔正在让其芯片制造厂井井有条,同时也恢复了可预测且更快速的性能和功能增强节奏,这意味着 AMD 必须做同样的事情。作为本周 Data Center Premier 活动的一部分,AMD 的高层展开了路线图,并表明他们不仅将坚持 Epyc 世代的常规节奏和完美执行,而且将深化Epyc 路线图包括不同的变体和 SKU,以追逐服务器市场的特定部分和非常精确的工作负载。

在 AMD 总裁兼首席执行官 Lisa Su 发表主题演讲之前,公司首席技术官 Mark Papermaster 和 AMD 数据中心和嵌入式解决方案事业部总经理 Forrest Norrod 介绍了 Epyc 服务器芯片的深化路线图。这是在推出带有 3D V-Cache 的“Milan-X”Epyc 7003 的背景下完成的,该产品将许多 HPC 和 AI 工作负载的性能提高了 50%,并将于 2022 年第一季度推出,并且“Aldebaran”Instinct MI200 GPU 加速器,现在开始出货,需要注意的是,改芯片用在了橡树岭国家实验室安装的1.5 exaflops“Frontier”超级计算机中。可以肯定的是,Milan-X 和 Instinct MI200 是本周 AMD 活动的亮点,但它们并不是 AMD 在其路线图上谈论的唯一内容,我们还需要考虑其他一些问题比 AMD 本身更进一步推动了这一路线图。

“它们都是在过去四年中开始扩大我们在数据中心的产品组合的大量工作的结晶,”Norrod 解释说,指的是 Milan-X 和 Aldebaran。“所以特别是在 CPU 方面,你应该考虑沿着合理的足迹快速进入市场。长期以来,我们一直认为,当我们通过某个点时,特别是考虑到数据中心工作负载复杂性的增加,我们将不得不开始扩大我们的产品范围,并且始终注意我们如何在这样的情况下做到这一点。我们保持执行保真度的方式。我们需要让客户真正轻松地采用更多工作负载的特定产品。这是我们讨论的中心主题:工作负载的特殊性,拥有针对数据中心市场的特定细分市场进行调整的产品。通过这样做,我们确保我们可以继续在这些细分市场中的每一个领域提供领导力绩效和领导力 TCO。”

Norrod 没有做出具体承诺,但表示我们应该期待使用 AMD 计算 GPU 的芯片和产品组合的扩大和深化。

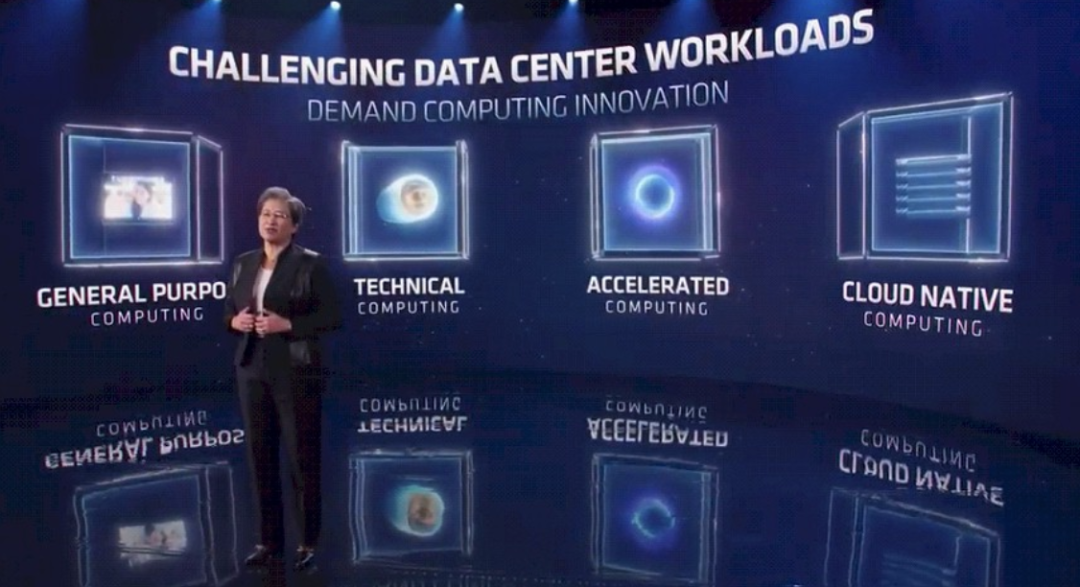

在她的主题演讲中, Lisa Su将数据中心分为四个部分,并解释了 AMD 将如何使用独特的芯片来针对每个部分。

“通用计算涵盖了最广泛的主流工作负载,包括本地和云端,” Lisa Su 解释说。“socket级性能是一个重要的考虑因素。技术计算包括数据中心中一些要求最高的工作负载。在这里,每个核心的性能对这些工作负载最重要。加速计算专注于人类理解的前沿,解决气候变化、材料研究和基因组学等科学领域,高度并行和海量计算能力才是真正的关键。对于云原生计算,需要最大的内核和线程密度来支持超大规模应用程序。为了在所有这些工作负载中提供领先的计算能力,我们必须采用量身定制的方法,专注于硬件、软件和系统设计的创新。”

有了这个,让我们来看看 Su、Norrod 和 Papermaster 谈到的 Epyc 路线图,然后看看我们放在一起的增强和扩展路线图,以便为您提供更全面的认识。

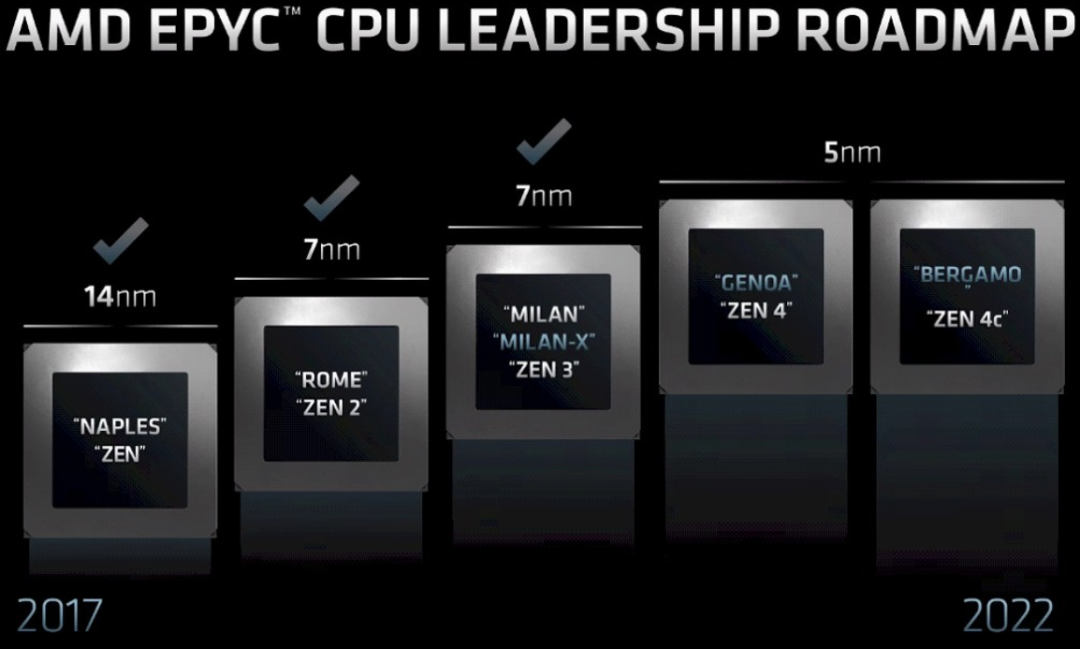

这是他们都谈到的 Epyc 路线图:

您可以看到添加了“Milan-X”芯片,以及“Genoa”系列中的另一个芯片,称为“Bergamo”,采用 Zen 4c 内核,即将推出的 Zen 4 内核的变体,计算芯片的封装与标准的Genoa不同。但这并不是你得到的全部。

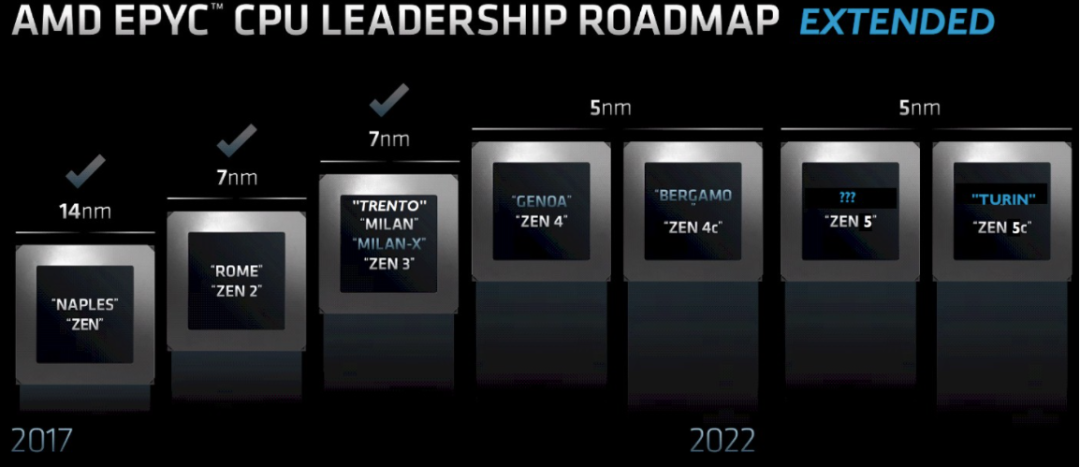

还有 Milan处理器的“Trento”变体,它将用作 Frontier 系统中 MI200 GPU 加速器的 CPU 主机。然后将是第二代 5 纳米 Epyc 处理器,我们还听到了代号为“Turin”的高核数版本,现在我们看到了更具有启发性的 AMD 服务器芯片路线图,看起来非常像 Bergamo的后续,而不是Genoa。这也许意味着对Genoa将会有不同后续版本。

无论如何,这是我们看到的扩展版的 AMD Epyc 路线图:

让我们来看看这个。

正如我们本周所知,Milan-X 将由几个 Milan 芯片的 SKU 组成,其中两排 L3 缓存堆叠在裸片上的本机 L3 缓存之上,将总 L3 缓存增加三倍以提高性能. 我们从演示文稿中知道有 16 核变体和 64 核变体,我们假设可能还有更多——24 核和 32 核,可能是 48 核——所有这些变体都得到了成比例的数量添加了额外的 L3 缓存(每个内核多出 3 倍)。

通过 Trento,我们听说 Milan 处理器复合体上的 I/O 和内存集线器小芯片在两个方面得到了增强。首先是 I/O 集线器支持 Infinity Fabric 3.0 互连,这意味着 Trento 芯片可以与连接到它的任何 Instinct MI200 加速器一致地共享内存。这是 Frontier 的必要功能,因为 Oak Ridge 在之前基于 IBM Power9 CPU 和 Nvidia V100 GPU 加速器的“Summit”超级计算机上具有一致的 CPU-GPU 内存。据传,Trento I/O 和内存集线器小芯片的另一项增强是在控制器上支持 DDR5 主内存。据我们所知,Trento 集线器小芯片还支持 PCI-Express 5.0 控制器和 CXL 加速器协议,这可能在 Frontier 中很有用。

Milan、Milan-X 和 Trento 都适合 SP3 服务器插座,最高 TDP 为 400 瓦。

借助 Genoa 和 Bergamo 芯片,AMD 正在转向台积电的 5 纳米芯片蚀刻工艺,Papermaster 表示,在相同的 ISO 频率下,该工艺可提供两倍的晶体管密度和两倍的晶体管功率效率,同时还提升了晶体管的开关性能提高了 25%。非常清楚:这不是Milan到Genoa的声明,而是 7 纳米工艺到 5 纳米工艺的声明,这如何导致服务器芯片性能取决于架构以及 AMD 如何在频率和电压曲线上转动刻度盘。AMD 还为这些处理器迁移到更大的 SP5 插槽。

Genoa 基于 Zen 4 内核,而 Bergamo 基于 Zen 4c 内核,与 Milan 系列芯片中的 Zen 3 内核相比,每时钟指令 (IPC) 具有相同的改进 – 以及相同的微体系结构,因此没有软件使用它所需的调整 - 但它在频率和电压的优化曲线上有一个不同的点,并且在缓存层次结构中进行了一些优化,使Bergamo更适合在 Epyc 包中拥有更多的计算小芯片或 CCD。与 Zen 3 核心相比,Zen 4 核心 IPC 的提升预计将在 29% 的范围内,因此这将是单线程性能以及Genoa吞吐量性能的重大变化。Begamo 将吞吐量性能提升到更高的极限,但会牺牲一些每线程性能来实现这一目标。

Genoa Epyc 7004 将拥有 96 个 Zen 4 内核,跨越四组三个计算块,总共十几个计算块,以及一个支持 DDR5 内存、PCI-Express 5.0 控制器和 CXL 协议的 I/O 和内存集线器最重要的是将加速器、内存和存储连接到计算复合体。Genoa将于 2022 年某个时候启动;我们不太清楚何时,因为 AMD 正在把握时机以领先于英特尔,英特尔一直在改变其“Sapphire Rapids”和“Granite Rapids”至强 SP 的发布日期。

有几种方法可以获得Bergamo将提供的 128 个 Zen 4c 内核。Bergamo 芯片可以使用八个 16 核计算块,而不是 Genoa 中的 12 个 8 核计算块。芯片也可以有 12 个 12 核tiles,然后将每个tiles上的一些核心倒回去,将核心数一直拨回到Bergamo封装中的 128 个总核心。后者似乎与前者的可能性相同,但如果两个处理器都有十二个内存控制器,正如传言那样,那么它将是后一种情况。Trento I/O 和内存集线器支持 8 个计算小芯片,而 Genoa I/O 和内存集线器支持 12 个计算小芯片,因此 AMD 可以采用任何一种方式到达Bergamo,但同样,如果它使用 Trento I/O 和内存中心,那么Bergamo将被降级为只有八个内存控制器,这将导致计算内存容量和带宽不平衡。看起来Bergamo将使用Genoa I/O 和内存集线器,因此,并有一些部分失效的内核,因此它最大为 128 个内核而不是 144 个内核。Papermaster 所说的只是,Bergamo 的物理设计和 Chiplet 配置与 Genoa 不同,所以大家在这一点上都在猜测。

Bergamo 芯片将插入与Genoa相同的 SP5 插槽,这是超大规模和云构建者关心的。据 Lisa Su称,Bergamo 将在 2023 年上半年上市,但 Norrod 最初表示可能在 2022 年底至 2023 年初推出。目前尚不清楚为什么这需要这么长时间来上市。可能是超大规模和云构建者最近才与 AMD 进行对话,让 AMD 承担风险并承担额外成本来制作 Gemoa 处理器的特殊 SKU。

在这之后是Bergamo和Gemoa ,看起来Bergamo实际上是传闻中的256核“Turin”处理器,该处理器是基于最近传言的未来的Zen 5c内核。

我们不认为普通用途的Genoa会从96核跃升到256核,但跃升到192核是合理的。这就是我们认为 在我们上面的扩展路线图中,Genoa中会出现标有“???”的内容。(除非另有说明,否则我们将称其为 Florence。)该芯片可能有四个计算块,每个块有 12 个 Zen 5 核心,在每个核心复合体中,并且封装上有四个核心复合体,以达到理论上的 192 个通用核心Epyc 7005。人们说Turin超大规模变体将有 256 个内核和高达 600 瓦的热设计点。此处的计算块可能基于 16 个 Zen 5c 内核,打包成一个四块计算复合体,其中四个在包装上。

我们认为将会有带有堆叠 3D V-Cache 的 Genoa-X 和 Florence-X 变体,甚至有可能看到也具有增强的 L3 缓存的 Bergamo-X 和Turin-X 变体。

有传言说 Epyc 7005s 将基于台积电的 3 纳米工艺,但我们认为 AMD 将尝试从 5 纳米中获得两代芯片,Genoa的演进版本和Turin基于改进的 5 纳米工艺,就像罗马一样是 7 纳米, Milan是第二次的更新。如果像两个月前传闻的那样,台积电的 3 纳米工艺出现延迟,情况尤其如此。Epyc 7005s 可能是 2024 年末到 2025 年初的产品——同样,这将取决于许多活动部件以及英特尔的表现如何,以及当时服务器领域发生的其他事情。10 exaflops 的超级计算机将需要这些 CPU。

我们强烈怀疑 Genoa kicker 和 Turin 处理器将适合与 Genoa 和 Bergamo 相同的 SP5 服务器插槽。如果您每代都更改插槽,会为服务器制造商造成麻烦。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。