论及此问题,输出电容的两种影响至关重要:对输出电压纹波的影响,以及在负载瞬变后对输出电压的影响。

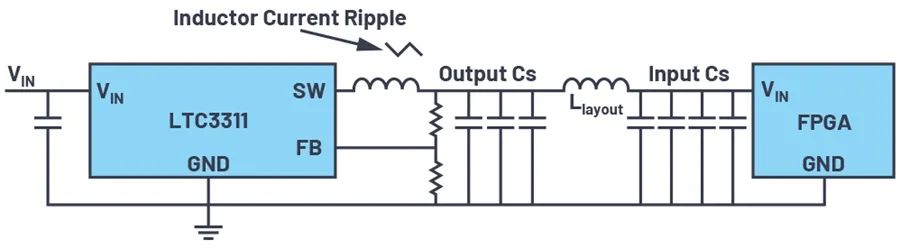

首先,我们来看一看输出电容这个词。这些电容一般安装在电源的输出端。但是,许多电力负载(电力消耗对象),例如FPGA,都需要使用一定数量的输入电容。图1显示的是一种典型的包含负载和FPGA的电源设计。如果在电路板上,电压生成电路和耗电电路之间的距离非常短,那么电源输出电容和负载输入电容之间的界限就会变得非常模糊。

图1. LTC3311 开关稳压器,包含所连接的FPGA对应的输出电容和输入电容。

通常需要利用某种物理分隔方法来加以区分,而这会导致产生大量寄生电感(Llayout)。

电源输出端的电容形成决定了降压型(降压)开关稳压器的电压纹波。此时,经验法则适用:输出纹波电压等于电感纹波电流 X 输出电容的电阻。

这个电阻ZCout由电容的大小和数量,以及等效串联电阻(ESR)和等效串联电感(ESL)组成。如果电源输出端只有一个电容,此公式高度适用。如果是更为复杂的情况(参见图1),其中包含多个并联电容,且因为布局(Llayout)的原因产生了串联电感,那么计算不会如此简单。

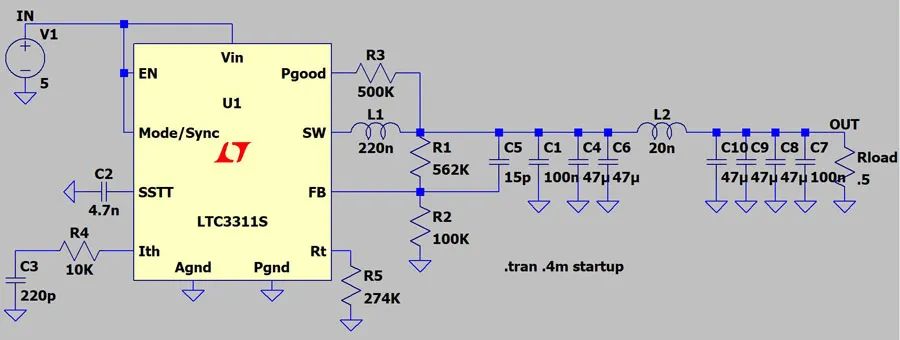

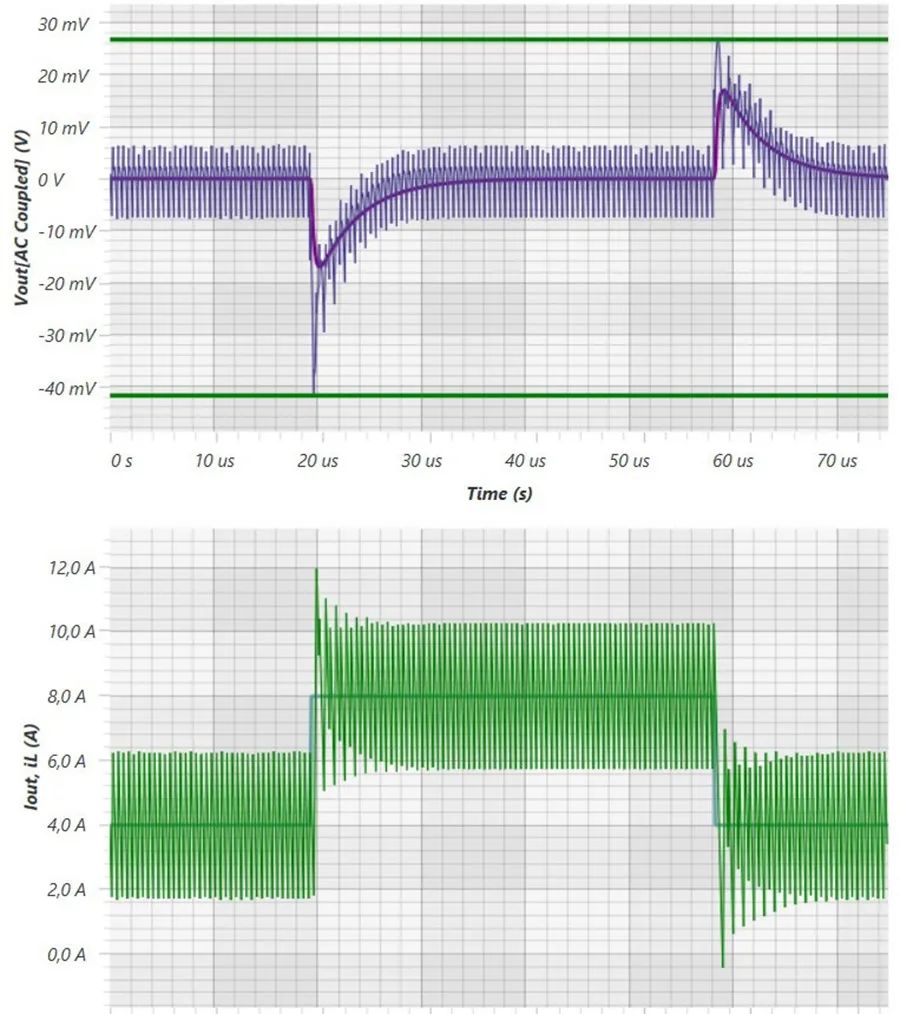

在这种情况下,非常适合使用LTspice®这样的模拟工具。图2所示为针对图1提到的情况快速创建的电路图。可以将不同值(包括ESR和ESL)设置给单个电容。也可以考虑板布局(例如Llayout)可能产生的影响。然后,会仿真开关稳压器输出端和负载输入端的电压纹波。

图2. 使用LTspice评估系统电源输出端的不同电容。

输出电容也会影响负载瞬变后的输出电压失调。我们也可以使用LTspice仿真这一影响。此时,特别需要注意的是,在某些限制范围内,电源控制环路的控制速度和输出电容的电感是相互关联的。电源控制环路的速度如果更快,那么在负载瞬变之后,只需要更少数量的输出电容即可保持在特定的输出控制窗口之内。

最后但同样重要的一点是,vvv具有自适应电压定位(AVP)。AVP可以利用输入误差电压预算并减少输出电容器的数量,此外,设计人员还可以通过增加环路带宽来实现减少输出电容的数量。

AVP在低负载条件下稍微增大输出电压,在高负载条件下稍微降低输出电压。然后,如果发生负载瞬变,则更多动态输出电压偏差都发生在允许的输出电压范围内。

建议使用ADI公司的LTpowerCAD®来找出哪些控制环路可以优化,以及可以减少多少个输出电容。图3所示为计算控制速度的屏幕截图。其中显示了在负载瞬变后计算得出的电压过冲。可以通过改变输出电容、调节开关稳压器控制环路的速度来进行优化。

图3. 使用LTpowerCAD优化开关稳压器的控制环路,以及减少输出电容的数量。

确定正确的参数后,即可减少电源中输出电容的数量,如此可以节省资金和板空间,我们建议大家使用这个开发步骤。