▼关注公众号:工程师看海▼

前几天,和芯片设计的朋友聊天,才知道懂得太少,更多是基础不牢。回头又把相关学习笔记整理一下,算是温故知新。

设计部分:关于DDR设计,做过多种产品,有消费类,高速类,还有医疗的,不管是因特尔,还是赛灵思的,DDR的设计部分一般都是参考公版,相关的规则一般都是严格执行,也就是说这部分,终端产品所谓研发都是知其然不知其所以然,所以出问题的概率如果有,都是直接对接芯片厂商来解决。这里面需要关注芯片是否导入PINDELAY的问题,特别以后做DDR5的设计。

测试部分:DDR相关测试,只是测一些时序,读/写上下边沿,以及建立&保持时间,占空比等指标。PI部分的电源纹波测试。至于眼图,一般都是用大厂提供的软件进行Margin测试,相关的数值标准也是软件自带的,里面的原理知识,理透底层逻辑的少。这也是后面学习的方向。

仿真部分:说到仿真,三大主流软件(SIGRITY,ADS,ANSYS)都是各自的解决方案,以SIGRITY为例,SI 部分Power SI & System SI;PI 部分IR Drop(DC),PDN(AC),以及Optimize PI。

预警:文章很基础且比较长,点赞加收藏,以备后用。

DDR(Double Data Rate SDRAM),双倍速率同步动态随机存储器,是内存的一种。

SDRAM(Synchronous dynamic random-access memory),同步动态随机存取内存,是有一个同步接口的动态随机存取内存(DRAM)。

SRAM(Static Random-Access Memory),静态随机存取存储器。“静态”指这种存储器里面储存的数据就可以长时间保持。

DRAM(Dynamic Random-Access Memory),动态随机存取存储器。“动态”里面所储存的数据保留时间比较短,数据会周期性地更新。

ROM(Read-Only Memor),只读存储器。掉电之后信息不会丢失。常用于存储各种程序和数据。PROM,EPROM,EEPROM不做过多展开。

RAM(Random Access Memory),随机存储器。掉电之后数据随之丢失。常用于暂时存储程序、数据和中间结果。

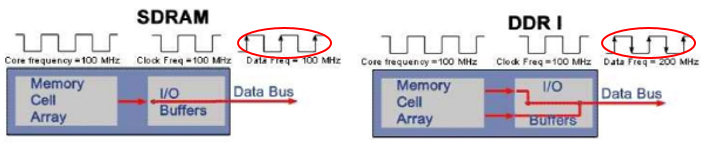

DDR 所谓的双倍,不是提高时钟频率,本质上采样方式变化,上升沿和下降沿读/写数据,因而数据速率是SDRAM的两倍。如下图:

传输速率MT/S (M:Million兆):每秒兆次数据传输,单位时间内的传输速率。MT/S>/S是QPI(QuickPath Interconnect)的数据传输单位,类似于MHz相对于FSB。

FSB(Front Side BUS)前端总线,是CPU与北桥芯片之间的数据传输总线。

北桥芯片,从Intel5系列就不用北桥芯片。笔者在2012年开始做消费类产品,经常听同事讲起这些。北桥芯片负责联系内存、显卡等数据吞吐量最大的部件。CPU就是通过前端总线(FSB)连接到北桥芯片,进而通过北桥芯片和内存、显卡交换数据。前端总线是CPU和外界交换数据的最主要通道。

有北桥芯片就有南桥芯片。南桥芯片负责I/O总线之间的通信,如PCI总线、USB、LAN、ATA、SATA、音频控制器、键盘控制器、实时时钟控制器、高级电源管理等。

PCH全称为Platform Controller Hub,是intel公司的集成南桥。北桥中的内存控制器和PCIe控制器都集成到了CPU内部,相当于整个北桥芯片都集成到了CPU内部,主板上只剩下南桥。所以PCH可以理解成南桥。这时,PCH与CPU之间的连接总线采用DMI(Direct Media Interface),直接媒体接口,采用PCI-Express总线,换来更高的性能。

FSB与QPI(Quick Path Interconnect)都是前端数据总线,它们之间的区别是:QPI的传输速率比FSB的传输速率快一倍。QPI总线的数据传输速率是两倍于总线时钟速率。5GT/s的总线速率其总线时钟频率是 2.5GHz。

Pinout Description

CK_t,CK_c:差分时钟。地址&控制信号在上升沿和下降沿交叉处采样。

CKE,(CKE1):时钟使能。读/写过程中保持高电平,自刷新(Self-Refresh)和预充电(Precharge)保持低电平。

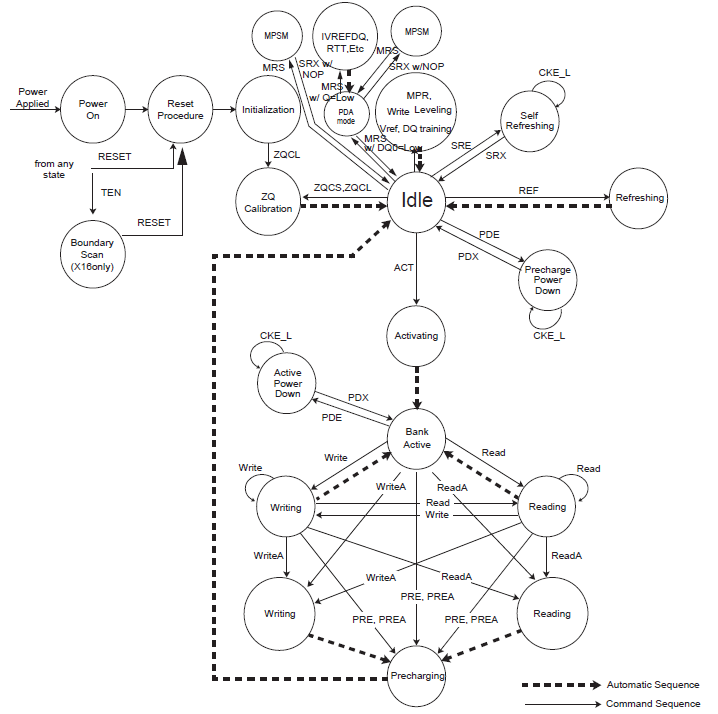

看到自刷新和预充电,那就讲一下。

DRAM(Dynamic Random-Access Memory),动态随机存取存储器。它要不断进行刷新(Refresh)才能更新数据。刷新操作与预充电中重写的操作一样,都是用Sensor-Amplifier敏感放大器先读再写。不同的是刷新是周期性的,而预充电是不定期的。

刷新有自动刷新(Auto Refresh)与自刷新(Self Refresh),这两种刷新都是内部的自动操作,不需要外部提供地址信息。

预充电是寻址的独立性,比如对同一行L-Bank(Logical Bank)的另外一行进行寻址,就要关闭现有行,重新打开新的一行。

CS_n, (CS1_n):片选。低电平有效。CS_n可被认为命令代码。

C0,C1,C2:芯片ID。

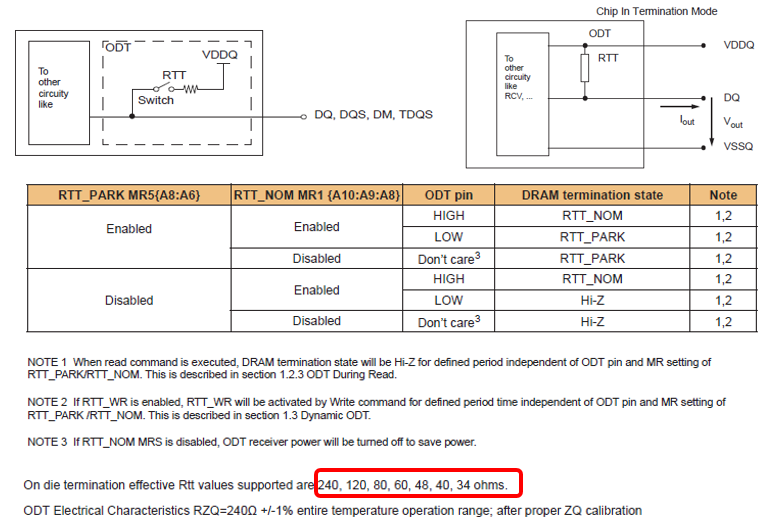

ODT,(ODT1):片上终端使能,使能片内终端电阻。有六种选项阻值。

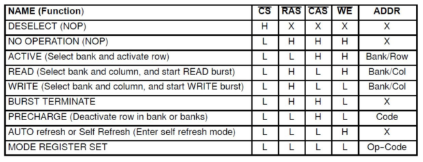

ACT_n:Activation Command Input激活命令输入。ACT_n 为低,RAS_n/A16,CAS_n/A15,WE_n/A14寻址,ACT_n 为高,RAS_n/A16,CAS_n/A15,WE_n/A14为命令输入,比如读/写或者其他真值表的命令。

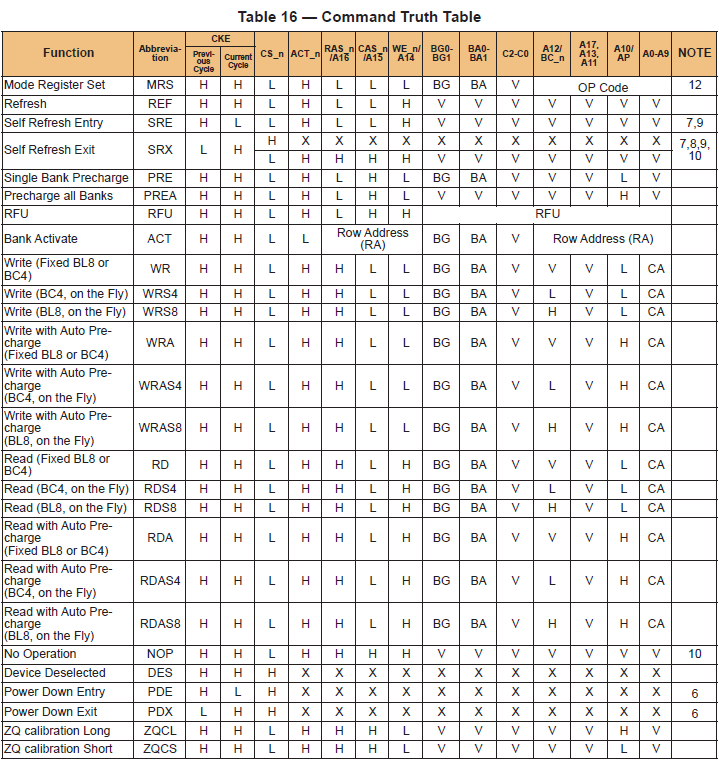

命令状态真值表

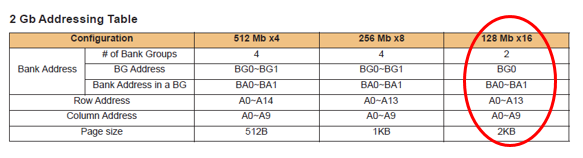

BG0&BG1,BA0~BA2:

Bank是存储库,内存划分多组存储库,BG为区域选择,X4/X8对应BG0/BG1,X16对应BG0;BA为Bank选择,BA0~BA2为3位,说明有8个Bank。

Bank地址线位宽为3,Bank数目为 2^3=8;行地址线位宽为14,列地址线位宽为10;2^3 * 2^14 * 2^10 = 2^27 =2^7Mb = 128Mb,加上数据线,则容量为 128 Mb x 16 = 256M Byte =2G bit。

RAS_n:行地址选通。CAS_n:列地址选通。WE:写使能。

A0 - A17:地址线分为行地址线和列地址线。地址线和列地址线是分时复用的,即地址要分两次送出,先送出行地址,再送出列地址。

A10/AP:在读/写时候,对A10进行采样决定是否自动预充Autoprecharge,高为是,低为否。在预充时,对A10采样,高为所有Bank,低为当前Bank。

RESET_n:芯片复位,低电平有效。

DQS_t, DQS_c:数据选通信号。DQL0~DQL7为低7位,DQU0~DQU7为高8位。读的时候为输出,写的时候为输入。

TDQS_t, TDQS_c:对寄存器功能选通,只针对X8颗粒使用,X4/X16关闭该功能。

PAR:命令和地址奇偶校验输入,输入奇偶校验应保持在时钟的上升沿,并同时与CS_n LOW的命令和地址保持一致。

ALERT_n:输出信号指示错误:CRC错误标志,命令和地址奇偶校验错误标志等。在连通性测试模式下,此引脚用作输入。是否使用此信号取决于系统。如果未作为信号连接,则必须将ALERT_n引脚绑定到板上的VDD。

TEN:连通性测试模式启用:X16器件上必选,在密度等于或大于8Gb的x4 / x8上为可选输入。高电平有效。是否使用此信号取决于系统,可以通过一个弱下拉电阻将DRAM内部将此引脚拉低至VSS。

DM:控制信号, 数据掩码功能。在DDR进行写操作时,通常采用突发模式。需要注意的是DM信号和数据信号是同时发出,接收方在DQS的上升与下降沿来判断DM的状态,如果DM为高电平,那么之前从DQS中部选取的数据就被屏蔽了,对于突发写入,如果其中有不想存入的数据,仍可以运用DM信号进行屏蔽。为了屏蔽不需要的数据,人们采用了数据掩码(Data I/OMask,简称DQM)技术。通过DQM,内存可以控制I/O端口取消哪些输出或输入的数据。这里需要强调的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。

ZQ:输出驱动校准参考引脚。

电源部分

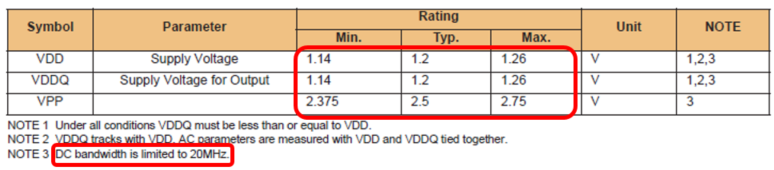

VDDQ:提供数据输入输出电源1.2V+/-0.06V

VSSQ:提供数据输入输出地

VDD:提供电源1.2V+/-0.06V

VSS:地

VPP:提供DRAM激活电源2.5V(最低2.375V,最高2.75V)

VREFCA:CA参考电压

注意:输入引脚(BG0-BG1,BA0-BA1,A0-A17,ACT_n,RAS_n / A16,CAS_n / A15,WE_n / A14,CS_n,CKE,ODT和RESET_n)不提供端接。

UDIMM(Unbuffered Dual In-Line Memory Modules):无缓冲双列直插内存模块。地址和控制信号不经缓冲器,无需做任何时序调整,直接到达DIMM上的DRAM芯片。UDIMM由于在CPU和内存之间没有任何缓存,因此同频率下延迟较小。UDIMM需保证CPU到每个内存颗粒之间的传输距离相等,这样并行传输才有效,而这需要较高的制造工艺,因此UDIMM在容量和频率上都较低,一般用于家用。

RDIMM(Registered Dual In-line Memory Module):地址和控制信号经过寄存,时钟经过PLL锁相。相对于UDIMM,RDIMM更稳定,容量更大,对于单个的读写访问要滞后一个时钟周期。定位于工作站和服务器。

LRDIMM(Load-Reduced Dual In-line Memory Module):使用简单缓冲,不使用比较复杂的寄存器。缓冲降低了在下层主板上的电力负载,但对性能几乎无影响。

SODIMM(Small Outline Dual In-Line Memory Modules):UDIMM和RDIMM都隶属于DIMM,内存模组的长度等,包括金手指的信号分布在内都是一样的。而SODIMM可以理解为小一号的内存模组,一般用于尺寸有要求的笔记本市场。

说到SODIMM,和前面的SDRAM有区别。SDRAM是一种存储机制,DIMM是一种模块类型。

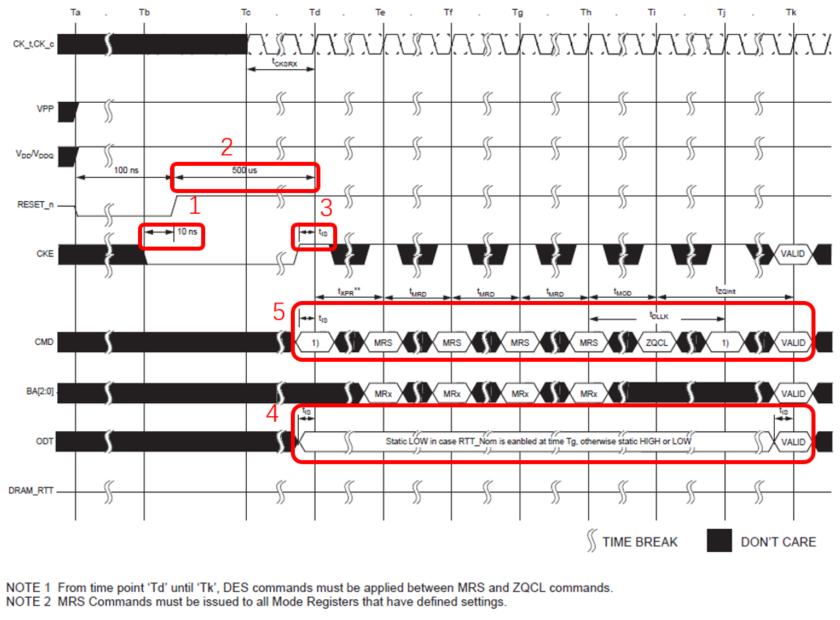

复位和上电初始化

①通电时(Ta之后),RESET_n为LOW(≤0.2x VDD),至少保持200us。在 RESET_n无效前,CKE被拉低至少10ns,下图1处。电压(300mv到VDD最小值)的跳变时间至少大于200ms。跳变期间,VDD ≥VDDQ and (VDD-VDDQ) < 0.3volts。VPP跳变必须同时或者早于VDD和VPP。

②RESET_n无效,等待500us直到CKE使能,下图2处。这段时间,DRAM完成内部初始化,独立的外部时钟

③CKE使能之前,Clocks启动且保持至少10ns,下图3处。CKE是同步信号,建立时间和时钟符合。

④DDR SDRAM 的ODT保持高阻态直到RESET_n启动。ODT保持高阻态在RESET_n失效之后直到CKE为高电平。详情见下图4处。

⑤CKE为高电平,等待复位退出,在MRS模态配置命令执行之前。寄存器各种模态配置,这里面包括BG/BA等Bank的初始化。见下图5处。

⑥ZQ校准,各种调试,写均衡操作等,知道器件就绪稳定。

复位和关闭电源的初始化过程,和上电的步骤类似,不做展开。

相关的命令执行情况,可以参考命令真值表:

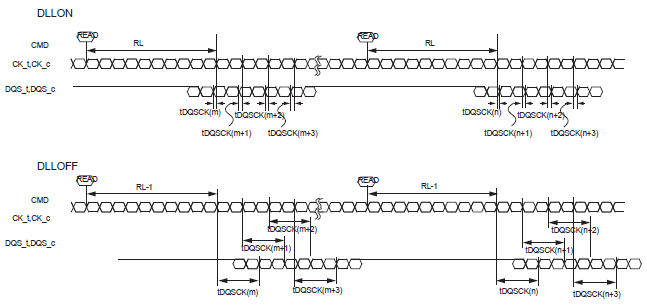

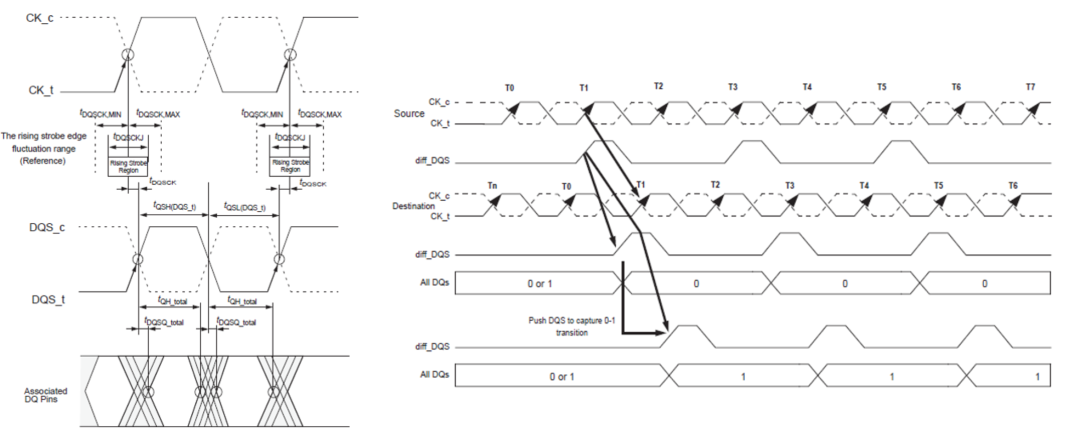

DLL(Delay-Locked Loop):延迟锁相环。不同于PLL,不涉及频率和电压转换。DDR SDRAM有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟。因为温度、电压波动等原因,这两个时钟不能保持同步,这个时候就需要根据外部时钟动态去修正内部时钟,来保持两个时钟的同步,就是让CK和DQS边沿对齐。至于实现DLL的两种方法,一个是时钟频率测量法(CFM,Clock Frequency Measurement),一个是时钟比较法(CC,Clock Comparator),工作原理和差异就不做展开。

读/写时序图:

在数据写入(Write)时,DQS和DQ信号相差90°相位,因此DDR芯片才能够在DQS信号的控制下,对DQ和DM信号进行双沿采样;而在数据读出(Read)时, DQ和DQS信号是同步的,都是和时钟沿对齐的。这时候为了要实现对DQ信号的双沿采样,DDR控制器就需要自己去调整DQS和DQ信号之间的相位延时,这也就是DDR系统中比较难以实现的地方。

对于DDR设计而言,信号完整性仿真和分析的大部分工作,实质上就是要保证数据读/写的正确性。

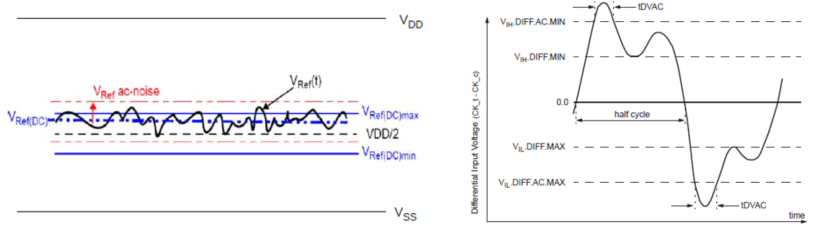

DDR电源模块,关注直流电压的范围。当然整个电源部分的PI都需要考虑,下图为主要电源的范围。红色标记中,20MHz是测试电压纹波所选择的示波器带宽,这是为了避免数字电路的高频噪声影响纹波测量,保证测试的正确性。

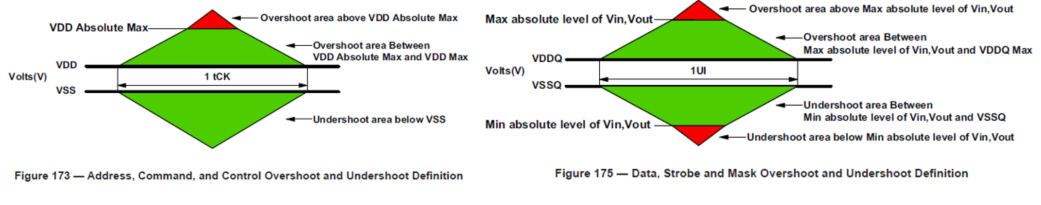

除了DC部分,还有AC部分。我们在测试过程中,关注其单调性,还有相关标准的最大/最小值。

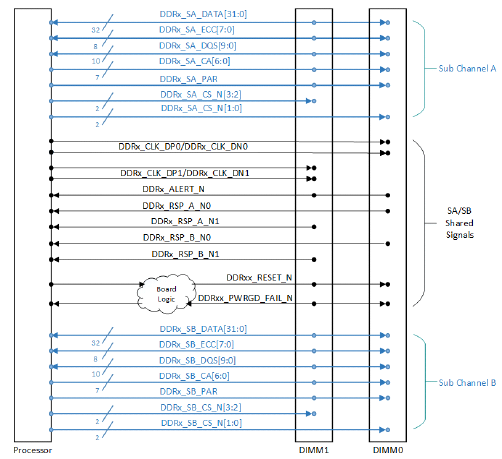

关于DDR 版图设计部分,相关的设计规则:

走线的线宽和线距根据叠层,满足相关阻抗和串扰的要求;

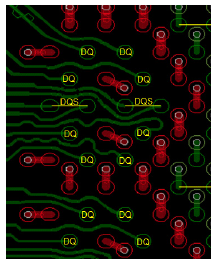

信号(DQ, DQS, ECC, CA, CS and CLK)走线保证回流路径的完整,针对DQS出Pin区域也推荐回流地孔;

CK和DQS的差分信号P/N是5mils匹配;

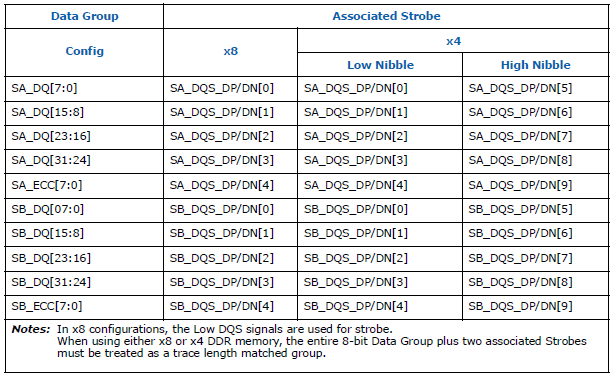

每个DIMM的数据选通DQS管控组内的DQ/ECC进行长度匹配,同一组信号走线在同一层,保证时延等长;

注意X8/X4复用:

SMT Connector DIMM-TO-DIMM走线方式:

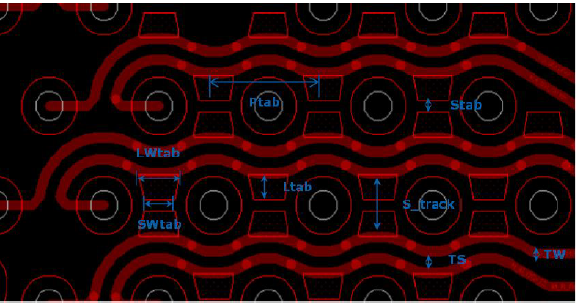

出Pin区域Tab Routing走线:

Tab Routing,做个相关的仿真,可能是精度问题,没有发现在S参数上太大的变化。

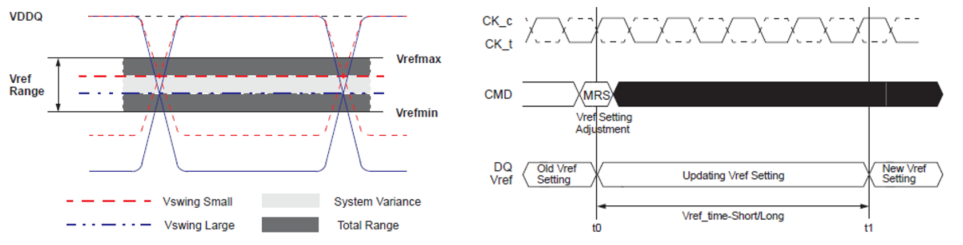

还有一个信号:Vref

DDR4数据信号的参考电平VrefDQ是由芯片内部自己产生的,没有外接该电平的管脚,只有地址信号的参考电平管脚VrefCA。

这个信号线有些SPEC,推荐走短而粗的线,线宽推荐20mils。

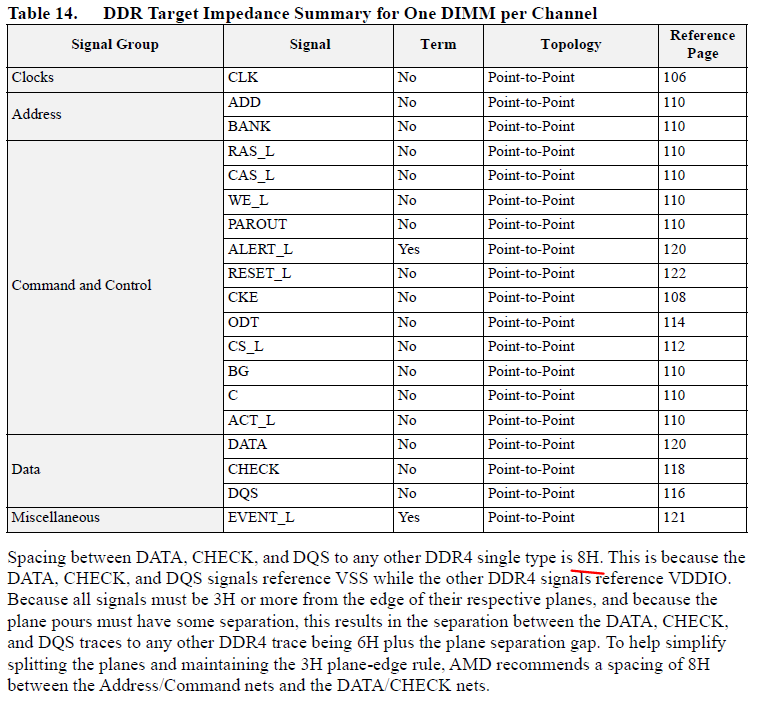

至于DDR走线的相关间距和要求,详见下图:

参考文献:JESD79-DDR4, DDR3_SDRAM,信号电源完整性仿真分析与实践

相关SPEC电子文档加微私发。只用于学习交流。

---The end---

限时免费扫码进群,交流更多行业技术

推荐阅读▼

电池、电源

硬件文章精选

华为海思软硬件开发资料