半导体技术快速发展,双倍数据速率同步动态随机存取存储器(Double Data Rata Synchronous Dynamic Random Access Memory, DDR SDRAM)的信号完整性问题已成为设计难点。文中提出了一种基于 ANSYS 软件和 IBIS 5.0 模型的 DDR4 SDRAM 信号完整性仿真方法。利用 IBIS 5.0 模型中增加的复合电流(Composite Current)、同步开关输出电流等数据,对 DDR4 SDRAM 高速电路板的信号完整性进行更准确的仿真分析。仿真结果表明:高速信号在经过印制板走线和器件封装后,信号摆幅和眼图都有明显恶化;在仿真电路的电源上增加去耦电容后,信号的抖动和收发端的同步开关噪声(Synchronous Switching Noise, SSN)都得到明显改善;在不加去耦电容的情况下,将输入信号由 PRBS 码换成 DBI 信号,接收端的同步开关噪声有所改善,器件的功耗可以降为原来的一半。

互联网通信系统不断发展,近年出现 5G 通信、人工智能、云计算、大数据等,它们对硬件计算能力和数据传输速率提出了更高要求。DDRSDRAM 由于具有密度高、容量大、读写速度快等特点而广泛应用。随着芯片制造工艺、系统级封装(System In Package, SIP)、硅通孔(Through Silicon Via, TSV)、扇出(Fan-out)等技术的发展,商用 DDR 技术已经发展到了第 4 代,即DDR4 SDRAM。

相对于 DDR3 SDRAM 采用的多点分支单流架构,DDR4 SDRAM 采用了点对点传输架构,传输速率和频宽都有很大提高 。DDR4 SDRAM的工作电压为 1.2V,还支持休眠模式。此外,DDR4 SDRAM 的数据接口采用伪开漏极接口(Pseudo Open Drain, POD),还支持数据总线转位(Data Bus Inversion,DBI)功能,采用 POD和 DBI 功能,将大多数信号驱动到高电平,可以减少芯片 IO 的功耗 。这些新增加的功能,在降低芯片功耗的同时,也使得 DDR4 SDRAM 相对于 DDR3 SDRAM 具有更低的信号传输误码率。DDR SDRAM 系统大多采用并行总线拓扑走线结构,信号线密度高、传输速度快,其系统的成败很大程度上取决于印制电路板的信号完整性,印制电路板的信号完整性问题对系统设计者来说是一大挑战。DDR4 SDRAM 相对于原来的DDR SDRAM,传输速度更快,对印制板的信号完整性要求更高。当前国外,如英特尔、思科、三星、赛灵思等公司都有专门的信号完整性研究部门,对 DDRSDRAM 的信号完整性有比较成熟的设计方案。在国内, DDR SDRAM 的信号完整性研究起步较晚,目前只有华为、中兴等知名企业有比较成熟的设计案例。本文基于 ANSYS 软件,利用 IBIS 5.0 模型,对 DDR4 SDRAM 的信号完整性进行仿真分析,其中主要包括:印制板走线模拟仿真、器件封装模拟仿真,去耦电容对信号抖动和收发端同步开关噪声影响模拟仿真,DDR4 SDRAM 的 DBI 功能对器件功耗和接收端同步开关噪声影响的模拟仿真。

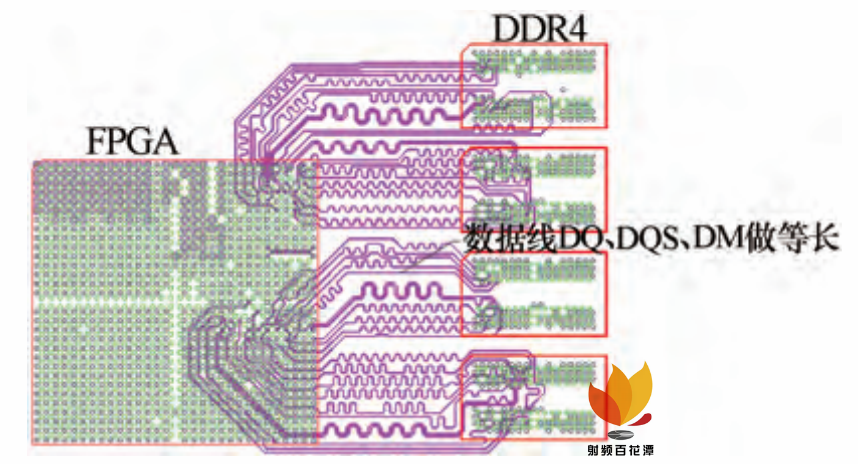

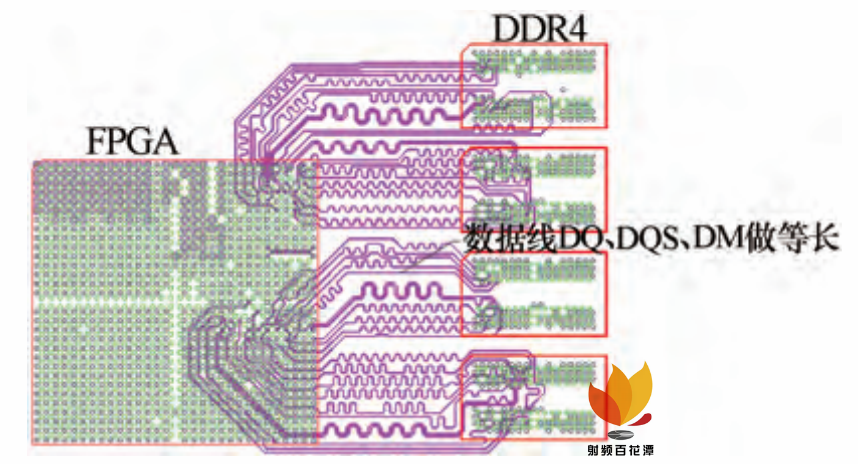

DDR SDRAM 高速电路板的走线密度很高,结构很复杂,为了满足走线要求,一般都采用单端数据线形式,但随着 DDR 速率的提高,从DDR4 SDRAM 开始,数据线开始采用差分走线结构。为了提高 DDR4 SDRAM 高速电路板的信号完整性,需要对 DDR4 SDRAM 各种类型的信号线进行分组,保证组内信号线等长,组间的时序合理。信号线大致分为:数据信号线、地址信号线、时钟信号线、控制信号线这四组。DDR4 SDRAM 中数据信号包括数据输入输出信号(Data Quad Input/Output, DQ)、数据选取脉冲信号(Data Quad Strobe, DQS)、数据屏蔽信号(Data Mask, DM)这三种信号。其中 DQ、DM为单端走线,DQS 为差分走线。所有数据信号线做等长处理,数据信号线间保持三倍的线宽距离,并且保持参考平面的完整,以减少信号线之间的串扰;走线时,要尽量减少数据信号线换层而引起的回路不连续,DDR4 SDRAM 高速电路板布局布线图如图 1 所示。此外由于信号过孔会产生串联电感效应,残孔会产生电容效应,因而还要根据高速电路板厚与传输速率,选择合适的走线层以此确定信号过孔的长度和残孔的长度。三星公司发表的关于 LPDDR3 的高速电路板优化设计和赛灵思发表的关于 DDR4 2400 的高速电路板优化设计都提到了采用短过孔长度的设计可以让 DDR 得到比较好的信号完整性。此外增加去耦电容,有助于提高高速电路板的信号完整性 。

图 1 DDR4 SDRAM 高速电路板布局布线图地址信号线与数据信号线的走线方式相类似,所有的地址信号线也要做等长处理,走线沿线也需要有完整的参考平面来保证阻抗连续。时钟信号线为差分信号,在高速电路板上采用菊花链拓扑走线方式。地址和控制信号在做工作状态判断的时候,都是通过时钟的边沿做触发的,所以时钟信号线和地址、控制信号线的走线需要等长。控制信号线主要包括 CS、CKE、RESET 等控制线,大多为使能信号,频率较低,只要保持等长,阻抗连续,线之间的间距满足要求即可。

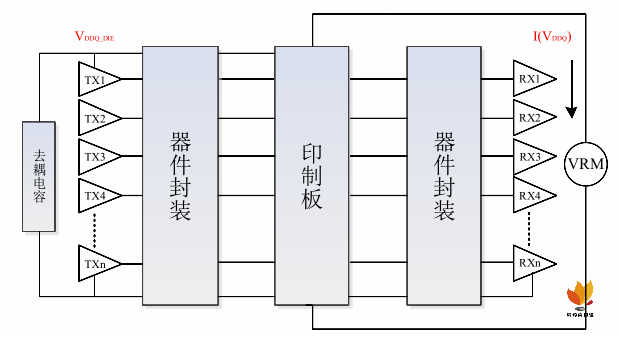

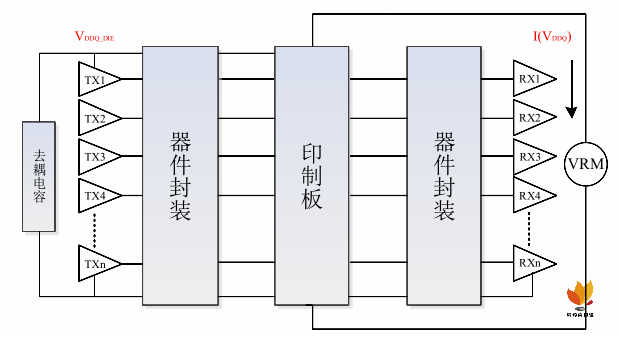

相对于传统的 SPICE 模型,IBIS 模型在仿真精度和仿真时间上做了很好的平衡,IBIS 模型的精度主要决定于电压/电流和电压/时间数据表精度,数据表的数据量很小,计算时间短。而 SPICE模型是以文本的形式,对于 DDR4 SDRAM 这种复杂仿真设计,建立基于 SPICE 模型的仿真链路要花费大量时间,而且相对于 IBIS 模型仿真出错率更高。本文采用美光公司 MT40A512m16JY-075E(IBIS 5.0 power aware Models) 的 DDR4 模型,此模型相对于 IBIS 4.2 模型增加了复合电流、同步开关输出电流等数据,这些数据可以提高信号完整性仿真的准确性。驱动芯片为 FPGA 芯片,其 IBIS 模型从其官网下载得到,仿真电路的原理框图,如图 2 所示。

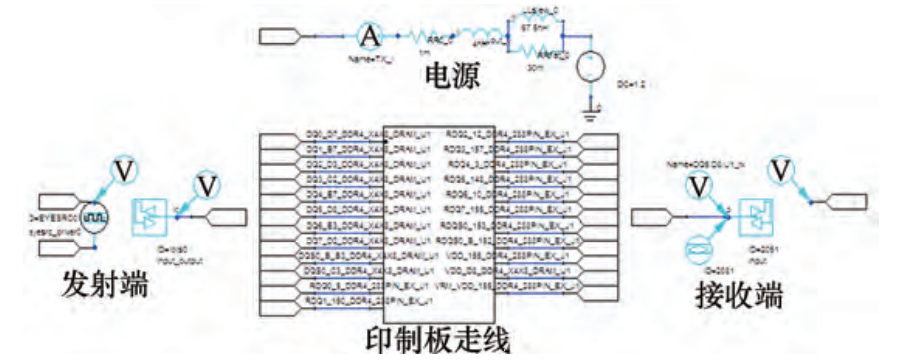

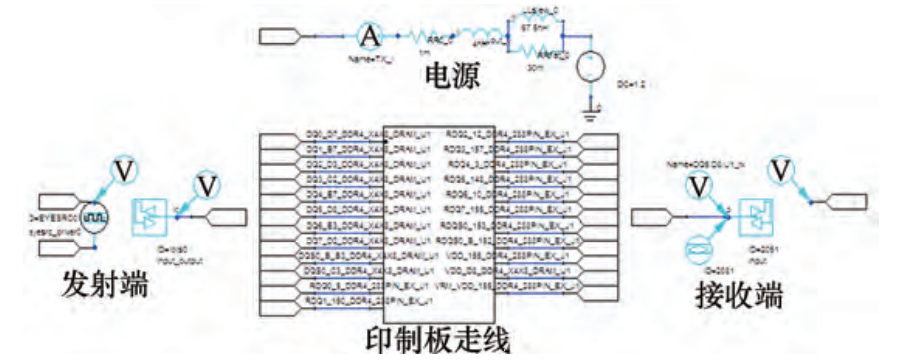

整个仿真平台所用的高速电路板中包含 1 片FPGA 读写控制芯片,4 片 DDR4 SDRAM 芯片,印制板的特征阻抗为 40Ω。仿真参数设置如下:接口电压为 1.2V, 数据速率为 3200Mbps,数据DQ 信号为 POD 信号,时钟、地址、控制信号为SSTL 信号。通过SIwave2018.0内的SIwizard功能自动在ANSYS Electronics Desktop 中产生仿真电路 。DDR4 SDRAM 仿真电路图,如图 3 所示。其中左边为发射端电路,右边为接收端电路,它们的参数由 DDR4 SDRAM 和 FPGA 的 IBIS 模型决定,正中间为高速电路板走线提取的参数,它通过 SIwave2018.0 软件提取得到,此外仿真电路图还包括电源部分。

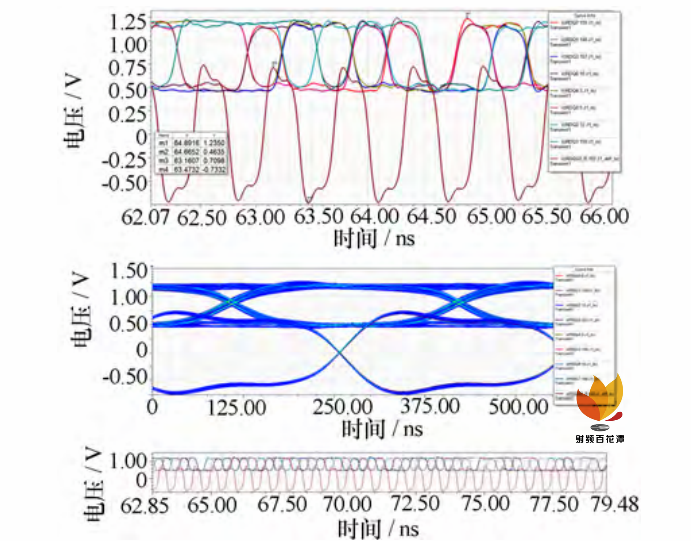

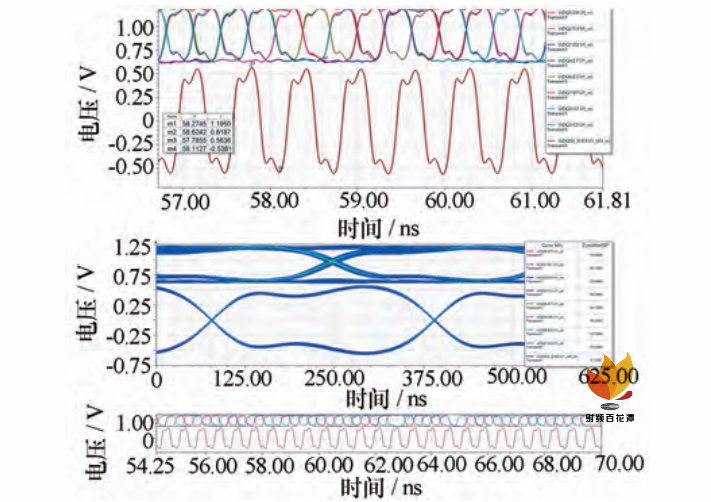

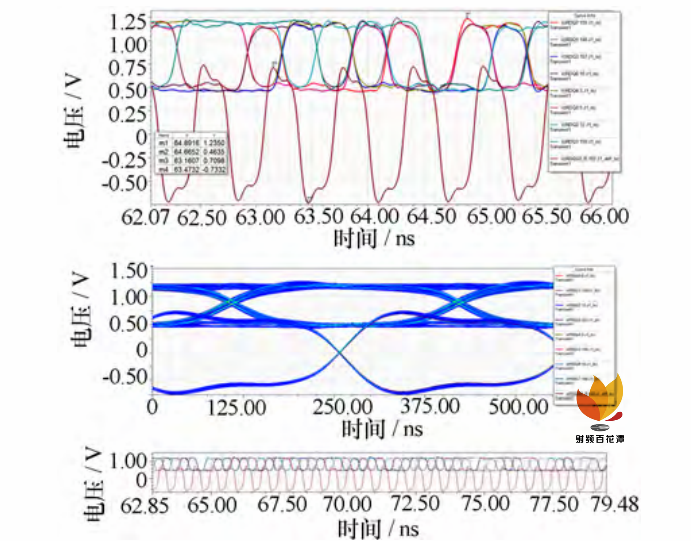

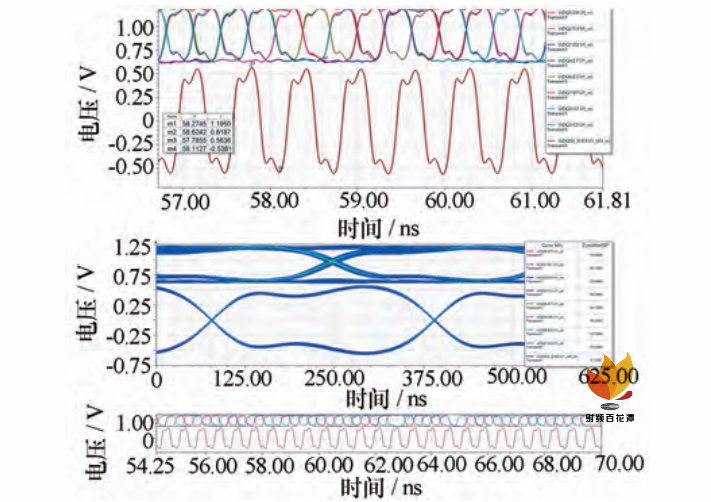

按照图 3 所示连接仿真电路,仿真电路中包含 8 路单端的 DQ0- DQ7 数据信号线,和 1 路差分的 DQS 差分数据信号线,DDR4 SDRAM 的IBIS 5.0 模型中端接电阻选择 48Ω。仿真设置时,在 DQS 信号发射端加时钟信号,在 DQ 信号发射端加 PRBS 码。通过瞬态仿真,得到图 4 和图 5仿真结果,其中图 4 为发射端瞬态仿真波形和眼图,图 5 为接收端瞬态仿真波形和眼图。从仿真结果看出:开启芯片的片上终端功能(On-Die Termination, ODT)后,8 路 DQ 数据信号的交叉点会上移,但信号峰值保持在 1.2V,DQS 信号的眼图交叉点则保持在 0V;经过印制板走线和器件的封装对信号的衰减后,DQ 数据的信号峰值由0.77V 变为 0.58V,DQS 数据的信号峰值由 0.73V变为 0.56V,而相对于 DQ 信号,DQS 信号的抖动比较小(由于仿真加的激励信号不同)。 图 4 无去耦电容发射端瞬态仿真波形和眼图

图 4 无去耦电容发射端瞬态仿真波形和眼图

图 5 无去耦电容接收端瞬态仿真波形和眼图

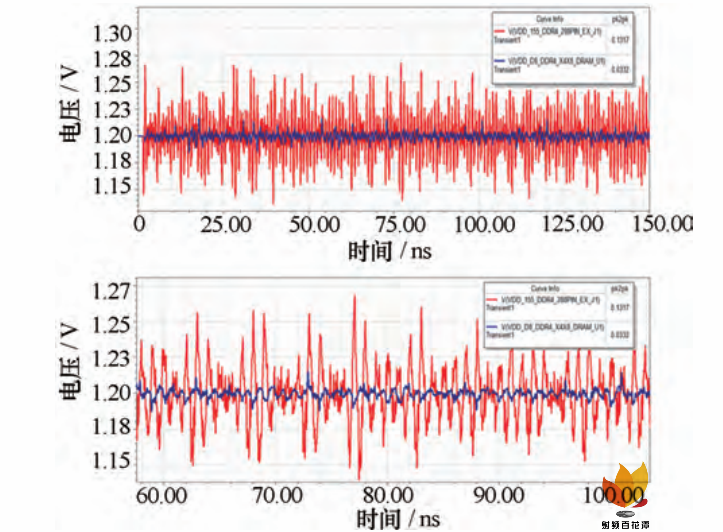

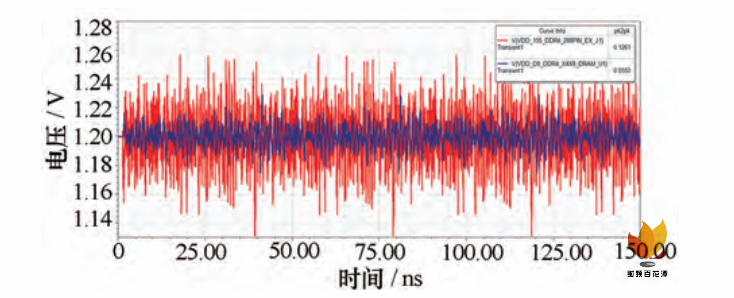

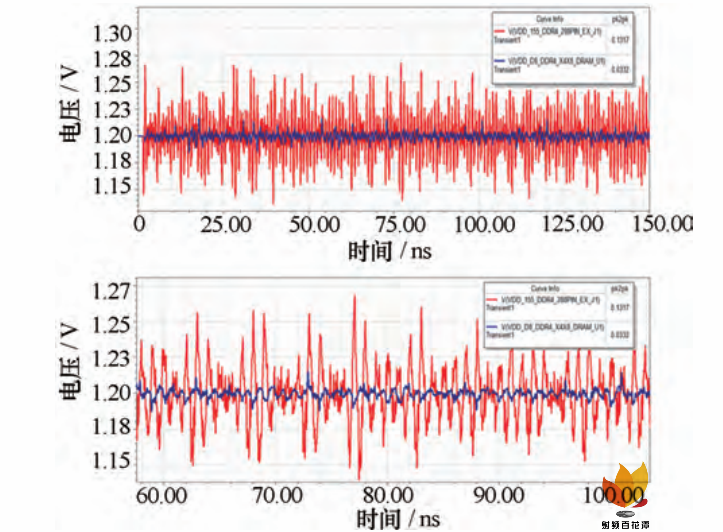

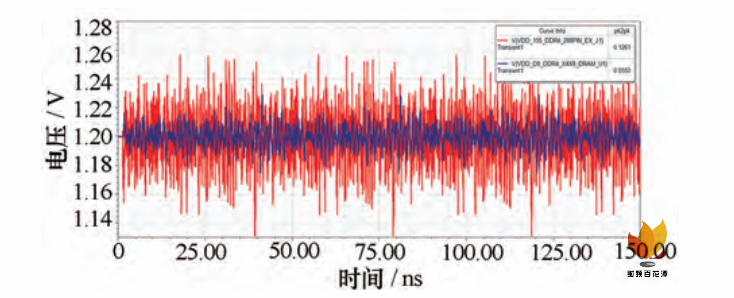

DQ数据信号和DQS差分数据信号同时传输时,信号的翻转对电源会产生噪声影响。图 6 为无去耦电容同步开关噪声仿真结果,其中红色曲线和蓝色曲线分别为发射端和接收端同步开关噪声仿真结果。

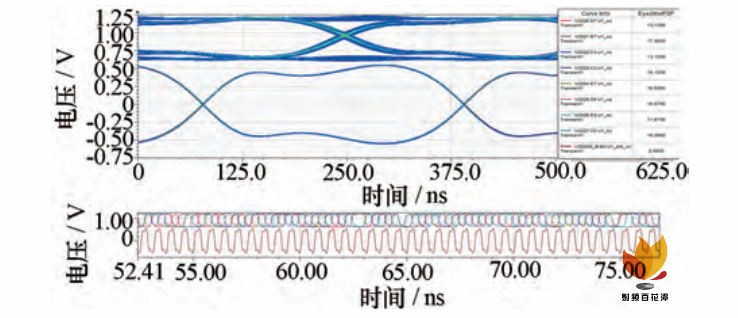

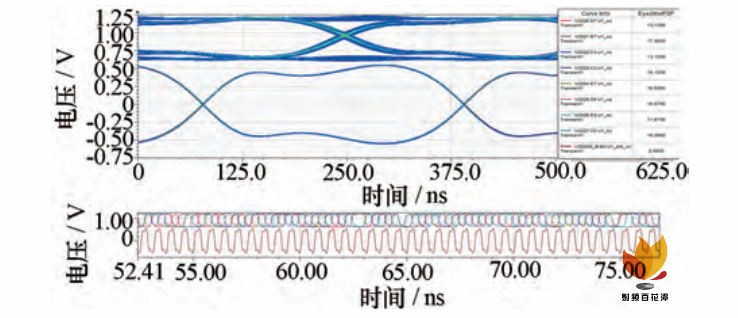

在仿真电路的电源处,加上 10nF 的去耦电容,其它设置与无去耦电容的仿真设置一样,得到接收端眼图和收发端同步开关噪声仿真结果,如图 7 和图 8 所示。对比图 5 和图 6 可以发现,加上去耦电容后,DQ和DQS信号的抖动减小了,发射接收端的同步开关噪声的影响也明显变小了。

图 7 有去耦电容接收端眼图仿真结果

图 8 有去耦电容同步开关噪声仿真结果

图 8 有去耦电容同步开关噪声仿真结果

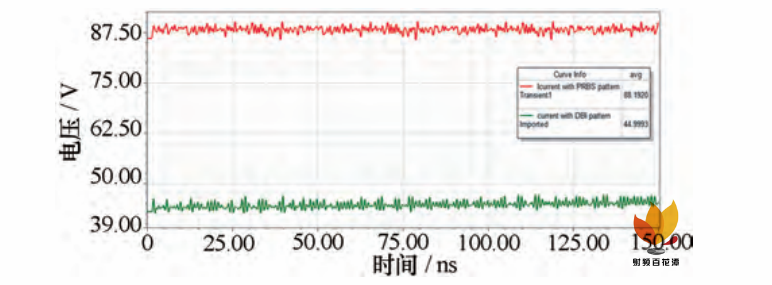

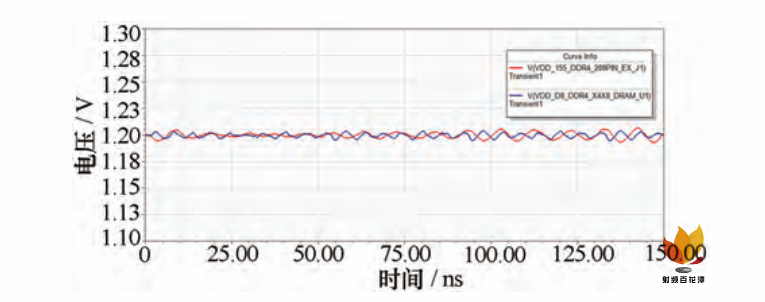

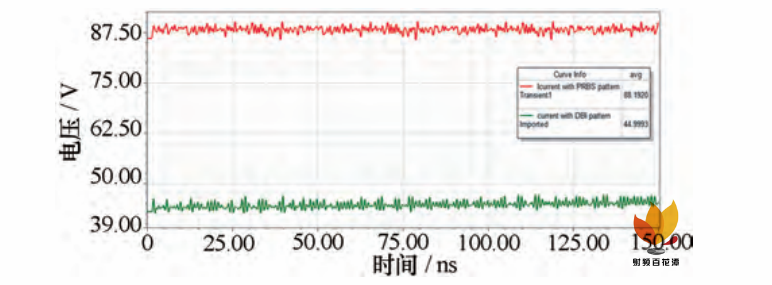

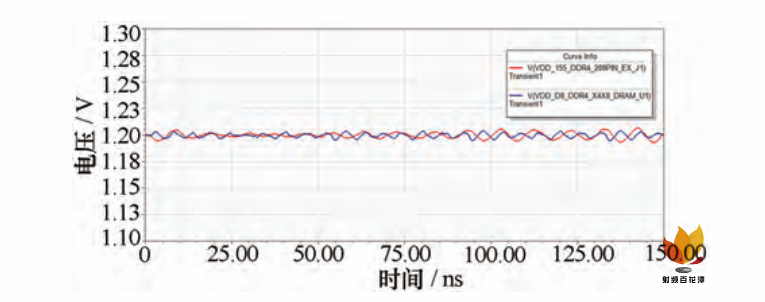

按照图 3 所示连接仿真电路图,在不加去耦电容的情况下,将 DQ 数据线输入端加的 PRBS码换成 DBI 信号后,仿真得到收发端同步开关噪声和整个器件功耗的仿真结果,如图 9 和图 10所示。从图 9 仿真结果看出在 DBI 工作方式下,发射端的同步开关噪声改善不大,接收端的同步开关噪声得到很大改善。从图 10 仿真结果看出相对于在发射端加 PRBS 码,利用器件上的 DBI 工作方式,整个器件的功耗可以降为原来的一半。

图 9 无去耦电容 DBI 模式同步开关噪声仿真结果

图 10 无去耦电容 DBI 模式功耗仿真结果

本文讨论了基于 ANSYS 软件和 IBIS 5.0 模型的 DDR4 SDRAM 信号完整性仿真方法。利用IBIS 5.0 模型中增加的复合电流、同步开关输出电流等数据,对 DDR4 SDRAM 高速电路板的信号完整性进行准确的仿真分析。高速数据信号在经过印制板走线和器件封装后,信号摆幅和眼图都有明显恶化;在仿真电路的电源处增加去耦电容后,信号抖动和发射接收端的同步开关噪声都得到明显改善;将输入激励由 PRBS 码换成 DBI信号后,信号接收端的同步开关噪声有所改善,整个器件的功耗降为原来的一半。(参考文献略)

来源:《微波学报》

本号对所有原创、转载文章的陈述与观点均保持中立,推送文章仅供读者学习和交流。文章、图片等版权归原作者享有。投稿/招聘/推广/宣传 请加微信:15989459034

图 4 无去耦电容发射端瞬态仿真波形和眼图

图 4 无去耦电容发射端瞬态仿真波形和眼图

图 8 有去耦电容同步开关噪声仿真结果

图 8 有去耦电容同步开关噪声仿真结果