BSI结构需要额外的waferbonding及thinning,背面对准处理(alignmentfor backside process)及背面界面钝化(passivation)等工艺,要求容差非常小,工艺复杂。下表是常用的两种BSI结构工艺,不论采用哪种BSI结构,都需要waferbonding工艺。

表1 BSIprocess flow

Flow | Silicon bulk BSI(三星/OV) | SOI bulk BSI(SONY) |

1. | Bulk Si substrate | SOI wafer形成 |

2. | CMOS process | CMOS process |

3. | Bonding handle wafer | Bonding handle wafer |

4. | Backside thinning&passivation | Backside thinning to BOX |

5. | PAD metal generate | PAD metal generate |

6. | ARC(抗反射涂层) | ARC |

7 | pad open | pad open |

8 | CF | CF |

9 | CP测试/Package | CP测试/Package |

以SONY为代表的SOI结构,其成本提高4~5倍,因BSI背面透光,有thinning工艺到BOXstop layer层,精确控制silicon层厚度,使得SOI结构更易构建。

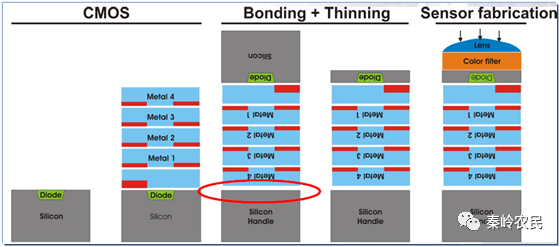

主要工艺流程:

(1)SOIwafer形成(三种process)

(2)CMOSimage process&metal

(3)Bondingto Handle wafer

(4)Backsidethinning down to the BOX to expose backside(buried oxide)

(5)Anti-reflectivecoating(ARC)

(6)Colorfilters/Micro Lens

(7)CP/Packaging(3DTSV/WLP)

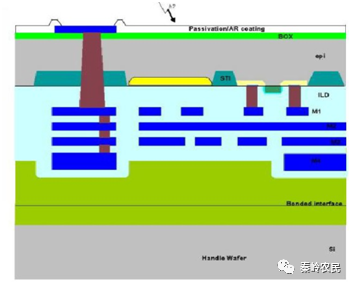

图1 SOI结构示意图

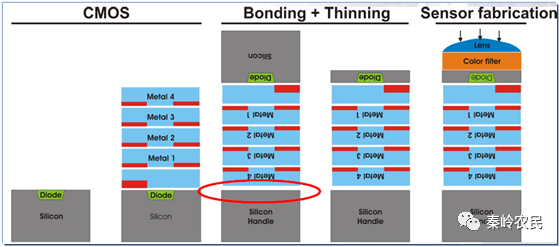

以三星/OV为代表的siliconbulk工艺,主要是为了降低材料成本。

图2silicon-bulk结构示意图

主要工艺流程:

(1)BulkSi substrate

(2)CMOSImage Process&metal

(3)Waferbonding

(4)Backside silicon thinning down

(5)Backside passivation

(6)PADopening

(7)Anti-reflectivecoating(ARC)(SIN减反射及钝化作用)

(8)Colorfilters and Micro Lens patterning

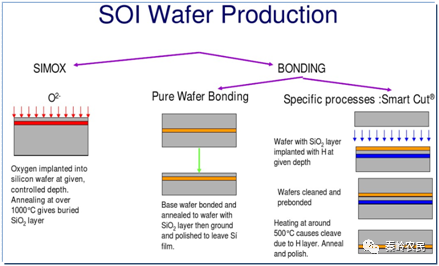

(1)注氧隔离(SIMOX:Separation byimplantation of oxygen),包括注入O,N,Co离子到单晶硅中形成oxide,SIN,CoSi2埋层,已成熟的是oxide埋层工艺,通过高剂量(1e1017~2e18 /cm2)氧离子在能量(50~200KeV)注入到衬底silicon,然后快速anneal形成4~5um BOX(Buried Oxide),top silicon层厚度约3um;SIMOX制作的SOI有较好BOX均匀性,能通过控制注入能量实现BOX上silicon厚度,但退火温度影响silicon微结构,退火温度一般不低于600℃,否则会在wafer表面形成一层非晶态硅层。另BOX太薄会导致SOI与衬底击穿短路,起不到隔离效果,需一道internal oxide(ITOX)来生长一层oxide(~1350℃),一部分氧离子会穿过silicon进入到Si/BOX界面反应生成ITOX来提高BOX厚度。

图3SOI的三种形成方法示意图

(2)Bond&EtchbackSOI(BESOI),键合法(waferbonding/mounting)(因效率低,已抛弃):将两个wafer通过氧化键合在一起,通过后续热处理减小键合应力,也叫layertransfer。

在扩散炉中,两wafer在热氧化作用下生长热氧化层,氧化发生在wafer所有面,当氧化层足够厚时两wafer就会通过oxide层bond在一起,由于oxide粗

糙度作用两wafer在室温下发生部分bond,为巩固bond键合力会在~1100℃烘烤。Bond之后会进行wafergrinding(CMP)或etching移除其中一个substrate大部分silicon厚度,仅仅只保留oxide上方很薄一层silicon。为保证减薄的均一性,需要做一层stoplayer,键合之前需对一wafer进行P型implant或Epitaxy重掺杂(>1019cm-3),then重掺杂的wafer会暴露在高选择比的蚀刻剂中去除掺杂部分wafer;这种方法可以通过掺杂深度预先确定topsilicon layer的厚度和均匀性。(重掺杂的silicon与不掺杂silicon蚀刻速率相差较大,KOH对硅的腐蚀在掺杂浓度<1e19cm-3时基本为常数,超过该浓度时,腐蚀速率与掺杂硼浓度的4次方成反比,达到一定的浓度时,腐蚀速率很小,可认为停止反应。)

由于不存在implant,对substrate损伤最小,自由电荷载流子较少,通常用来制造SOIwafer的device layer>2um器件,wafer 直径从3“(76.2mm)~8”(200mm);

(3)smartcurt法:H离子层断裂分开;可制作超薄~50nmdevice layer层。

主要工艺如下:

a:wafer表面生长oxide层,

b:wafer表面注入H离子,topsilicon厚度由注入的H+范围(5e1016cm-2能量5~70KeV),决定。

c:与BESOI方法类似,与handlewafer bonding;

d:bondingwafer经过两个温度过程形成最终的SOI衬底。(1)600℃烘烤温度下,将wafer在H注入峰值浓度处分开,(2)1100℃条件下加强bonding键合能力。

e.CMP化学机械抛光处理H分离的wafer表面粗糙度,去掉表面的残留损伤层,粗糙度规格<2A。

(4)外延层转移工艺(ELTRAN):通过在键合之前在结构中引入多孔硅来获得可控的键合wafer分裂,首先在wafer表面形成两个不同多孔率和机械特性的多孔硅层,wafer会在这两层之间裂开,氢气气氛中热处理,在单晶多孔硅上外延生长硅,且硅晶向保持不变,随后此wafer被键合到另一wafer表面,室温下利用高纯水喷射下开始裂开,且裂开的wafer可循环使用。

(5)NanoCleave:是smart-cut变体,采用注入H+形成应力层,在室温下wafer机械裂开,形成光滑硅平面,做器件之前表面不需要抛光。

Devicewafer工艺(即Pixel区域各种工艺,各层metal工艺)已完成,metal上覆盖的passivation表面进行CMP平整化,做bonding准备工作。

图4体硅工艺

Device&carrierwafer对位及粘合,如何对位?

目前主要有以下几种adhesion工艺方法:

• Direct bonding (fusion bonding)--直接键合

• Surface activated bonding--表面活化键合

• Plasma activated bonding--等离子体活化键合

• Anodic bonding--静电键合

• Eutectic bonding--共熔键合

• Glass frit bonding--玻璃粘合键合

• Adhesive bonding--粘合剂键合

• Thermo-compression bonding--热压键合

• Reactive bonding--活化键合

• Transient liquid phase diffusionbonding--瞬态液相扩散键合

其中最常用的是:Directbonding (fusion bonding),lowtemperature Plasma activated bonding(等离子体活化键合)和polymer adhesivebonding(聚合物粘合剂键合);

(1)对于lowtemperature Plasma activated bonding,wafer需要平坦化处理来满足融合键合技术,首先需要在Devicewafer利用PECVD淀积oxide,然后热退火使氧化层更加致密化,主要作用是去除PECVD生成的oxide层中残余的气体陷阱,否则残留的陷阱将会在bondinginterface聚集形成空洞,之后oxide层将使用CMP抛光,CMP之后对Devicewafer进行plasmaactivated,alignment选择edge-to-edge机械对位(max.accuracy:±50um)或光学对位(max.accuracy:<1um),主要取决于对位精度。

Devicewafer与handleWafer在室温下接触自发bonding,然后在200℃~400℃热退火处理,随后即可进行背部减薄处理。

图5Plasma-ActivatedBonding设备

wafershape、clearnlinessand smoothness挑战:平坦化<0.5nm

低温(T<400℃,t:1~3hours)低压力(易变性)

(2)PolymerAdhesive Bonding是采用polymer旋涂或喷涂工艺,优点是polymer材料可填充wafer表面gap,补偿wafer平整度,在polymer厚度范围内可兼容particle;当backside涂敷polymer时受到污染可能存在risk,polymer层收缩也可能发生对位精度的恶化,以及后续材料的可靠性问题。

Carrierwafer为本征态silicon,厚度(8寸wafer)据估计约725um,Bondinghandle wafer for mechanical support(提供几机械支撑应力);

Bonding过程中需要注意以下几个问题:

a.Bubblefree achieved:bonding过程中不能产生气泡,

b.Bubblemonitor methodology established:建立如何检测气泡的方法

c.Goodplanarization before bond:bonding 之前的平坦化处理,

d.Particlereduction&bonding interface:如何减少particle及bonding界面处理;

Devicewafer减薄,目前Device+carrier总厚度可减薄到100um,Devicewafer Grinding要求wafer表面TTV(TotalThickness Variation)小于±0.1um,wafer center均匀性较好,waferedge均匀性稍差;WTW(waferto wafer)每片grindingwafer与wafer之间的差异<±0.025um;

photo/etch各层passivation及silicon形成PAD开口;进行photo/etch形成PAD开口,depositespacer oxide用来isolationsilicon与backsidemetal;depositebackside metal W(tungsten)/Al metal,W金属用来阻挡铝扩散到oxide及silicon中,W金属可以用氟基或氯基气体蚀刻;M1~M3内部互联,再进行photo/etch工艺形成opticalblock(WOB),WOB之外应不属于光学区域,Mlensstop layer及增加CF层的粘附力(因最终pad区域的CF层需要去除);

淀积抗反射涂层:此处使用SIN材料,SIN采用PECVD,T<350℃,SIN薄膜具有优良的表面钝化效果,高效的光学减反射性能(厚度和折射率匹配),低温工艺(有效降低成本)。

在制作好的backside表面fillingscrible line/pad open windows,然后进行PL(平坦层)及pixel的R/G/B颜料层涂覆,再进行FL(平坦层)增加颜料层与ML的粘附性,最后制作ML有机层形成微透镜,在ML层上还需要淀积LTO(低温氧化层/Nanofilm),主要是起到可水洗的作用,保护lens污染等。