本文由半导体产业纵横编译自tom’shardware

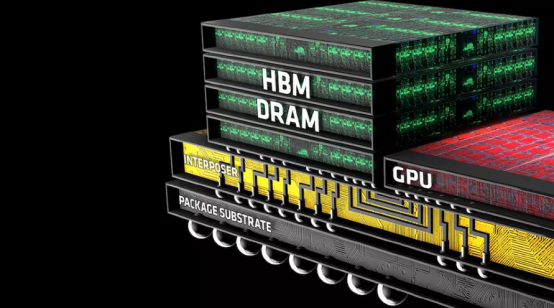

Synopsys 本周推出了其 HBM3 解决方案,该解决方案使片上系统 (SoC) 的开发人员能够为使用 5nm 制造工艺实施的 2.5D 设计添加对下一代 HBM3 内存的支持。IP 封装支持 HBM3 内存芯片,容量高达 64GB,数据传输速率高达 7200 MT/s,带宽高达 921 GB/s。

领先的内存制造商美光、三星和 SK 海力士已认可 Synopsys 业界首个完整的 HBM3 解决方案,并表示他们会致力于生产 HBM3 内存。Synopsys 的 HBM3 解决方案包括 DesignWare HBM3 控制器、物理接口 (PHY)、验证 IP 和 3DIC 编译器。

Synopsys HBM3 控制器支持多达 32 个伪通道(即 16 个物理 64 位通道或一个 1024 位接口),每个伪通道具有 16 到 64 个组以及高达 32Gb 的通道密度。更确切地说,具有 PHY 的控制器支持具有不同层数的 HBM3 内存堆栈,其容量高达 64 GB 以及具有高达 7200 MT/s 数据的 1024 位物理接口传输率。典型的 HBM 可以支持具有两个、四个或六个控制器的SoC。因此,Synopsys 的 HBM3 解决方案可为配备四个 HBM3 堆栈的 SoC 提供高达 3.68 TB/s 的内存带宽。

该控制器还支持纠错码 (ECC)、刷新管理和奇偶校验,因此可用于需要各种 RAS(可靠性、可用性、可扩展性)功能的数据中心和高性能计算 (HPC) 应用程序。

Synopsys 表示,其 HBM3 控制器和 PHY 主要基于该公司经过 5nm 硅验证的 HBM2E IP,这意味着风险降低。同时,Synopsys 的 HBM3 控制器使用经过验证的 DFI 5.0 接口连接到其 PHY,并支持广泛使用的 Arm 多端口 AMBA 4 AXI 主机接口。

为了进一步简化实施并降低风险,该公司提供了 3DIC 编译器,该编译器具有完整的 HBM3 自动布线解决方案,可实现快速而稳健的设计开发。

“Synopsys 继续满足数据密集型 SoC 的设计和验证要求,为 HBM3、DDR5 和 LPDDR5 等最先进的协议提供高质量的存储器接口 IP 和验证解决方案,”负责营销和战略的高级副总裁 John Koeter 说。“当关闭认证加速时,完整的 HBM3 IP 和验证解决方案使设计人员能够提供满足不断增长的带宽、延迟和功率要求的产品”。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。