输入:VIH>3.5V,VIL<1.5V。

可以看出TTL电平的噪声容限为0.4V,CMOS的噪声容限为1.5V。

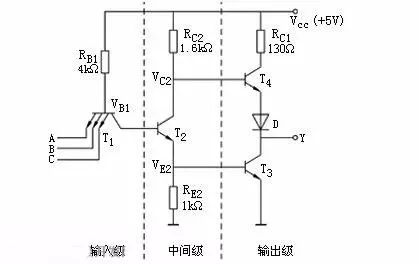

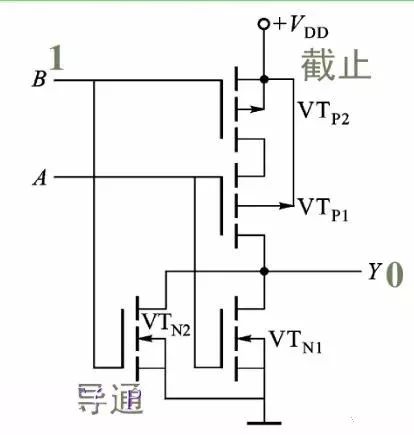

TTL和CMOS门电路结构:

如图TTL门结构,输出级采用推挽式输出结构,T4为射极跟随的形式,输出电阻小,带负载能力强。

如图CMOS门结构。

3.3V LVCMOS:Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。2.5V LVCMOS:Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。

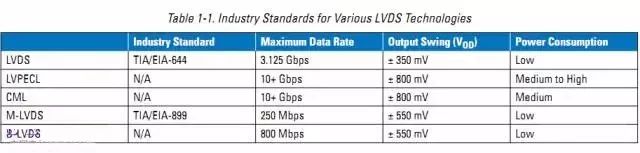

二、高速电平标准

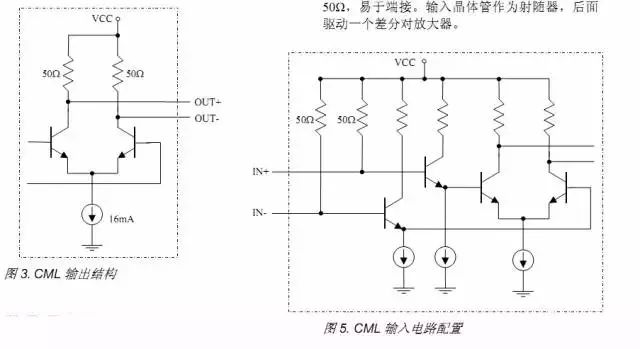

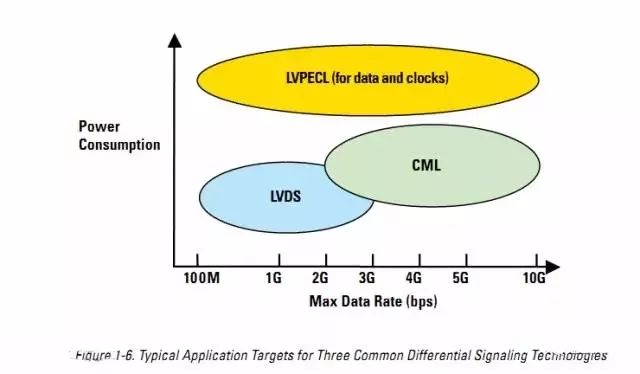

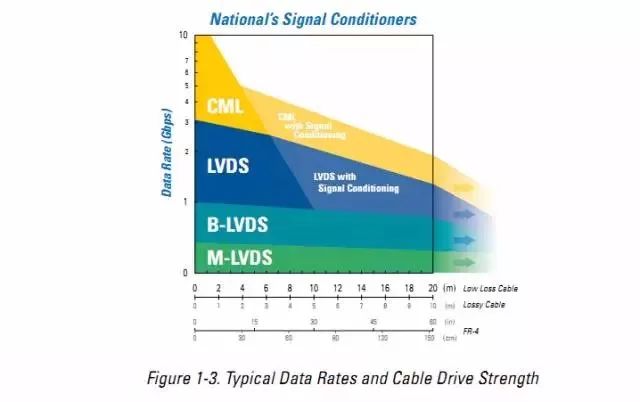

在高速电路中如何实现高速驱动输出呢?要么增大驱动电流,要么降低电平标准,或者提高晶体管工作速度。显然前者会带来非常大的功耗,因此改变电平标准和改进晶体管设计成为选择,虽然低电平更容易受到干扰,所以需要更严格的硬件设计。

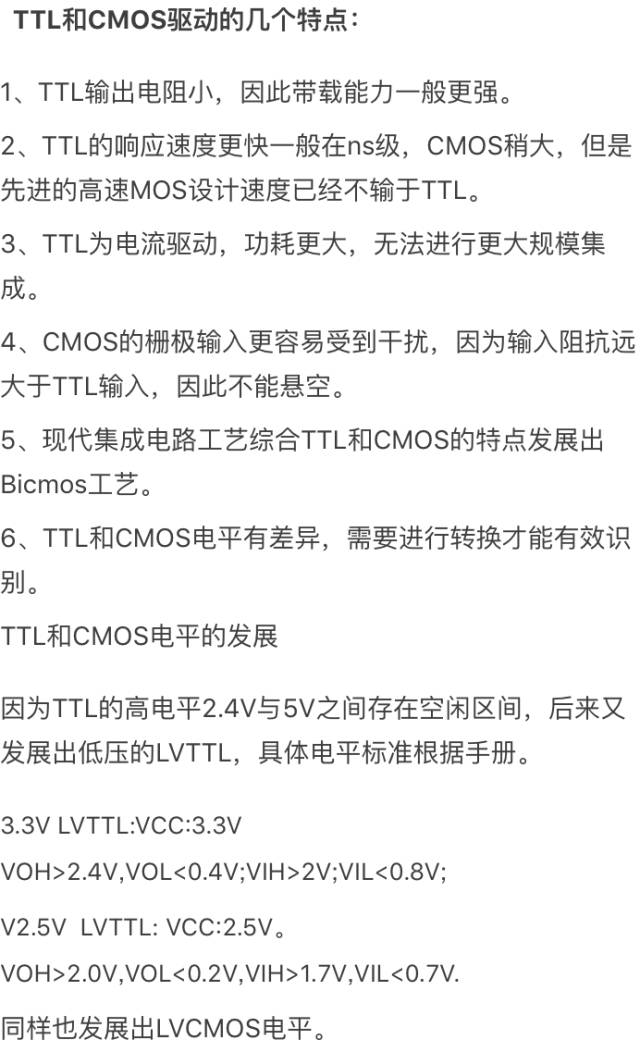

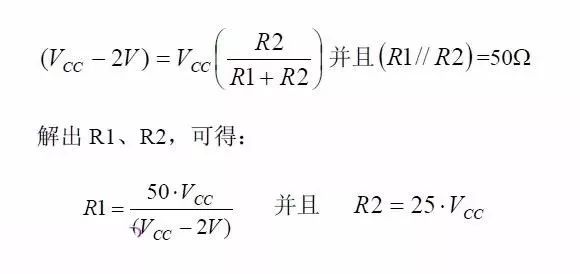

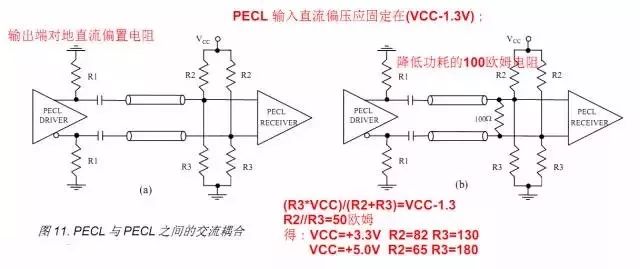

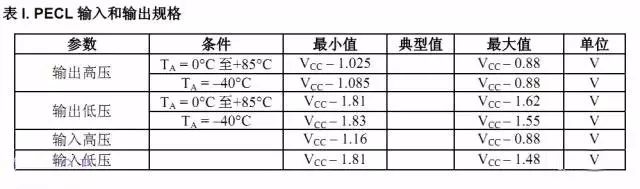

1、ECL和PECL电平接口

ECL即射极耦合逻辑(Emitter Coupled Logic)采用的是差分结构输出,并需要负电源供电。后来发展处PECL,即正电源射极耦合逻辑。基本原理就是利用晶体管工作在非饱和区来减小转换时间,大大提高转换速度。

ECL的输出管始终有电流通过,非常有利于高速转换。输出阻抗几欧姆,输出电流10mA左右,驱动能力强。

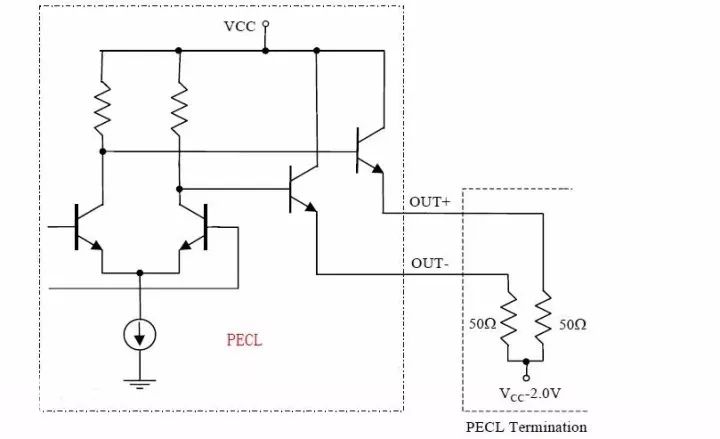

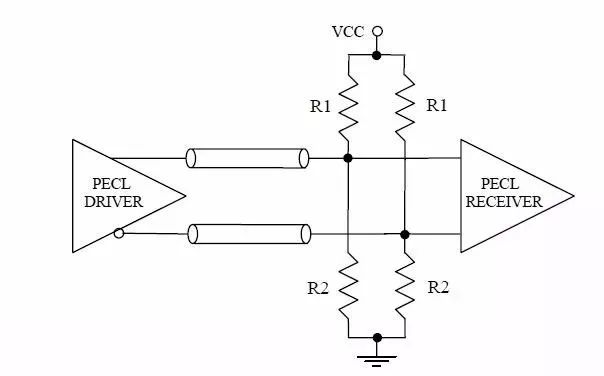

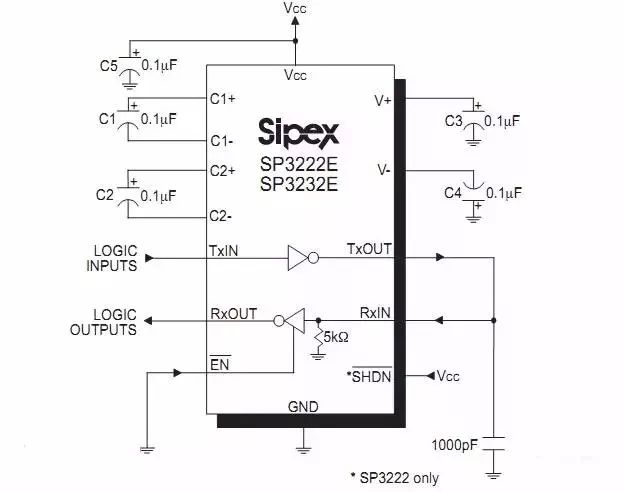

接口连接:直流耦合,适用于短距离

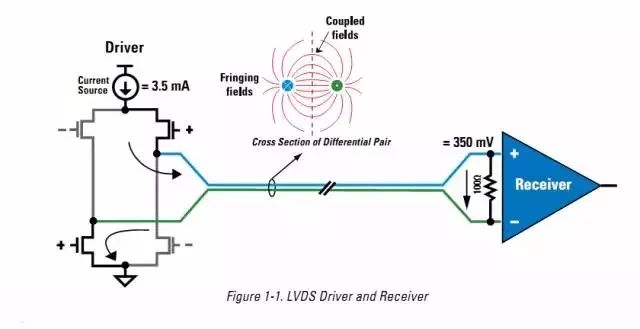

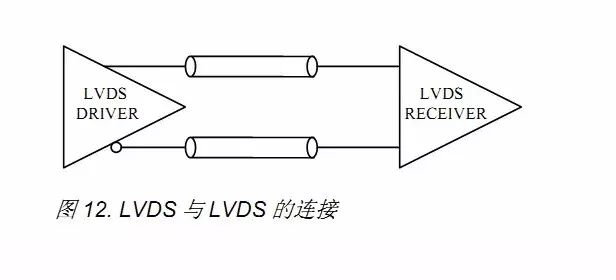

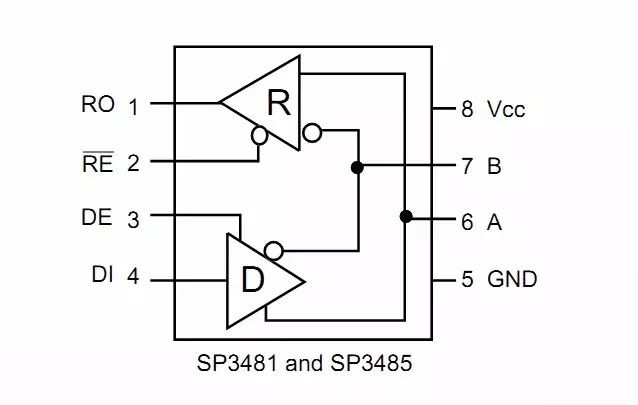

LVDS的连接方式:直接连接,因为片内具有端接电阻。

LVDS的连接方式:直接连接,因为片内具有端接电阻。

互感器、电能表接线和原理讲解!

满足你的好奇,我们把示波器拆了!

别小看这不起眼的电阻,里面有很多学问!