VPX 架构基于 VME 总线技术发展而来,是由 VITA 协会推出和维护的国际标准总线架构。从板材选型、叠层结构、关键信号线及 PCB 工艺等各方面进行分析设计,提出 VPX 机箱背板 PCB 信号完整性设计方案。

VPX 架构是目前主流的模块化、通用化、开放式机箱架构,基于 VME 总线技术发展而来,它是由VITA 协会推出和维护的国际标准总线架构。基础平台以“功能模块化、集成总线化、测试自动化”为设计理念,打造方便、易用的统一集成架构,可按需配置,堆叠扩展。背板是基础平台所有功能模块互联的基础,信号的质量对 VPX 机箱工作的稳定性具有决定性的作用,因此背板 PCB 信号完整性是基础平台设计的重点。为了解决背板的反射、串扰以及电源干扰等信号完整性问题,机箱背板在板材选型、叠层结构、关键信号线及 PCB 工艺等方面进行了精心设计,并通过信号完整性仿真及功能性能测试。

1 信号完整性设计

1.1 板材选型及叠层结构设计

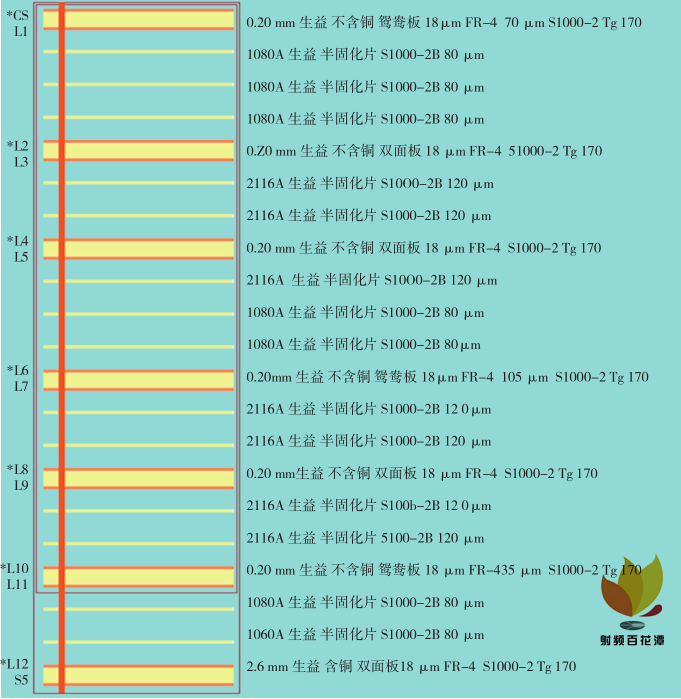

PCB 板材及叠层结构是信号完整性的一个重要要素。机箱背板采用 FR4-TG170 板材,比 FR4-TG130 具有更高的玻璃态转化温度,耐燃性更好,并通过指定供应商选取介电常数不大于 4.4 的板材,以减少串扰发生时传递的能量。背板板厚设计为 5.4 mm,在优先考虑信号走线质量的情况下综合考虑了成本及加工难易度。背板叠层采用 14 层板,叠层结构如图 1 所示。

图 1 背板叠层结构示意图

图 1 背板叠层结构示意图(1)CS。顶层,排放插座及主要器件,尽量不走关键信号线,且其余信号走线尽快入内层,保证EMC 性能。

(2)L1。地层,主要网络为 GND,为顶层及L2 层提供完整的参考平面。(3)L2。关键信号层,敏感信号和关键信号均可在这层走线。

(4)L3。地层,主要网络为 GND,为 L2 及 L4层提供完整的参考平面。

(5)L4。关键信号层,敏感信号和关键信号均可在该层走线。

(6)L5。地层,主要网络为 GND,为 L4 层提供完整的参考平面,为 L6 提供地层。

(7)L6。电源层,主要网络为 12 V 和 3.3 V 辅助电源。此层的相邻层有地层,以保证更好的电源完整性。

(8)L7。次关键信号层,由于此层其中的一个参考平面为分割了的电源层,因此此层将进行次关键信号的走线。

(9)L8。地层,主要网络为 GND,为 L7 及 L9层提供完整的参考平面。

(10)L9。关键信号层,敏感信号和关键信号均可在该层走线。

(11)L10。地层,主要网络为 GND,为 L9 及L11 层提供完整的参考平面。

(12)L11。关键信号层,敏感信号和关键信号均可在该层走线。

(13)L12。地层,主要网络为 GND,为 L11 及底层提供完整的参考平面。

(14)SS。底层,排放插座及次要器件,尽量不走关键信号线,且其余信号走线应尽快入内层,保证 EMC 性能。

通过设计以上叠层结构,机箱背板的所有信号走线都有完整的参考平面,保证了信号线的阻抗连续性,关键信号甚至有两层参考平面,使信号屏蔽性和抗干扰能力得到进一步提升;同时,不存在相邻两层间信号串扰现象,且关键信号均在内层布线,减少了远端串扰的影响;L6 电源层有相邻的L5 底层,也满足电源完整性要求。

1.2 关键信号线分类及设计

机箱背板存在 5 种总线,分别是交换总线、配置管理总线、时分总线、时统总线及友邻总线。其中,交换总线和友邻总线的接口形式相同,按相同信号特性进行设计;时分总线和时统总线的接口形式相同,按相同信号特性进行设计。通过对 3 种信号线进行分类设计,解决机箱背板各种总线的信号完整性问题。

(1)总线源端及末端就近摆放一个 100 Ω 端接电阻,以最大限度地吸收反射信号。

(2)总线的走线长度不能超过 508 mm,为芯片的驱动能力保留充足的裕量。

(3)每个过孔的出现都会使信号阻抗出现不连续的现象,因此总线在布线时打过孔尽量不要超过 2 个,减少由过孔带来的寄生电容,并在过孔附近就近打接地过孔,为交流信号提供最短的回流路径。

(4)总线需和其他网络保持 0.508 mm 以上的间距,采取 3W 原则,最大程度地减少其他信号对时分总线和时统总线的串扰。

(5)总线的走线一直伴随有完整的参考平面,保证总线信号有最短的回流路径,同时保证信号线的特征阻抗不会发生突变。

(6)差分线的特征阻抗设计为 100 Ω。

配置管理总线网络标号为 SM0、SM1、SM2及 SM3,这些信号均为单端信号,物理接口形式为I 2 C,总线速率为 400 kb·s -1 ,为了解决信号完整性问题,配置管理总线遵循如下设计原则。

(1)总线源端及末端采用就近上拉一个 4.7 K电阻的端接方式,提高总线的驱动能力并吸收一部分反射。

(2)总线的走线长度不能超过 508 mm,为芯片的驱动能力保留充足的裕量。

(3)单端信号线的特征阻抗设计为 65 Ω。

交换总线和友邻总线信号均为高速差分信号,遵循如下设计原则。

(1)差分线在布线时打过孔尽量不要超过 2个,减少由过孔带来的寄生电容,并在过孔附近就近打接地过孔,为交流信号提供最短的回流路径 .

(2)差分线需和其他网络保持 0.508 mm 以上的间距,采取 3W 原则,差分线的过孔需和其他网络的间距保持 0.305 mm 以上,最大程度地减少其他信号对总线的串扰。

(3)差分线的走线一直伴随有完整的参考平面,保证总线信号有最短的回流路径及保证信号线的特征阻抗不会发生突变;

(4)差分线对内采用严格等长的走线方式,保证差分线对内信号时序稳定。

(5)差分线的特征阻抗设计为 100 Ω。

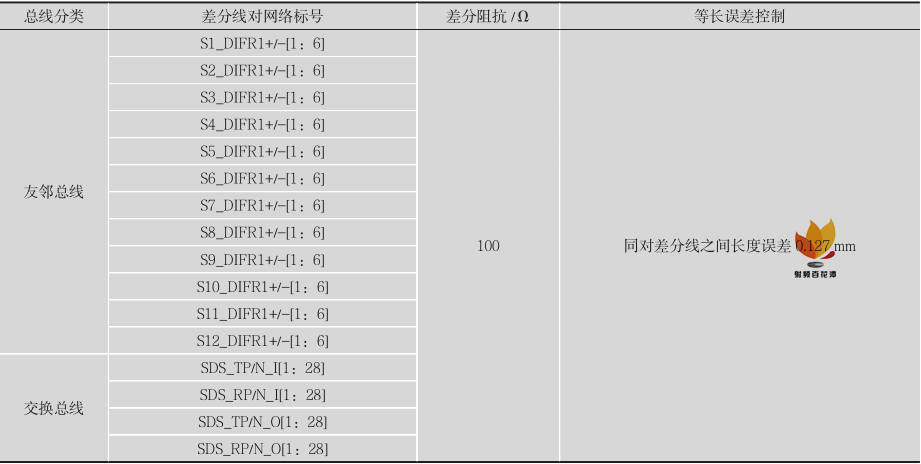

表 1 交换总线和友邻总线网络标号表

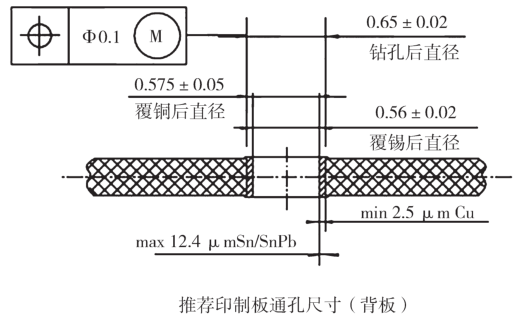

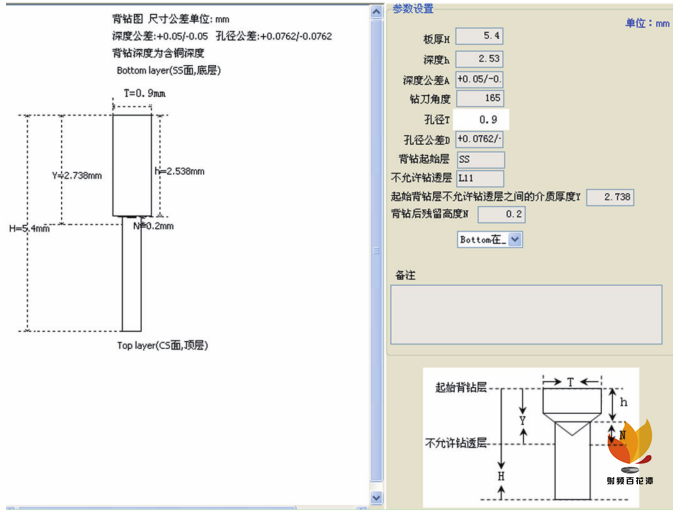

1.3 PCB 工艺设计

机箱背板采用 14 层板工艺,板厚 5.4 mm,PCB 过孔沉铜塞油,PCB 表面覆盖绿油。为了解决信号完整性问题,背板严格控制了 VPX 插座连接器的孔径公差,同时对高速差分信号采用背钻工艺来减少信号的反射。VPX 插座连接器的孔径示意如图 2 所示。

2 信号完整性仿真

2.1 时统总线和时分总线信号的仿真

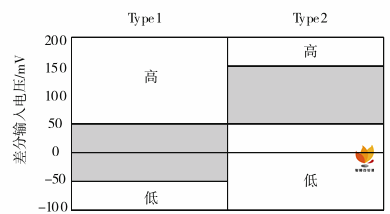

背板时统和时分信号采用 MLVD 差分信号,电气特性符合 MLVD 标准 Type1 类型接口的规定,接口输入电压阈值要求如表 2 所示。

表 2 接口输入电压阈值要求

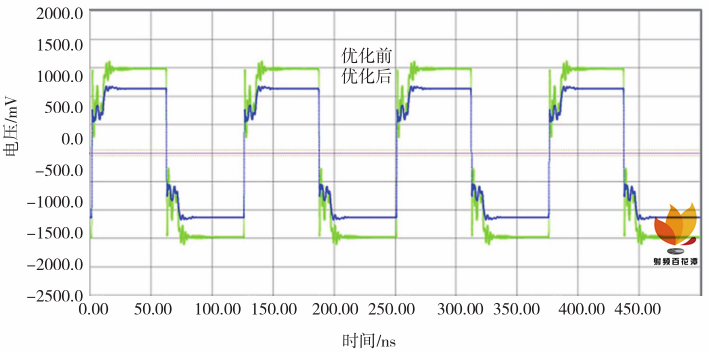

图 5 背板差分信号仿真优化结果

2.2 交换总线的仿真

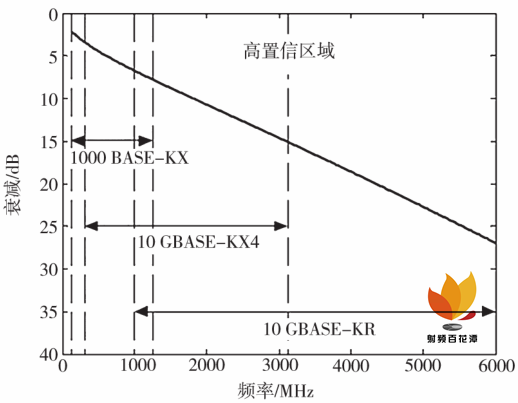

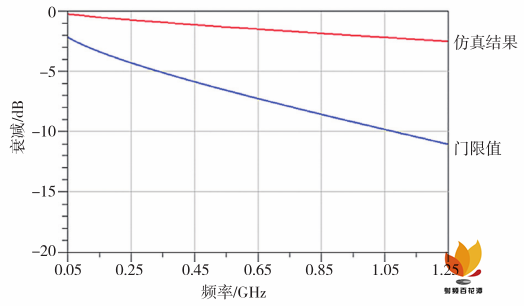

背板交换总线采用千兆以太网,符合 IEEE802.3Z 标准(1000BASE-X),信号衰减极限如图 6所示。正常的 1000BASE-X 信号衰减特性必须位于图中极限曲线的上方,离极限曲线越远,信号质量越好。

3 结 语

声明:

投稿/招聘/推广/宣传 请加微信:15989459034