来源 | 半导体封装工程师之家

智库 | 云脑智库(CloudBrain-TT)

云圈 | 进“云脑智库微信群”,请加微信:15881101905,备注研究方向

ABSTRACT

现代电子制造技术推动了微电子电路芯片尺寸减小的趋势。 由于其脆性,和封装,封装和可靠性测试而在芯片中引起的高应力可能导致芯片的有害断裂。其大直径和薄层,将难以确定硅晶片的断裂强度。因此,更适合在芯片级表征硅强度。本文讨论了一种通过简单的三点弯曲测试来表征硅芯片失效强度的方法,从而更好地理解了失效之前芯片中累积的应力。研究了芯片厚度,芯片尺寸和背面研磨方式对芯片应力的影响。

结果表明,芯片强度很大程度上取决于其几何形状和由于晶圆工艺(表面/边缘缺陷和背面研磨图案)而造成的损坏。对于进行了机械研磨的晶片,已经获得了一组取决于芯片失效的厚度的阈值应力值。确定的失效应力值对于解决在新封装和工艺开发工作中遇到的未来芯片失效问题将很有用。

INTRODUCTION

近年来,现代集成电路(IC)技术的飞速发展导致了微电子电路芯片尺寸和厚度的不断缩小。芯片尺寸的减小使得能够在晶片的单位面积上获得更多的功能芯片。芯片厚度的减少还有助于降低整体封装的高度。因此,所有这些趋势已成功地促进了更小巧,更紧凑的IC封装的生产。不可避免地,由于封装过程和可靠性测试而在芯片中引起的高应力问题开始浮出水面。在许多倒装芯片组件和多芯片封装中已观察到与芯片相关的故障。本质上是脆性材料,适度的应力水平可能导致有害的破坏,例如芯片的破裂和断裂。另外,诸如减薄和锯切的晶片处理步骤可能进一步在硅芯片中引起缺陷。

通过使晶片变薄的不同步骤,可以引入表面缺陷。通过晶圆切割,芯片中还会进一步引发边缘缺陷,例如微裂纹。当承受应力负荷时,微裂纹很可能传播并导致芯片破裂。

因此,在封装过程或可靠性测试期间通常会导致芯片破裂或断裂。例如,在模制过程中,硅模中的裂纹会以极高的模制压力或夹紧力发生。引线键合到薄叠层芯片结构上也可能导致芯片断裂。有限元建模技术可用于模拟这些过程并确定芯片中的应力累积。如果芯片应力超过某个阈值极限,则工艺参数将被认为是不合适的,需要重新优化。然而,尚未有文献证明硅芯片失效的强度(或应力)。另外,由于硅晶片的大直径和容易破裂的薄层,因此难以确定其断裂强度。因此,如果可以在芯片水平上表征硅强度或其断裂应力,则是有用的。

表征材料破坏强度的两个常见研究领域是材料强度方法和断裂力学方法。 在这两种方法中,破坏强度都取决于相关的材料特性。通过在材料强度研究中应用最大应力理论,当最大主应力超过其极限抗拉强度时,材料将失效。在断裂力学研究中,材料的破坏强度不仅取决于其材料性能(在达到材料强度的情况下为屈服强度),还取决于其缺陷尺寸。均质材料的破坏强度可以通过裂纹尖端处的应力强度因子(SIF)来表征[5]。假定材料中存在一定长度的裂纹尖端。加载后,裂纹尖端处的应力集中(或SIF)开始建立。当SIF超过材料的断裂韧性时,材料中将发生断裂。 Mercado等人[3]报道,硅的断裂韧性为25.9 MPa mm1 / 2。通过多芯片封装的有限元建模,他们发现通过使用适当的材料组降低硅芯片的SIF(低于25.9 MPa mm1 / 2),可以消除芯片开裂。在很多时候,材料强度方法是一种简单而直接的材料破坏强度分析方法,因为很难确定材料的初始缺陷尺寸。但是,硅的极限强度尚未确定。因此,本文采用材料强度方法,旨在提取芯片中经历的最大主应力以表征失效标准。

当前的论文研究了一种表征硅芯片失效强度的方法,采用一种简单的三点弯曲测试技术。这是一种用于脆性材料测试的常用方法,可以确定硅断裂的断裂载荷(F)。最终可以计算出芯片强度d(或失效前的芯片应力)。

这有助于更好地了解失效前芯片中累积的应力量,并提供了一种通过有限元分析预测IC封装中芯片故障的快速有效方法。将研究芯片厚度,芯片尺寸和背面研磨图案的变化对芯片应力的影响。虚拟晶片在当前的弯曲测试中使用,实际的晶片数量有限。

CHARACTERIZATION OF BRITTLE FAILURE STRENGTH

Brittle Failure of Silicon

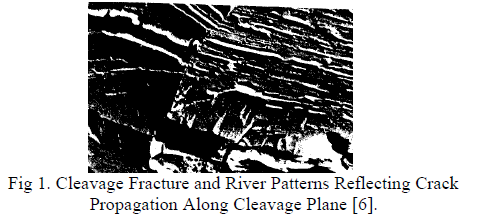

当施加的应力集中在微裂纹的尖端时,材料开始断裂。 当应力超过临界值时,在释放弹性能的地方原子键开始断裂。随着裂纹在材料中的传播,会产生一个新的表面。骨折可能是韧性的或脆性的。在延性情况下,由于沿最大剪切应力平面的边界滑动而发生大变形。在脆性情况下,原子键断裂,晶格似乎在原子尖锐的裂纹尖端后面“解开”。脆性断裂是一种快速传播,发生时没有任何明显的变形。裂纹运动的方向几乎垂直于所施加的拉应力的方向,并产生相对平坦的断裂表面。对于大多数脆性晶体材料,裂纹的扩展对应于沿特定晶体平面的原子键的连续和反复断裂。 这样的过程称为裂解。宏观上,断裂表面可以具有粒状或小平面的纹理(参见图1)

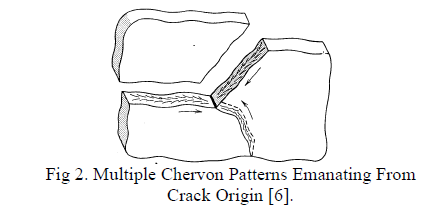

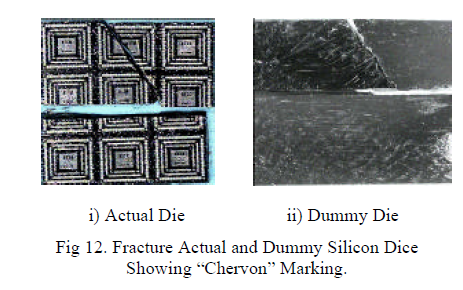

其他脆性断裂面包含称为“ V形”标记的曲线,似乎在断裂面的中间厚度附近会聚。沿着分支的Chervon标记将相对于零部件几何形状指向不同的方向。重要的是要认识到,所有不同的切尔文标记集都指向相同的相对方向-指向原点(如图2所示)。

Silicon Wafer Processing - Thinning and Dicing

在半导体晶片和集成电路的制造中,研磨是最重要的工艺之一。 来自晶圆制造厂的进料晶圆通常在700至800um的范围内。有必要将这些晶片薄到所需的厚度,以适应低封装高度轮廓。背面研磨操作通常分为两个阶段-粗磨和抛光。在大多数情况下,机械研磨技术用于减薄过程。粒度为300至600的砂轮用于将晶圆研磨至所需的厚度。通常在此研磨步骤之后会产生表面粗糙度或称为表面缺陷的缺陷。之后,将1200至2000的更细粒度用于抛光晶片背面。这种抛光将有助于减少粗磨过程中在晶片背面产生的高残留应力和表面缺陷。发现使用更细的砂粒会产生强度更高的硅片。

在薄化过程之后,为了切成小片而进行晶片锯切(或切块)。 金刚石锯通常用于切割晶圆。晶圆锯切是另一种可以将机械缺陷引入硅芯片的工艺。在刀片切割过程中,沿芯片边缘会产生诸如微裂纹的缺陷,从而导致芯片中的边缘缺陷。这些缺陷将再次构成裂纹扩展的潜在区域。最佳的工艺参数,例如刀片的暴露时间,刀片的半径和厚度以及切割速率,可以帮助减少边缘缺陷,从而减少芯片破裂的机会。可以看出,背面研磨和切割工艺不可避免地会对硅晶片造成损害。这些损坏将影响芯片的质量和强度。因此,为了最大程度地减少对硅晶片的损坏,应详细研究半导体芯片的内部质量,并应识别过程中的缺陷并将其减少到最低限度

Three-Point Bending Test Method

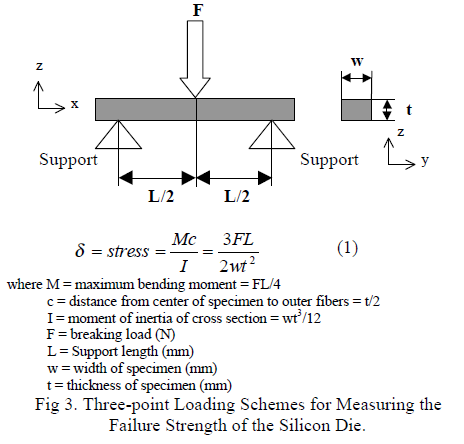

材料的破坏强度是断裂时的最大应力。 对于硅材料,通常不能通过拉伸试验来确定应力-应变行为。这是因为难以制备具有所需几何形状的试样并在不破裂的情况下将其夹紧。

因此,最常使用的是更合适的横向弯曲测试,其中使用三点加载技术将样品弯曲直至断裂。 如图3所示,对于给定的样品厚度(t)和宽度(w),以及对于样品的长度,可以根据施加到硅芯片上的断裂载荷F计算出芯片强度d(或失效前的芯片应力)。支撑跨度(L)。由于载荷的对称性,芯片中的最大主应力将沿着系统的x轴放置,该x轴等于公式(1)计算的芯片应力。在弯曲过程中,样品同时承受压缩应力和拉伸应力。其抗弯强度的大小大于抗拉断裂强度。这是因为在拉伸试验期间,样品仅承受拉伸应力,而在弯曲时,压缩应力和拉伸应力将彼此平衡,并且样品能够承受更高的应力载荷。 McLellan等人[7],Erfe [9]和Lee等人[10]已经证明了三点弯曲测试适用于硅芯片强度研究。其他测试方法包括四点弯曲,断球和振铃测试也已用于调查目的[8,11]。然而,由于这些工具的不可用,目前的工作中采用了三点弯曲测试方法。

通过三点弯曲测试,硅芯片的强度在很大程度上取决于晶圆/芯片的加工历史。首先,像光刻和蚀刻这样的晶片制造工艺将引起高应力集中的位置。晶圆厂使用的不同钝化层也可能会影响芯片的强度。

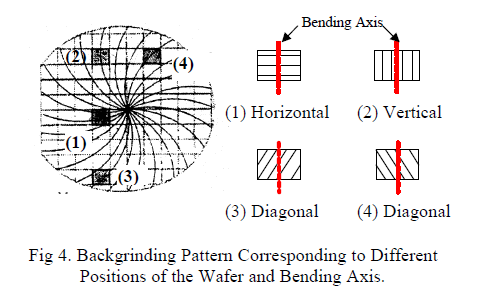

其次,机械研磨和抛光中不同的技术和工艺参数将决定残留在晶圆背面的缺陷或划痕的严重性。 另外,由于磨削而导致的各个芯片的背面上的划痕线的取向差异将导致相对于弯曲轴的芯片强度不同。如图4所示,与位于区域1中的芯片相比,从区域2中取出的芯片将承受较低的断裂载荷。其原因是任何平行于弯曲轴延伸的表面微裂纹都易于传播。而对于区域1中的背面研磨图案,划痕线垂直于弯曲轴,因此导致较高的弯曲强度。

EXPERIMENTAL BENDING TEST SETUP

收集了多个尺寸和厚度的硅芯片,用于三点弯曲测试。 对于每种配置,都使用Instron Micro-Force Tester测试了32个样本量。对于图4中描述的每个反向磨削模式,它进一步分为八个样本。为了在比较不同长度的芯片时保持一致性,在整个测试过程中使用了4mm的恒定支撑跨度。十字头运动速度(加载销)设置为0.5mm / min。在加载过程中,绘制了一个VS挠度图,并记录了芯片断裂时的最大载荷以进行分析。所有测试晶片和芯片都经过类似的机械背磨和锯切步骤,以避免由于制造工艺而导致测试结果出现差异。

RESULTS AND DISCUSSION

在材料测试中,三点弯曲法会在试样中心产生最大弯曲力矩,因此无法捕获远离芯片中心的表面或边缘缺陷。 四点弯曲测试会在加载销内的整个样本上产生均匀的力矩,从而使芯片在表面或边缘缺陷最大的点处断裂(而不必位于芯片中心)。因此,这是一种比三点弯曲更好的方法,可以捕获表面和边缘缺陷的随机分布特性。因此,从三点弯曲测试获得的芯片强度将始终高于四点弯曲测试,并且对于芯片开裂的失效标准更宽松。

Effects of Silicon Thickness on Die Strength

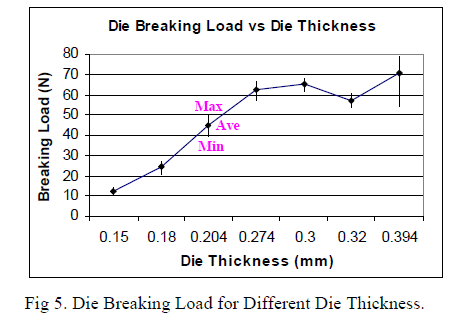

在弯曲载荷下测试了硅片的厚度范围为0.15mm至0.394mm。记录了32个样品的芯片破裂载荷,最大值,最小值和平均值如图5所示。结果通常显示芯片破裂载荷随芯片厚度的增加趋势。这是预期的,因为需要更大的负载才能导致更大体积的芯片破裂。观察到断裂载荷从芯片厚度0.3mm到0.32mm略有下降。对于0.394mm芯片厚度的测试值的标准偏差似乎要比其他更高。原因可以归因于在硅芯片中引起的表面和边缘缺陷的随机分布。受影响的样品在回磨和切割过程中可能遭受更大的损坏。尽管如此,仍注意到断裂载荷明显增加的趋势。

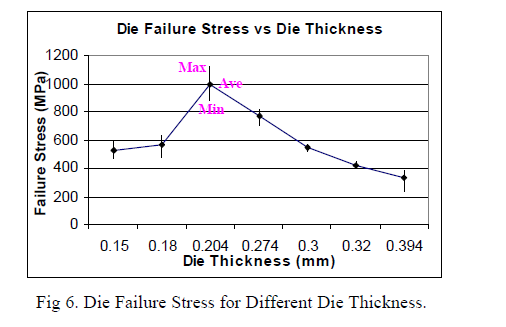

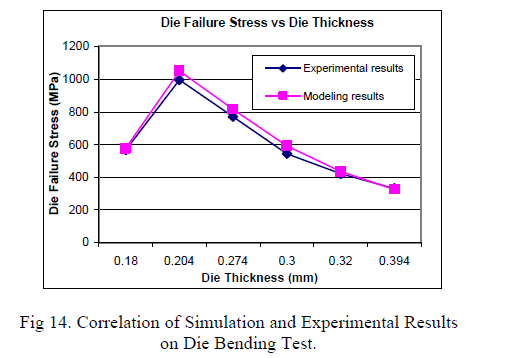

接下来,使用等式(1)计算断裂时的芯片应力(最大主应力),并获得断裂载荷。可以预料,虽然需要不同的载荷以使具有不同厚度的芯片破裂,但整个失效芯片应力应保持恒定。换句话说,所有厚度的芯片强度都应该相同。但是相反,对于不同的厚度,会捕获到不同的芯片应力。在图6中,对于0.15至0.394mm的芯片厚度,获得的失效时的芯片应力为300至1000MPa。McLellan等人[7]使用0.3mm的芯片厚度报道了大约300 MPa的破坏应力,而目前的研究结果为544 MPa。指出的差异可能是由于测试了不同类型的晶圆所致。 在McLellan等人的弯曲中使用了实际晶圆,而在当前测试中使用了虚拟晶圆。实际晶圆和虚拟晶圆之间的芯片强度比较将在后面的部分中讨论。当芯片厚度从0.394mm减小到0.204mm时,图6中的芯片破坏应力增加。当芯片厚度小于0.2mm时,存在拐点,并且芯片应力随着厚度的减小而减小。这种趋势表明,当芯片厚度变薄时,芯片强度实际上会增加,直至达到0.2mm的厚度。在较厚的芯片中,当承受弯曲载荷时,刚性更高。因此,它不能承受更高的压力并且更早失效。较薄的芯片在弯曲载荷下将具有更大的柔韧性,并且能够在失效之前吸收更高的应力。 但是,当其达到临界厚度而使芯片变得太薄(在这种情况下<0.2mm)时,则没有足够的材料来维持其柔韧性。结果,芯片不再能够承受更高的负载并开始崩塌。有了这个观察结果,就应该特别注意使用超薄芯片的超薄封装轮廓的解决方案。在工艺封装和处理超薄晶圆/骰子时,应采取更加谨慎的措施。

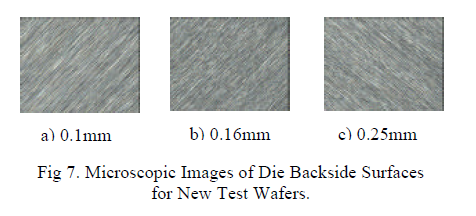

在另一种情况下,芯片强度可能受到背面研磨后引起的表面缺陷严重性的影响。较粗糙的芯片表面(具有更大和更多的缺陷)将更易于断裂破坏,因此会降低芯片强度。 因此,图6中观察到的趋势可能是由于表面粗糙度的严重程度的变化,而不是几何效应所致。诸如AFM(原子力显微镜)之类的计量技术可用于测量背面研磨晶片的表面粗糙度,从而有助于监视并将表面缺陷降至最低。不幸的是,不能对所有完成的测试零件进行表面分析。一组厚度在0.1mm至0.3mm范围内的测试晶片将进行弯曲测试。使用光学显微镜(由于AFM设备不可用)进行表面分析,其表面纹理如图7所示。发现在所有不同的芯片厚度上都观察到了类似的粗糙纹理。芯片破坏强度将在稍后阶段报告,并且芯片强度与厚度的趋势有待进一步分析。

Effects of Silicon Size on Die Strength

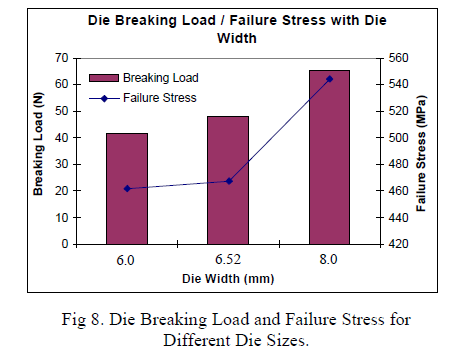

接下来评估芯片尺寸对其破坏强度的影响。由于所有测试的支撑跨度均固定为4mm,因此样品的长度不会对测试结果产生任何影响。在此分析中,研究了厚度恒定但宽度不同的芯片。从芯片厚度为0.3mm,宽度为6、6.52和8mm的样品中提取结果。图8示出了芯片断裂载荷和强度的响应。载荷和应力值都随芯片厚度的增加而增加。随着试样宽度的增加,在使整个芯片失效之前,试样中的任何裂纹都需要通过更长的晶界传播。因此,需要较大的力才能使较大的试样断裂,而这反过来又有助于提高芯片强度。

Comparison Between Wafer Types

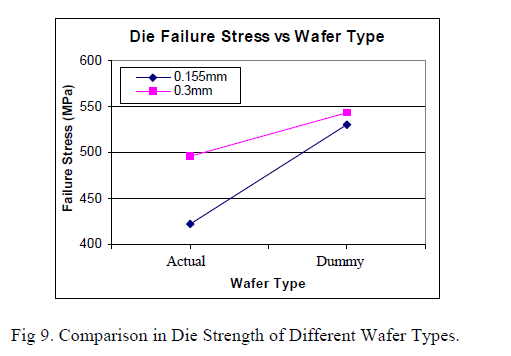

众所周知,实际功能晶圆的成本很高,因此通常将虚拟晶圆(也称为镜面晶圆)用于工艺参数优化和DOE(实验设计)研究。因此,重要的是要知道晶片类型之间的强度差异,以及要根据实际晶片调整或修改(如有必要)基于虚拟晶片而获得的任何优化参数。可以理解,在虚拟晶片和实际晶片之间的处理步骤中存在一些差异。尽管两种晶片类型都将在同一工厂中进行类似的背面研磨和切割工艺,但实际的晶片在背面研磨之前已经经历了额外的制造过程(例如光刻和图案化)。测试了两组虚拟晶片和实际晶片以进行比较,两种晶片厚度分别为0.155和0.3mm。已发现,虚设芯片的强度高于实际芯片(参见图9)。实际晶片所经历的晶片制造过程确实已经引起了晶片的进一步损坏。在较早的部分中已经很好地观察到了这种趋势,在该部分中,McLellan等人测试的实际晶圆的断裂应力低于当前工作中测试的虚拟晶圆。

Effects of Backgrinding Pattern on Die Strength

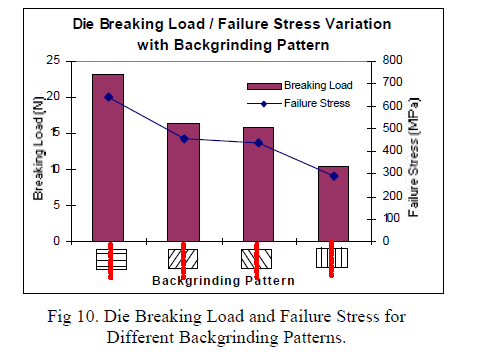

为了分析背面研磨图案对芯片强度的影响,根据背面研磨图案分离出一组芯片厚度为0.16mm的测试数据,并绘制在图10中。发现磨削图案垂直于弯曲方向 轴已产生最大的断裂载荷和破坏强度。通过在平行于弯曲轴的方向上使用磨削图案进行切块,可获得最低的芯片强度,而对角磨削图案则在两者之间产生了强度。前面已经解释了其原因,即平行于弯曲轴延伸的表面微裂纹可能更容易传播。早期的研究工作也观察到了类似的趋势。

Macroscopic Analysis

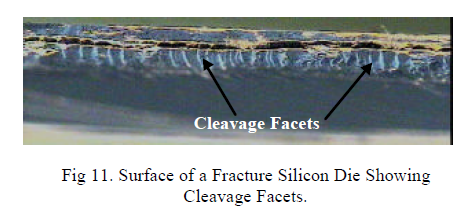

为了帮助进行测试后的故障分析,在弯曲测试后收集了硅片的断裂部分。 图11用光学显微镜放大了5倍示出了断裂硅裸片的表面。可以观察到,硅芯片处于脆性断裂状态,其表面清楚地显示出劈开面(“河纹”)纹理。

图12分别示出了实际芯片和伪芯片的脆性断裂。它包含称为“人字形”标记的曲线。所有的“ chervon”标记都指向相同的相对方向-朝原点返回,显示出由于表面缺陷而导致的芯片缺陷的优势。 Yeung等人[12]报道,通常由机械研磨造成的表面更严重损坏的背面研磨芯片往往会破碎成几片,强度较低。而从湿法化学蚀刻获得的具有更光滑表面的骰子将由于破裂扩展开始时释放的巨大弹性能量而破碎成碎片状。因此,观察结果表明,由于机械研磨,大多数被测试的晶片都存在较大的表面粗糙度。可以将湿法蚀刻化学工艺引入到背面研磨工艺中,以减少硅晶片的表面粗糙度,从而有助于提高芯片强度。

Finite Element Modeling

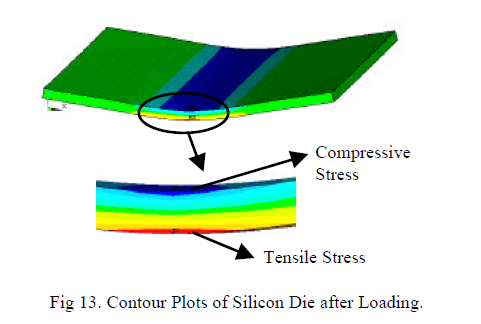

使用从梁弯曲理论推导的方程式1来计算破坏时的芯片应力。创建了硅芯片的三维(3D)有限元模型,以模拟弯曲测试,以检查所获得的芯片应力值的有效性。 ANSYS 7.0用于使用表示问题几何的元素类型45(线性元素)进行分析。在模型中规定了从实验结果中获取的平均断裂载荷,以模拟载荷条件。

加载结束时的芯片应力轮廓如图13所示。硅芯片向下弯曲,其最大拉伸应力位于芯片底部,而压缩应力位于上表面。将模拟结果中的拉伸应力值(最大主应力)与之前报道的实验测量值进行了比较。如图14所示,模拟结果与实验数据非常吻合,变化小于6%。它的确表明,可以使用梁弯曲方程来计算芯片弯曲应力,并且有限元建模技术可以准确地捕获在不同厚度下芯片中累积的应力。因此,可以建立使用元素类型45的强大仿真模型,以用于将来的模头应力计算和预测

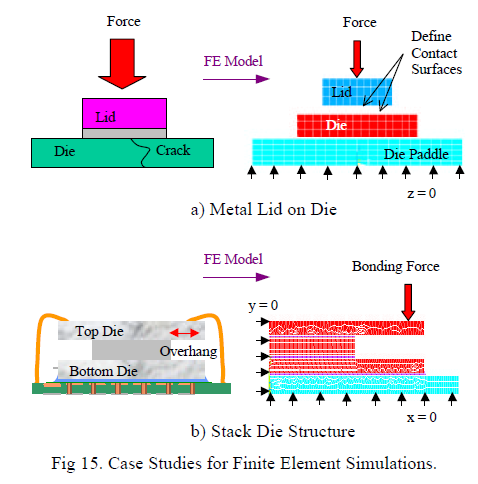

为了协助检查有限元建模是否适合解决IC封装相关问题,进行了两个案例研究。在采用四方扁平无铅(QFN)封装的第一种情况下,应将金属盖连接到硅芯片上,以改善散热效果(见图15a)。在较高的成型压力和夹紧力的情况下,减小盖表面积将对芯片施加较大的压力。芯片厚度为0.25mm时,在带有小盖的封装中发现了芯片裂纹。如图14所示的芯片破坏应力大约等于900MPa。有限元建模是基于实际的装载条件,使用较小和建议的(较大)盖尺寸进行的。当盖子尺寸增大时,模头应力从最高1140MPa降低到最低440MPa。因此,在QFN设计中实现了更大的盖子,从而解决了芯片开裂问题。在第二个示例中,将引线键合到薄堆栈芯片结构上(图15b)可能会导致顶部芯片断裂。顶部芯片悬垂处的引线键合复制了悬臂负载,其中在枢轴点将承受高应力。有限元建模是在最坏的情况下执行的,即具有长悬伸的薄芯片。发现产生的最大应力远低于实际的模头破裂应力。因此,在上模中没有遇到断裂。以上两种情况显示了有限元模拟与试验性芯片失效强度的结合,以抑制装配过程中可能的芯片断裂。

基于材料强度方法,可以在有限元分析中将硅芯片建模为块状材料。可以轻松提取最大主应力,从而提供了一种快速而有效的方法来评估IC封装中的芯片故障。相反,对于断裂力学,必须预先确定缺陷尺寸以进行失效分析,并且必须创建与网格尺寸有关的裂纹尖端模型。几乎不可能测量每个测试裸片以及安装在IC封装中的裸片的缺陷长度。因此,建议将材料强度方法用于芯片失效指示的第一遍,并在必要时使用断裂力学技术进行详细的裂纹分析。

CONCLUSIONS

已经研究了使用简单的三点弯曲测试表征硅晶片的破坏强度的方法。弯曲试验期间失效之前芯片中的最大主应力被记录为失效强度。 研究表明,芯片强度在很大程度上取决于其几何形状(厚度和尺寸)以及晶片工艺造成的损坏(表面/边缘缺陷和背面研磨图案)。使用各种背面研磨方法(例如机械研磨和湿蚀刻)将导致不同程度的表面粗糙度。宏观研究表明,表面损伤对芯片强度的影响不容忽视。对于已经进行了机械研磨的晶片,已经获得了一组取决于芯片失效的厚度的阈值应力值。但是,到目前为止的收集数据无法说明所有厚度(特别是超薄晶圆)的芯片强度。另外,利用三点弯曲测试产生了不太严格的失效标准。因此,将继续收集全面的故障数据。最后,进行了案例研究,以证明有限元模拟与实验失效强度的结合,可以解决封装和工艺开发工作中遇到的芯片失效问题。

- The End -

声明:欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为云脑智库。本公众号目前所载内容为本公众号原创、网络转载或根据非密公开性信息资料编辑整理,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系。我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。本公众号拥有对此声明的最终解释权。

投稿/招聘/推广/合作/入群/赞助 请加微信:15881101905,备注关键词

微群关键词:天线、射频微波、雷达通信电子战、芯片半导体、信号处理、软件无线电、测试制造、相控阵、EDA仿真、通导遥、学术前沿、知识服务、合作投资.

“阅读是一种习惯,分享是一种美德,我们是一群专业、有态度的知识传播者.”

↓↓↓ 戳“阅读原文”,加入“知识星球”,发现更多精彩内容.

/// 先别走,安排点个“赞”和“在看” 吧!↓↓↓