点击上方

蓝字

关注我们

制造一个最高水平的集成电路需要大量资源。水、能源、化学品、气体和硅晶圆只是制作一个芯片所需的几个关键要素。IC Knowledge LLC的Scotten W. Jones表示,依公司而定,5纳米涉及600至800个工序(不含检测和计量阶段)。随着半导体行业继续向2纳米甚至更小制程发展,工序步骤将更多。因此,生产工序的增加,势必导致生产芯片所需的资源水平(尤其是电力和水)也会持续增加。半导体行业如何在满足全球集成电路需求的同时,提高半导体晶圆厂的可持续发展呢?

光刻技术的挑战

随着半导体行业正进展到5纳米,先进的光刻步骤已从使用多重图形步骤,以及大量的蚀刻和沉积步骤的193i,转向使用极紫外光(EUV)光刻,它减少了制造晶圆所需的光刻、沉积和蚀刻步骤。Gartner研究机构副总裁Sam Wang指出,台积电在7纳米DUV工艺中使用了87个掩膜层。7纳米EUV工艺则使用了79个掩膜层,其中4个使用EUV, 5纳米工艺使用了81个掩膜层,其中14个是使用EUV。

从可持续发展的角度来看,减少掩膜步骤是件好事,因为它也减少了与多重图形有关的蚀刻、沉积和清洁步骤。然而,坏消息是EUV光刻技术比193i光刻技术加工的能源密集度更高,即使193i的工序甚至更多。

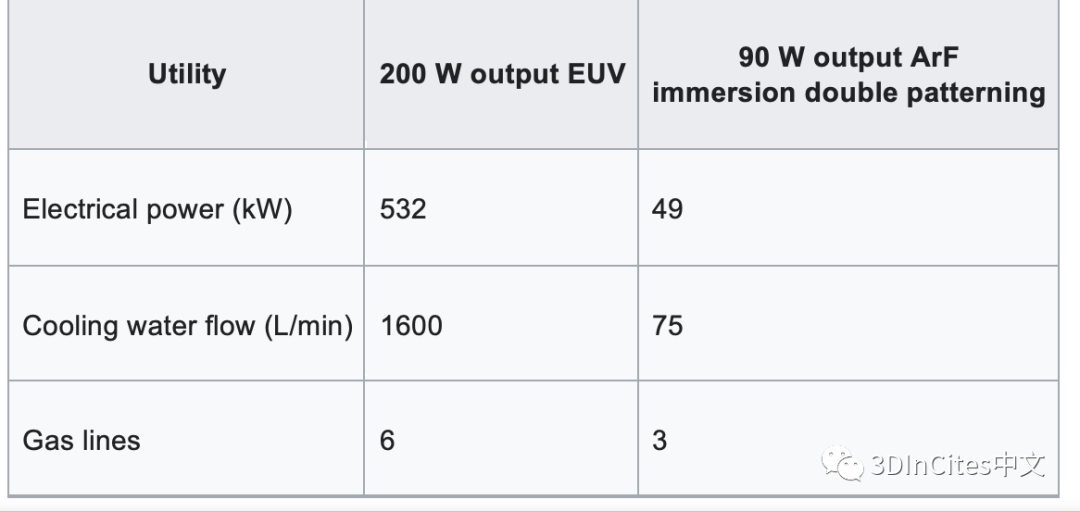

图1显示了2008年在日本举行的Sematech研讨会上提出的信息,证明了EUV比起DUV光刻使用了多10倍的电能。Andres Thoss撰写的Laser Focus World帖子中的最新数据表明,每个EUV系统使用的电能为兆瓦(MW)。据一家中国台湾媒体的报道显示,台积电有30台EUV设备,估计每天会消耗90万千瓦的电能。此外,这可能是台积电在海外寻找建造新工厂的原因之一,因为中国台湾的能源基础设施可能难以支持扩大EUV生产所需的能源量,尤其是台积电的可持续发展目标。

即使减少了工序,EUV和DUV工艺之间也不可能达到功率平价。然而,如果没有EUV技术,则无法制造7纳米及更小的晶体管;因此,工艺工程师需要从其他方面考虑可持续发展。

图 1:资源要求。(来源:Gigaphoton和Sematech Symposium Japan)

热预算

半导体晶圆厂的另一个更具可持续发展的因素是减少先进集成电路工艺流程中的热预算。经过长时间发展,工艺和设备已从批量设备发展到单晶圆或批量系统。CVD、外延和氧化扩散,所有之前在炉管或钟罩中进行的高温工艺,在许多情况下已经过渡到单晶圆设备。

依工艺而定,不管使用恒定温度基板,或使用可以快速加热和冷却的灯系统。新前驱体使沉积温度降低,而ALD的使用甚至可以进一步降低沉积温度。

氧化扩散炉已经过渡到单晶圆系统,除非炉管的拥有成本超过了单晶片的优势。在许多情况下,扩散过程已经从使用热源快速加热晶圆转向使用激光只加热上层,从而不会对已经退火的掺杂层产生影响,并可能减少加热每个晶圆所需的能量。

这几年来单晶圆设备的优点获得高度评价,其晶圆温度均匀性更好,气体分布更均匀,通常比批量系统能提供更好的均匀性。潜在缺点是,必须有更多的设备来提供与批量系统相同数量的晶圆,这可能消耗更多的能源。此外,在某些情况下,每个节点增加的步骤将需要每个晶圆厂增加额外设备,这也增加了能源预算。

更可持续发展的配套厂房

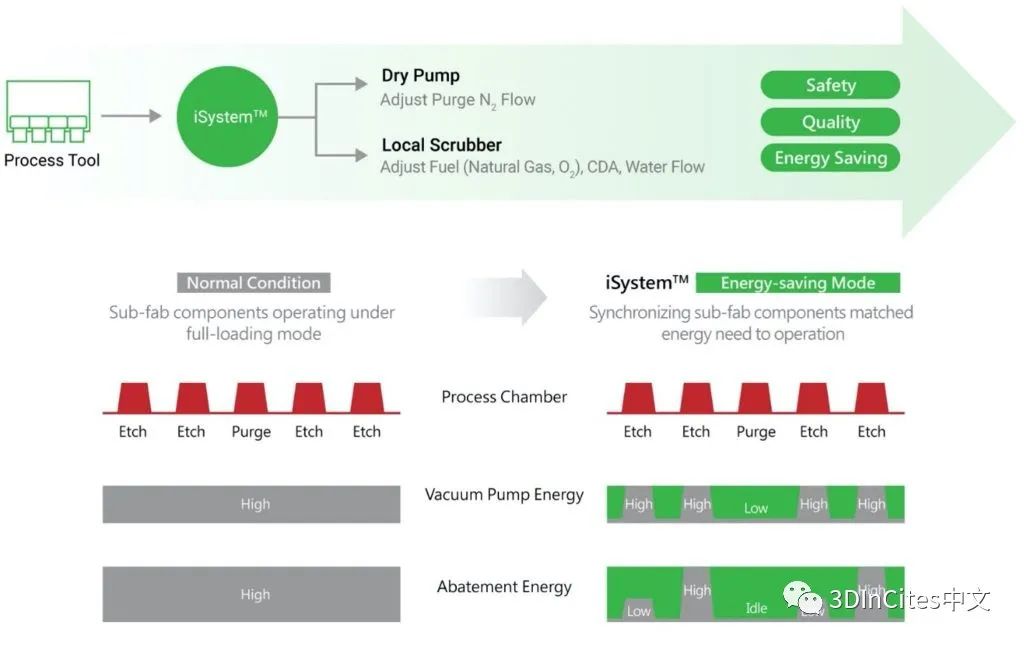

应用材料公司(AMAT)的Jim L'Heureux、Andreas Neuber博士的一篇最新博客描述了一个软件框架和控制器网络,收集来自设备和附属厂房区设备的数据,从而可以对操作和能源使用做出智慧决策。这个设备可以连接到附属厂房区的四套设备上。在这个示例中,他们演示了如何将其连接到真空泵和一个减排系统上,这是晶圆厂中典型的CVD和蚀刻设备。

一般情况下,当晶圆厂设备闲置时,子系统以全功率运行。AMAT的设备允许附属厂房设备与晶圆厂设备的工艺流程匹配。台积电正在使用它作为其可持续发展努力的一环。图2显示了台积电设置该设备以监测使用点的子系统设备的方式。

图 2:iSystem™、物联网和智能节能系统的运行机制(来源:台积电。)

根据AMAT博客,迄今为止,这一系统每年为台积电节省1340万千瓦时的电力,同时减少13,800吨的碳排放。台积电正在整个晶圆厂实施iSystem,作为其可持续发展计划的一环。一旦完全实施iSystem,每个晶圆厂能节省多少能源,以及对碳足迹的影响是什么令人好奇。

以上只是一个起点,但在减少晶圆厂的可持续发展足迹方面仍需加倍努力。

扫描二维码获取

更多精彩

3DInCites中文