这是来自Hackaday.io上的一个项目,作者为一位电子工程专业的毕业生,花了三年的时间制作的一款示波器,一个基于PC连接的低成本(500美元以内)4通道100MHz的示波器,他的目标是将高速ADC采集到的样点一个不漏地实时传送给PC,所有的数据处理都由PC来做,只要你的PC内存足够大。

要阅读英文的原文可以点击左下角的“阅读原文”。在这里我简单介绍一下该项目的要点:

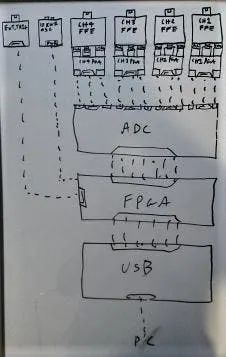

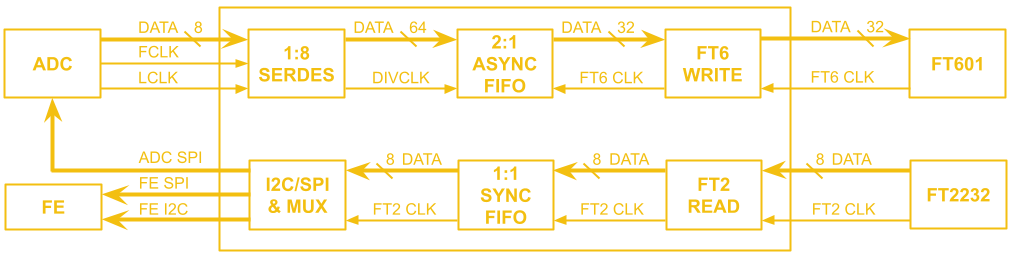

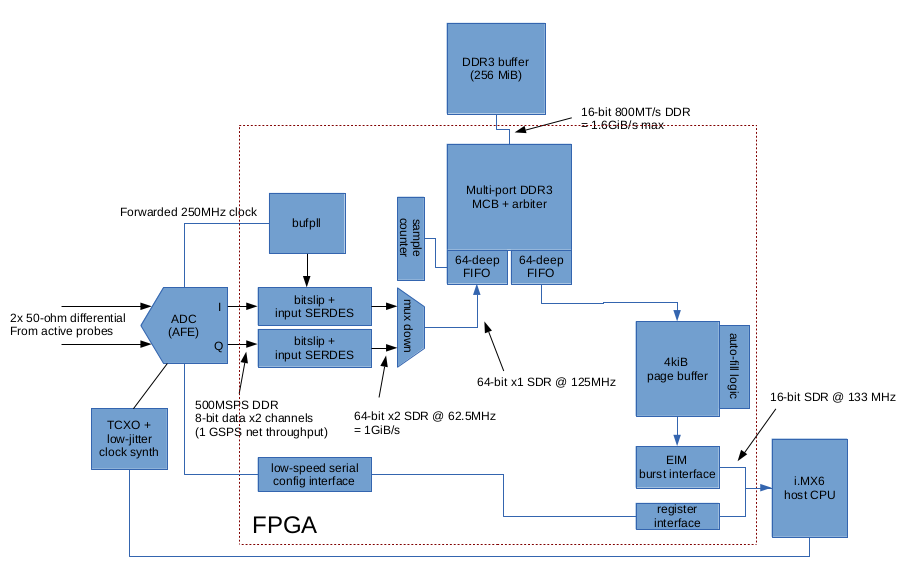

系统框图

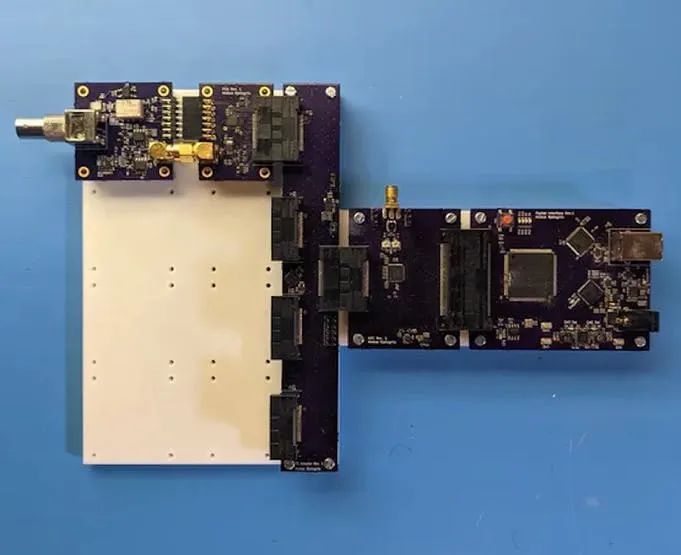

系统实物构成

作者参考了Novena的模块化的示波器设计方式

Aleksa在Hackaday.io上连续8篇博文讲述他制作这款软件定义示波器遇到的一些问题以及解决的过程。

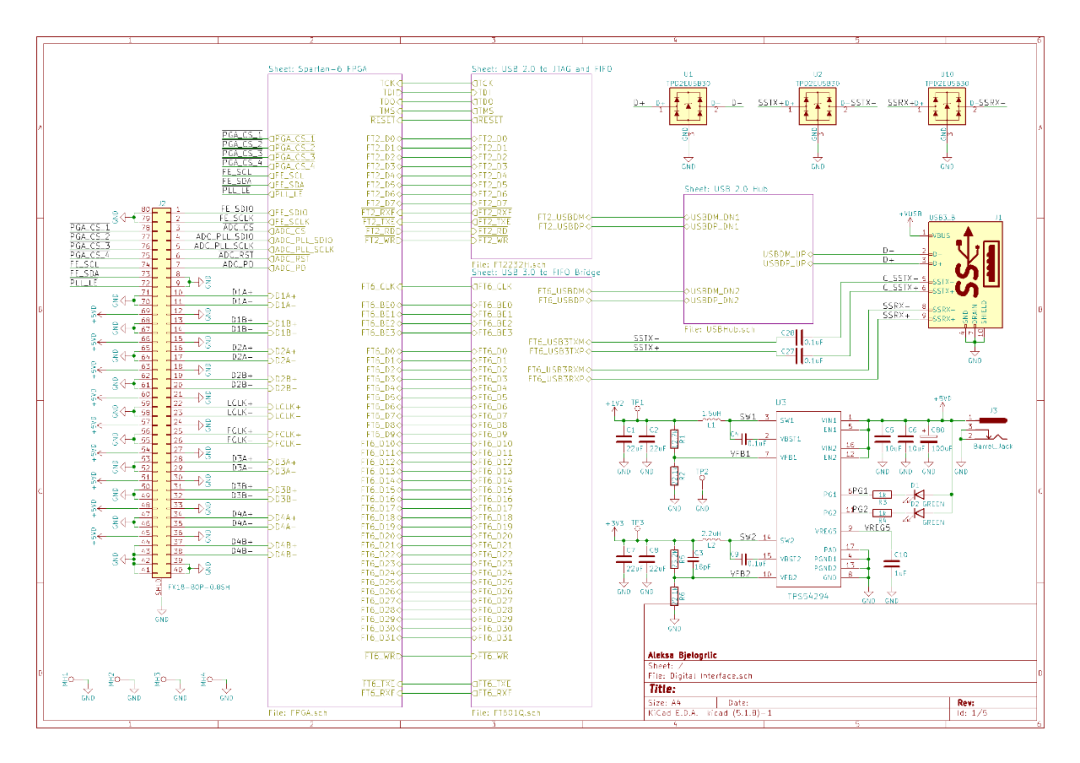

数字接口部分采用了Xilinx的Spartan 6 LX4 FPGA,能够处理来自高速ADC的1Gbps LVDS的输入,并且是TQFP封装;USB部分采用了FT601,QFN封装

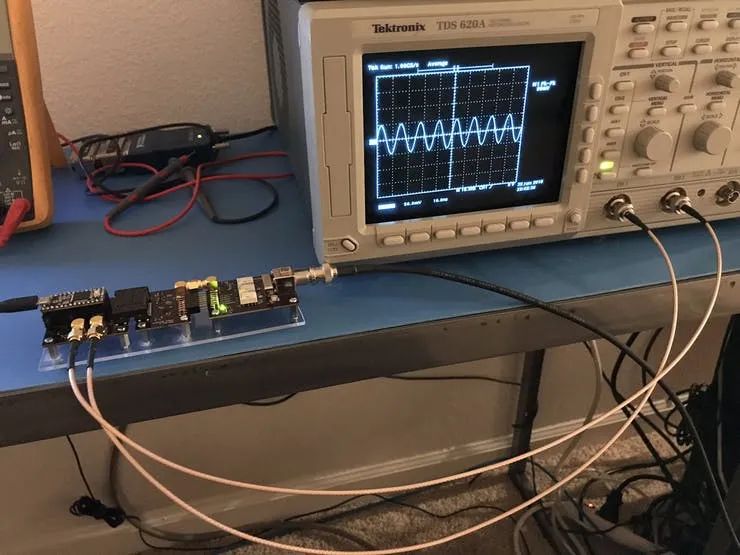

用KiCad绘制的PCB,这是数字接口部分。

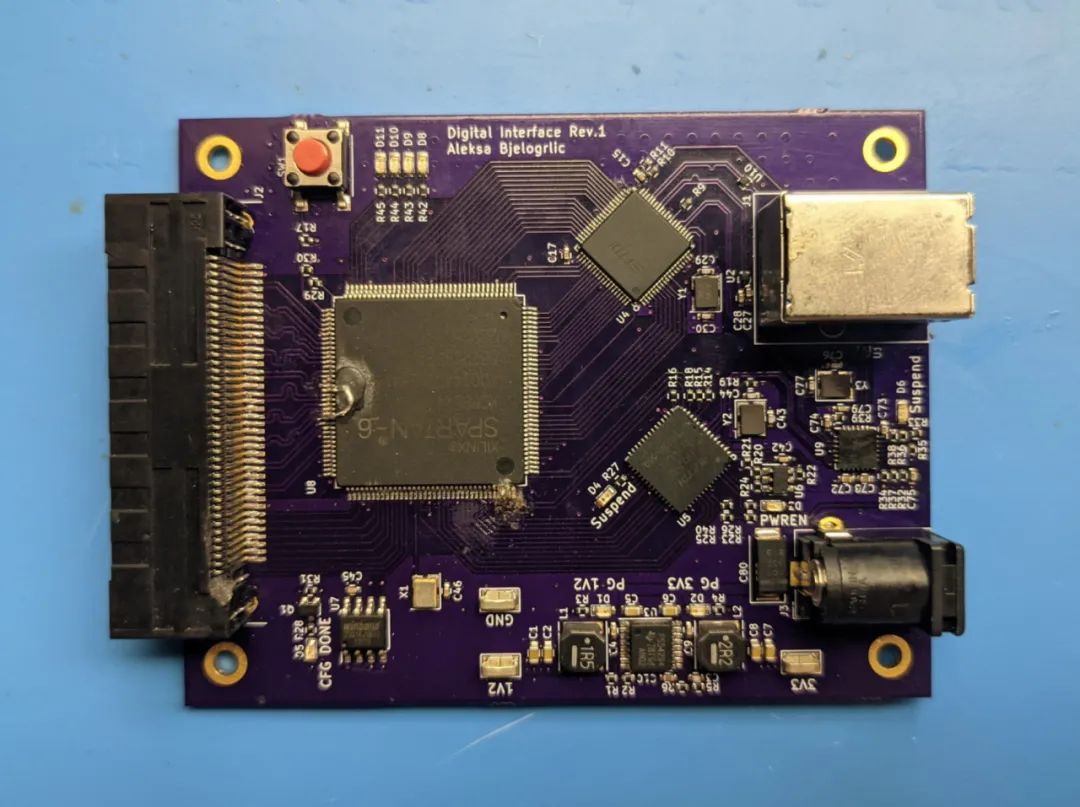

数字接口部分的板子实物照片

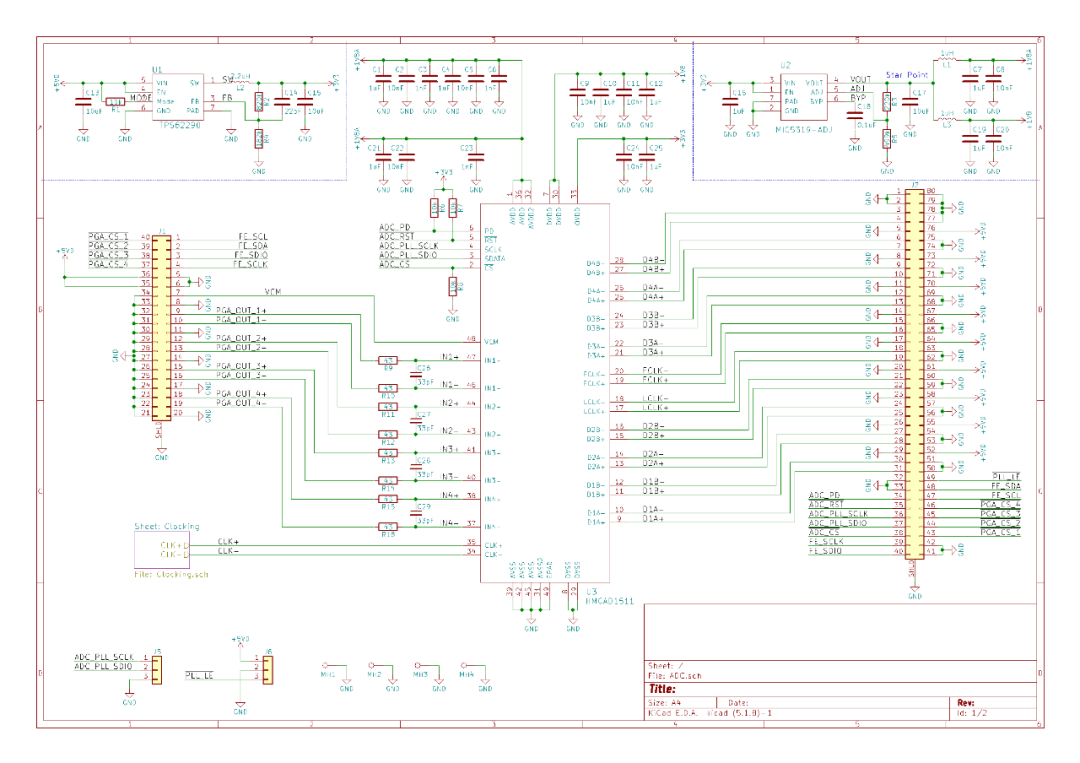

ADC采用了ADI的HMCAD1511,最便宜的1Gsps/8位 ADC,单通道的时候可以达到1Gsps、双通道为500Msps、4通道为250Msps,因此模拟带宽的设定各位350MHz@单通道、200MHz@双通道、100MHz@4通道,输出为8个DDR LVDS,可以接低成本的FPGA。

高速ADC模块的原理图和实物照片

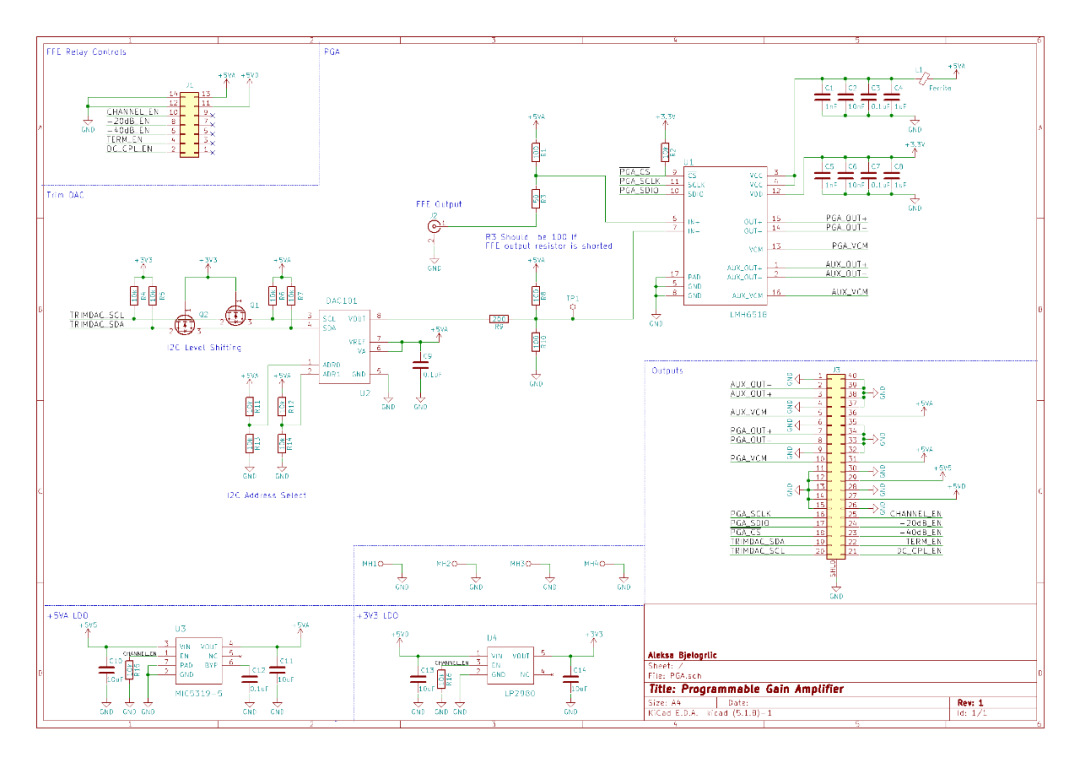

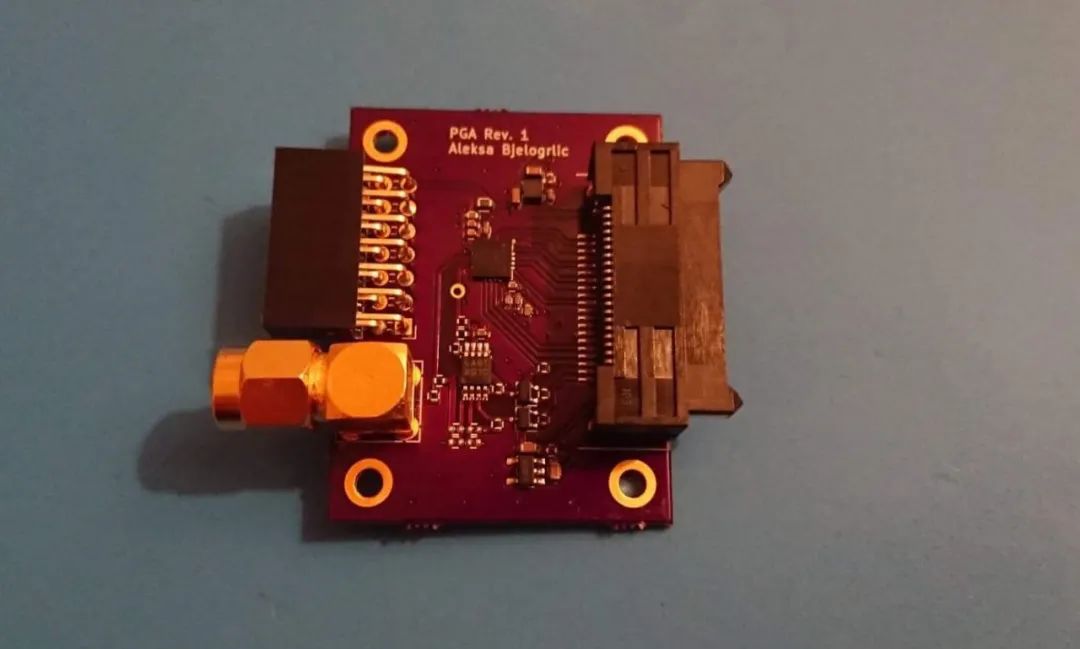

可变增益放大器部分,作者参照了Novena的数字探头的设计方案, 使用LMH6518 PGA,增益可以从-1.16dB调整到38.8dB,能够保证900MHz的带宽。

可变增益放大器模块部分的原理图和实物照片

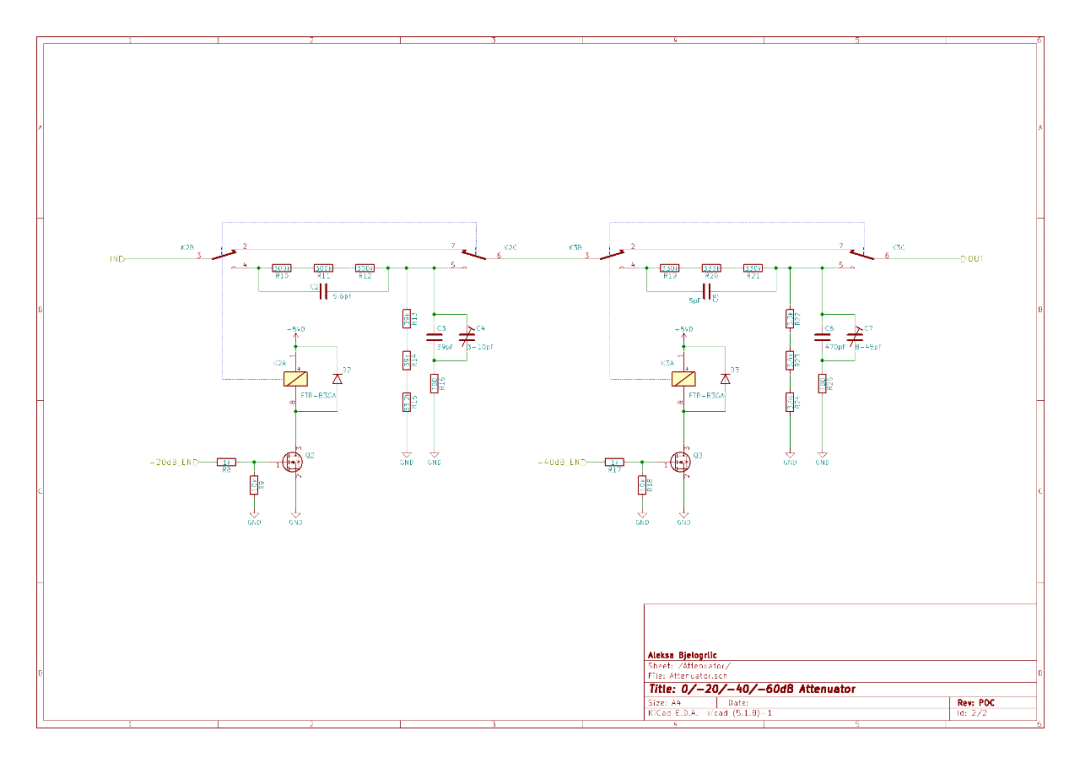

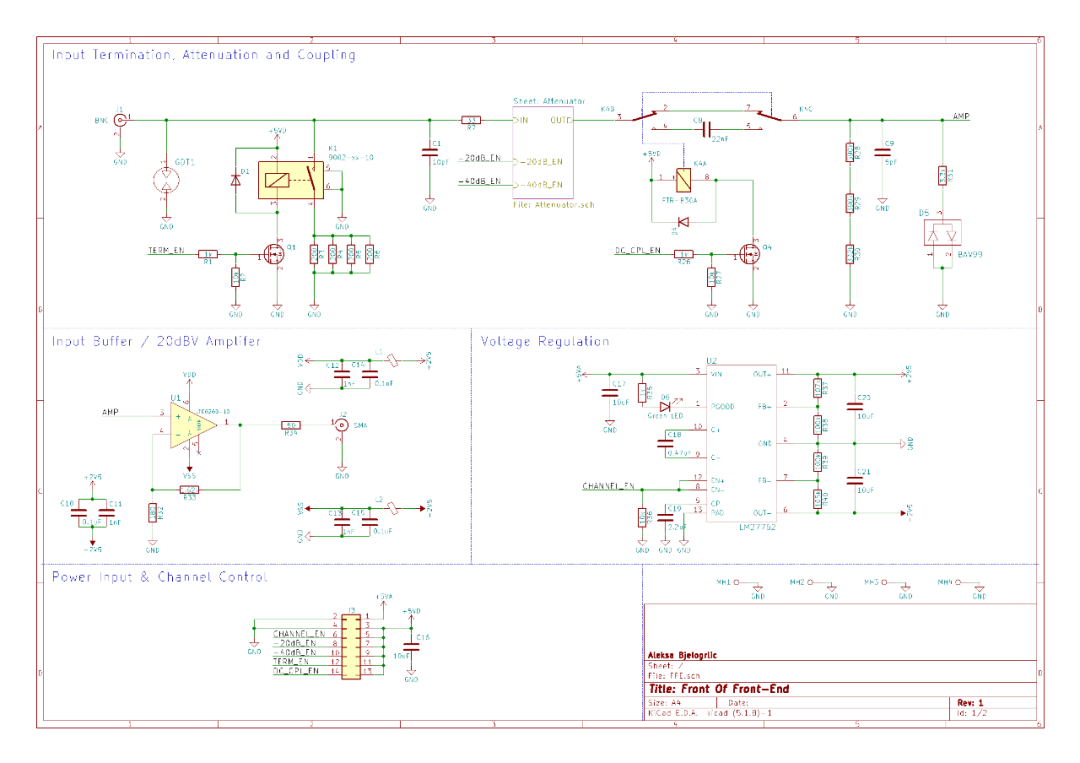

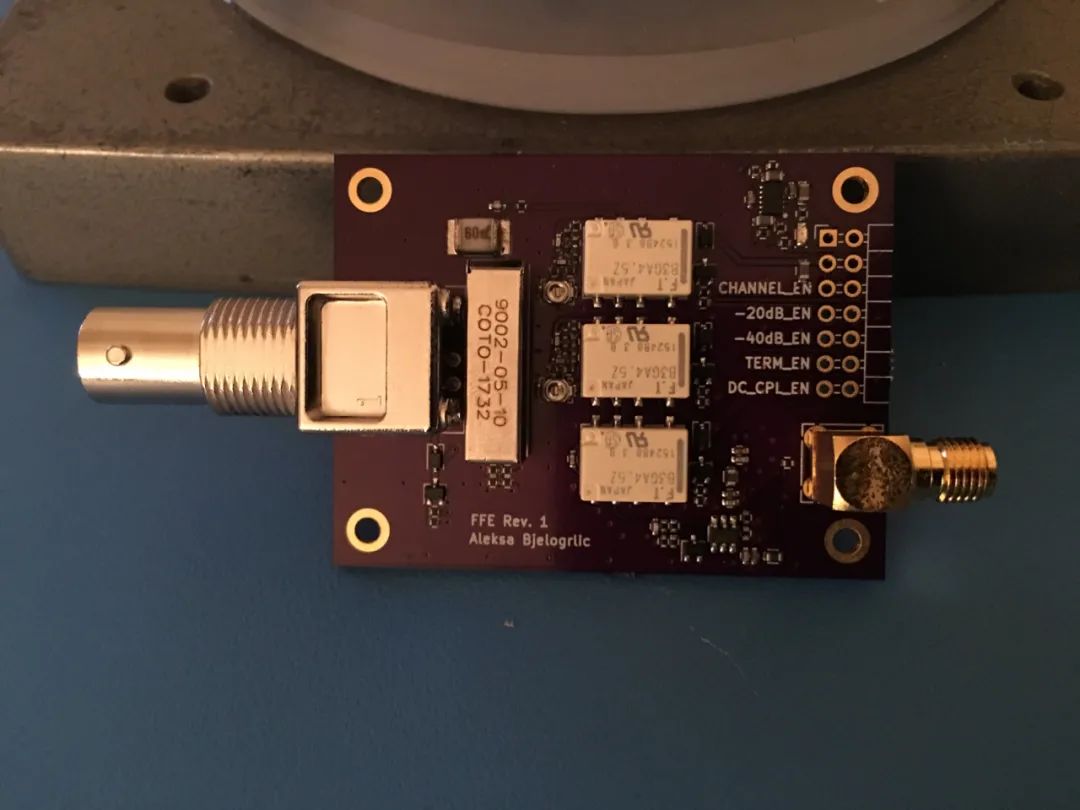

示波器模拟前端 -要保证输入阻抗为1Mohm || 15pF,以兼容现有的标准示波器探头。作者设定要采集的信号至少为500uV/Div,8位精度的ADC全量程电压为1.8V,所以系统的最大增益为450V/V,考虑到可变增益放大器的最大调整范围为87V/V,前端放大器要有10x的增益,350MHz的带宽需要3.5GHz的增益带宽积。

周末愉快!