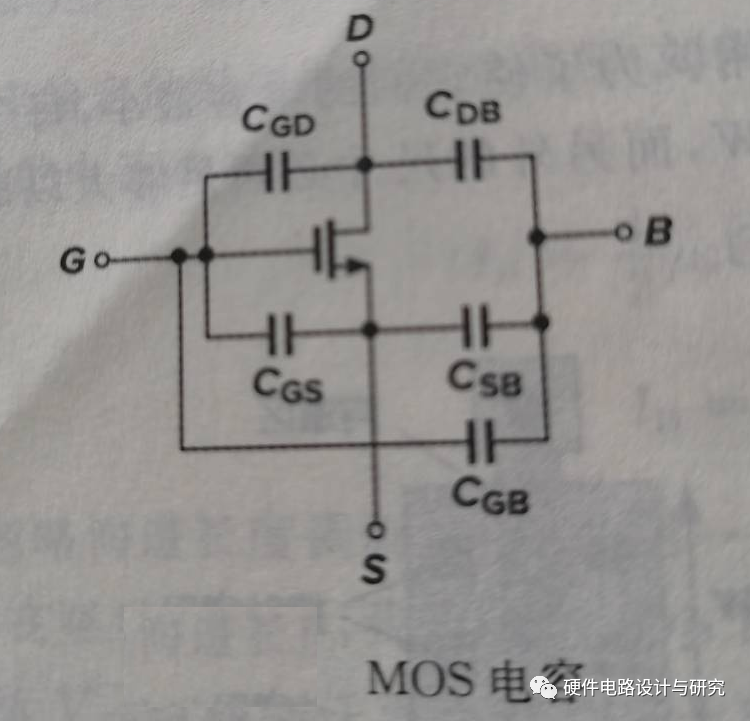

本次推文,我们来仿真一下NMOS管的寄生电容,寄生电容一方面对MOS构成的电路的高频特性有显著影响,另一方面在要求不高时,这些寄生电容也可直接当电容元件使用,除了源极和漏极之间(因为沟道的导电性会严重削弱其电容特性),MOS管其他任何两极之间均存在寄生电容。如下图所示:

在不同的电路应用中,对寄生电容的要求是不同的:电路设计在需要精度不太高的电容时,可以直接使用MOS管寄生电容来实现;而有时候希望尽可能避免出现寄生电容,从而提高电路工作速度与带宽,以及避免由此产生的电路稳定性、频率特性变差的问题。这需要我们对MOS管的寄生电容有所认识。

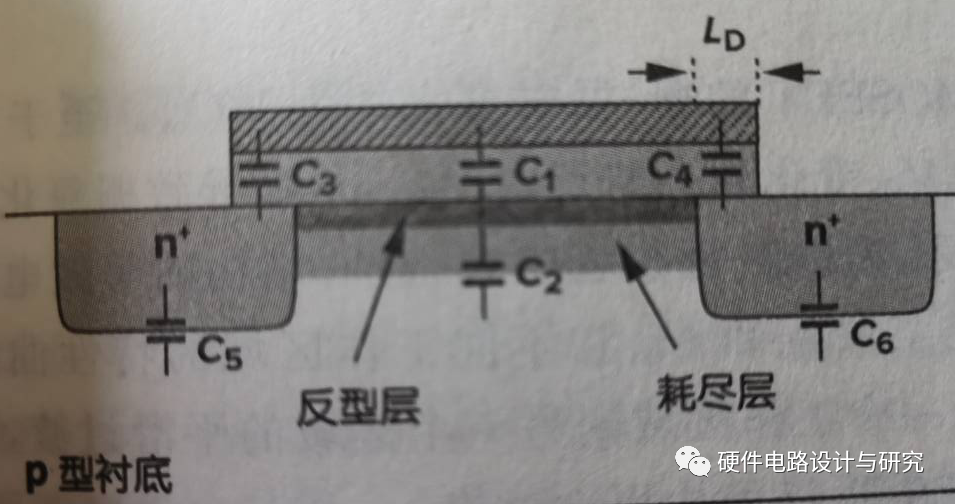

下图所示为MOS管实际结构剖面图。

基于该基本结构,我们发现有如下几类电容:

1)栅极和沟道之间的氧化层电容,也被称为MOS管的栅电容,与栅极的面积以及氧化层的介电常数有关,在上图中如C1所示,其值定义为C1=Cox*WL,

其中Cox为单位面积的栅极氧化层电容

2)衬底和沟道之间的耗尽层电容,与沟道尺寸有关,如上图中C2所示,其值为C2 =Cd*WL,其中Cd为单位面积的耗尽层电容值。

3)现在的CMOS工艺都采用了一种被称为“自对准”的技术,从而使得源极和漏极会扩散“深入”到栅极下方一些,深入的尺寸与工艺有关。这带来了另外一类电容,即多晶硅栅极与源极和漏极的交叠而产生的交叠电容。该电容也是一种平板电容,由于沟道长度方向的交叠尺寸在 某个特定工艺下是固疋值,因此该电容仅仅需要关注MOS管宽度W,定义为C3 = C4 = Cov*W,

式中,W为MOS管的宽度;Cov为单位宽度的交叠电容值。

4)源/漏区与衬底之间的PN结电容C5和C6 ,这两个电容与有源区的面积成正比。

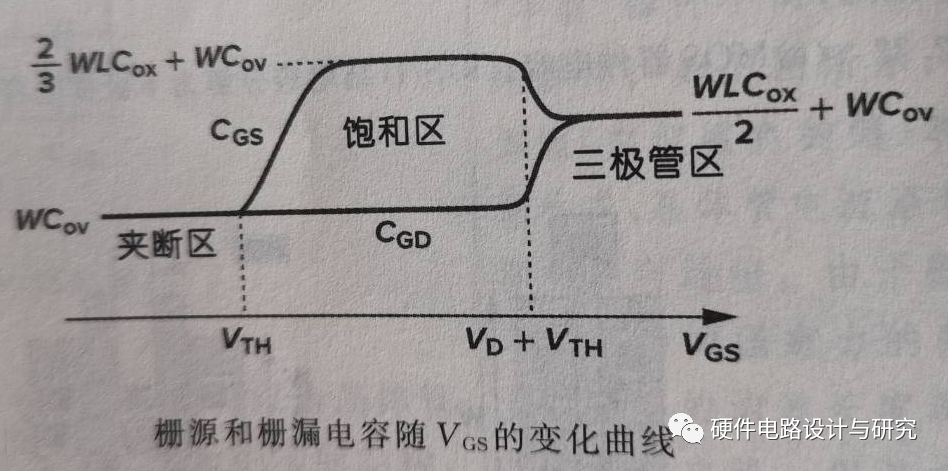

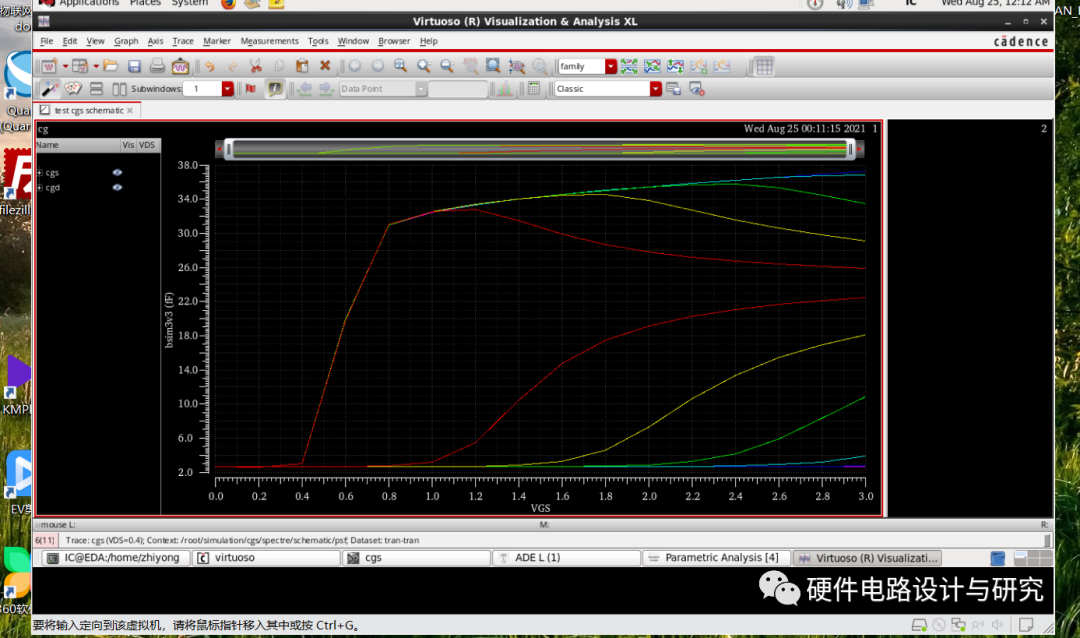

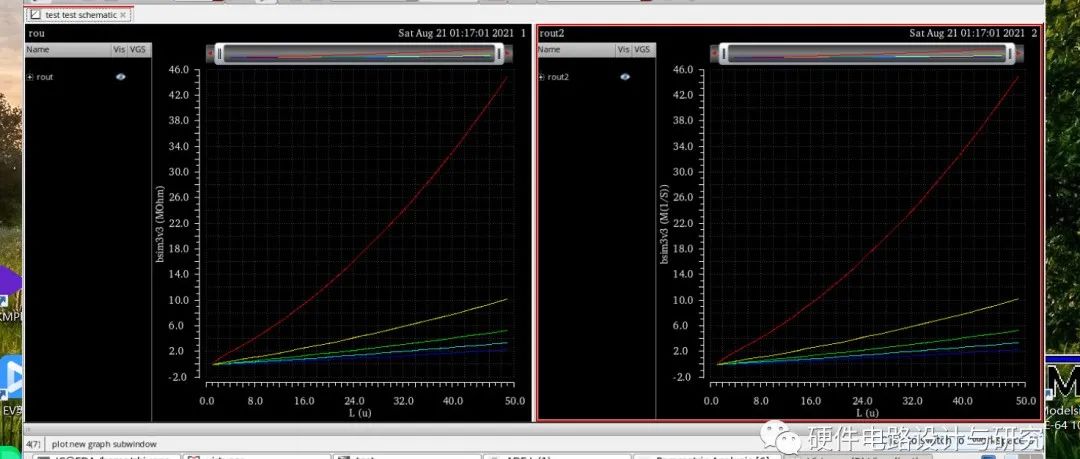

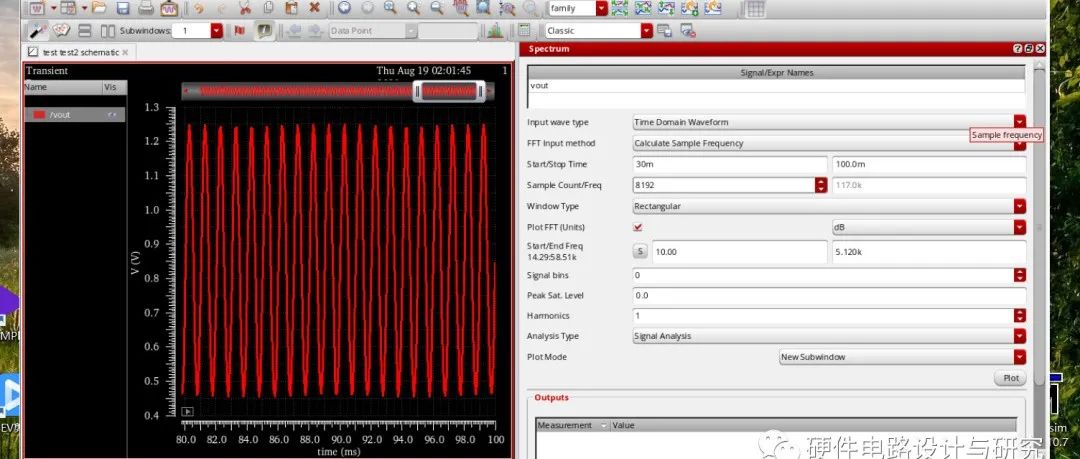

当MOS管工作在不同区域时,其导电沟道及水平方向、垂直方向上的电场分布是不同的, MOS管的栅极对Cgs和Cgd的影响贡献也有所不同。下图表示了MOS管工作在三个不同区域下的电容值示意,不同的Vds也会影响Cgs和Cgd,见后续的视频仿真讲解。

MOS用作电容使用时,通常是将漏极和源极短接作为一端,栅极作为另外一端。随着两端电压的变化, MOS管沟道特性出现变化,对外表现出的电容值也出现变化,即电容具有一定的电压系数。在某些不要求精确电容值的应用场合,还是可以使用MOS器件电容。

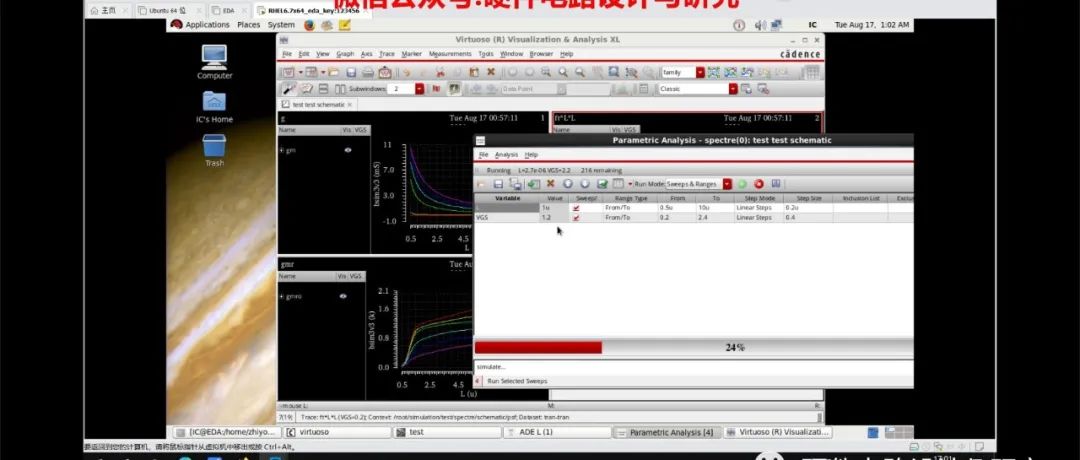

下图是扫描Vds、Vgs时的Cgs和Cgd仿真曲线,符合理论预期:

注意:

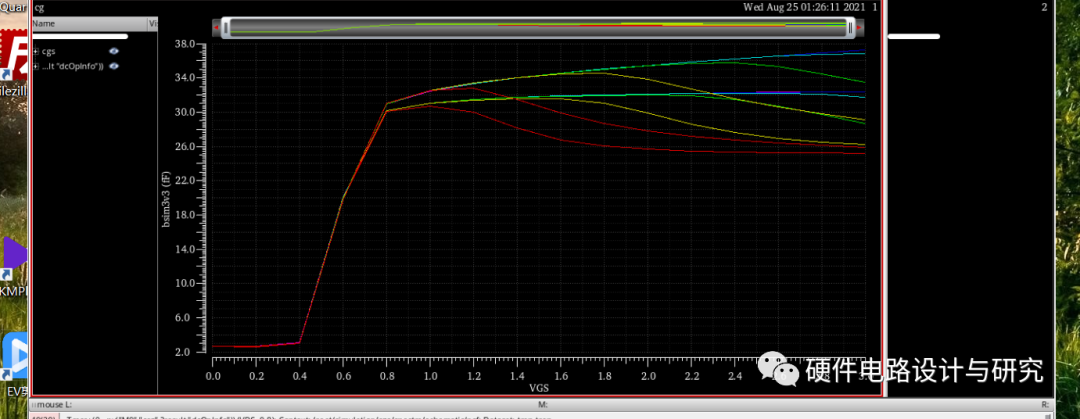

在spectre仿真时显示的Cgs和Cgd均为负数,这是怎么回事?当然上图我们已经求过反后再显示的:(- pv("M0" "cgs" ?result "dcOpInfo"))

在spectre里,Cij的定义为dQi/dVj,其意思是j端电压的变化引起i端电量的变化情况,例如:Cgs=dQg/dVs,即源端电压的变化引起栅端电量的变化情况,Cgg=dQg/dVg,栅端电压的变化引起栅端电量的变化。

假设源端电压增加dVs>0,即源端有正电荷积累,那么在栅端感应出来的电荷就为负的,即dQg<0,所以Cgs=dQg/dVs<0,Cgs求出来会是负数,只有Cgg,Css,Cdd等为正数,其它的都为负数,这是数学计算的原因,我们只要看它们的绝对值即可。

这同样解释为什么Cgs与Csg求出来会有轻微的差异,因为在源端变化电压引起栅端电荷的变化量,与在栅端变化相同电压变化引起源端电荷变化量是不完全相同的。下图是Cgs和Csg仿真:

视频讲解1:

视频讲解2:

以往相关推文:

2021-08-21

2021-08-18

2021-08-16