公众号:高速先生

作者:黄刚

有均衡的高速串行信号你们见多了,那有均衡的DDR信号你们见过吗?来,高速先生带你去领略下!

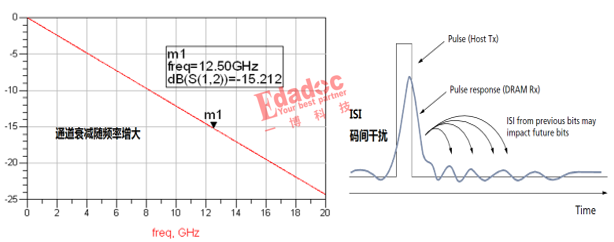

首先我们还是回顾下高速串行信号的相关概念。关于高速串行信号为什么需要各种均衡,我们在之前的文章(很多篇文章)都给大家介绍过很多了。其实总结来说就是由于高速信号达到一定的速率后,链路本身的衰减会急剧增大,另外由码型的不同带来的ISI(码间干扰)的影响也变得越来越大,这两方面都严重影响了高速串行信号的性能。

当然说到影响,简单来说就是使得信号的眼图张开度降低甚至达到闭合状态。下图是我们在同一个PCB通道下加入不同速率的信号在接收端的眼图结果,由于链路高频的衰减不断增大,可以看到从1Gbps到25Gbps速率的传输范围内,眼图从张开得很大慢慢到闭合了。

所以对于高速信号来说,各种均衡的配置就显得非常有必要了,我们一般能看到在芯片的收发端配置了几种常见的均衡,例如CTLE,FFE,DFE这些!

关于高速信号的介绍就到这里,高速先生差点忘记本文其实主要想写的是DDR仿真了!

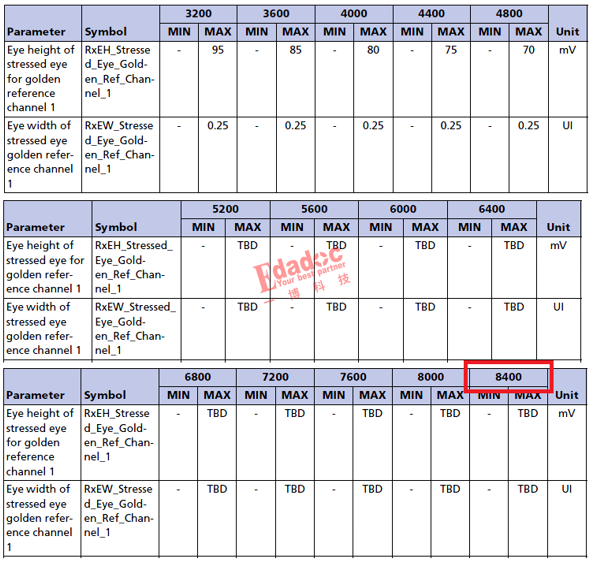

前面文章对DDR5标配的速率也有了简单的介绍,它的起步基本是DDR4的天花板,也就是3200Mbps,然后中值配置是在4800Mbps到6400Mbps之间,根据协议文档说的,最高目前写到了8400Mbps。

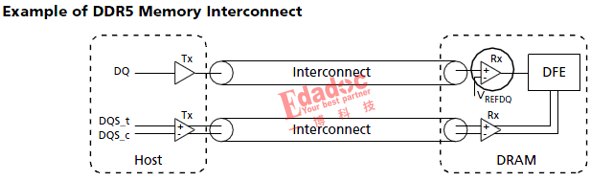

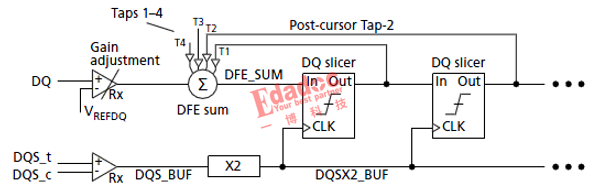

在DDR5的均衡中,主要配置了接收端的DFE均衡模块,说到DFE均衡,它无非是在FFE这种线性的均衡基础上加上了一个额外的判决功能。

通过仔细阅读DDR5协议,可以看到,DDR5的data信号标准配置是一个4tap的DFE模块。

好,关于协议和理论都太过枯燥,说点仿真的东西吧。我们直接拿到DDR5的模型,来仿真看看DFE均衡对数据信号的帮助哈。

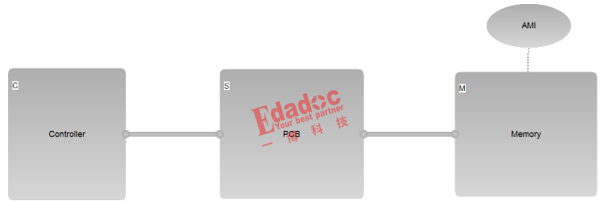

首先我们提取一根真实链路的data信号,把收发模型搭建好,如下所示:

我们看到DDR5的颗粒模型的确存在了AMI的算法,也就是把DFE的模块配置到接收模型里面去了。我们打开这个AMI模型,的确能看到DFE模块存在4tap的均衡参数可以调节。

好,本文最重点的部分来了!那就是我们通过在这个提取的DDR5数据通道上传输不同的速率,来看看接收端的结果,尤其重点来看看均衡之后的结果。

首先我们给的速率是3200Mbps,一个入门级的DDR5速率。在这个速率下,我们之前做的DDR4模块在没有DFE均衡的时候也是能成功保证的,从这个DDR5在这个速率下的仿真结果表明,DFE均衡在这个速率下帮助不大,或者说在这个速率下其实可以不需要DFE均衡。

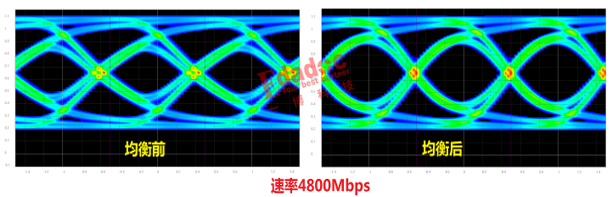

那我们再提高速率,来到4800Mbps,看看这个速率下均衡前后的变化。可以看到在这个速率下,接收端的结果已经慢慢开始衰减了,同时也能看到均衡后的效果慢慢的凸显出来了。

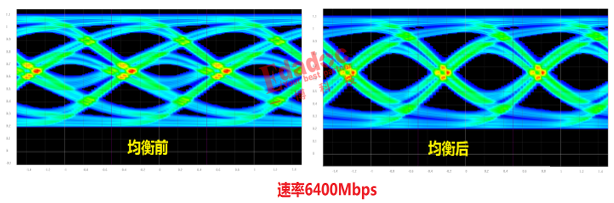

那我们再提高速率,把数据信号的速率提高到6400Mbps,在这个速率下就可以清楚的看到均衡前基本上眼图就很小了,但是通过DFE均衡后,眼图明显重新张开,效果非常明显。

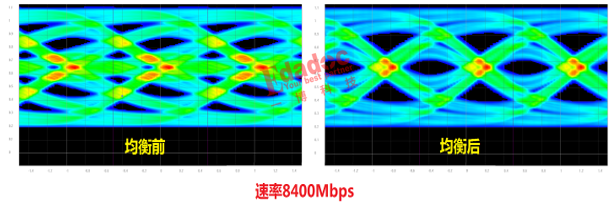

那我们最后把速率提高到协议的天花板,也就是8400Mbps这个level,这个速率其实已经超过了很多我们熟知的高速串行信号了,例如USB3.0,PCIE3.0等。我们来看看在这个速率下均衡前后的差异哈。

从仿真结果上看,这就厉害了!DFE均衡居然能把一个基本上闭合的眼图重新打开,完完全全说明了DFE均衡的作用,化腐朽为神奇哈!

通过上述的仿真结果,相信大家也清晰的看到DDR5数据传输率的确有可能传输到一个惊人的水平,各位现在还在做DDR3或者DDR4的朋友们,有没有冲动想把你们的产品升下级到DDR5了呢?

— end —

本期提问:

关于DDR5的技术,大家还有什么想知道或者有自己想法的,都可以给我们留言哈!

如果不想错过“高速先生”的精彩内容,请记得点击上方蓝字“高速先生”,右上角“...”点选“设为星标”。可第一时间看到高速先生的推文,感谢大家的关注和支持!

扫码关注

微信号|高速先生

觉得内容还不错的话,点个“在看”呗