在系统设计期间,有几个工作在不同频率上的组件(器件),例如处理器,外围设备等,它们有时可能具有自己的时钟晶体。先进先出First-In-First-Out(FIFO)队列在此类设备之间的数据交换中起着重要作用。FIFO是简单的存储器,用于数据排队通过通信总线。因此,FIFO通常用于跨不同时钟域的数据传输。我们首先描述了一个简单的同步FIFO架构,其中读写是在同一时钟上完成的。随后将会详细描述了异步FIFO的概念和设计,其中读写是在不同的时钟频率上完成的。

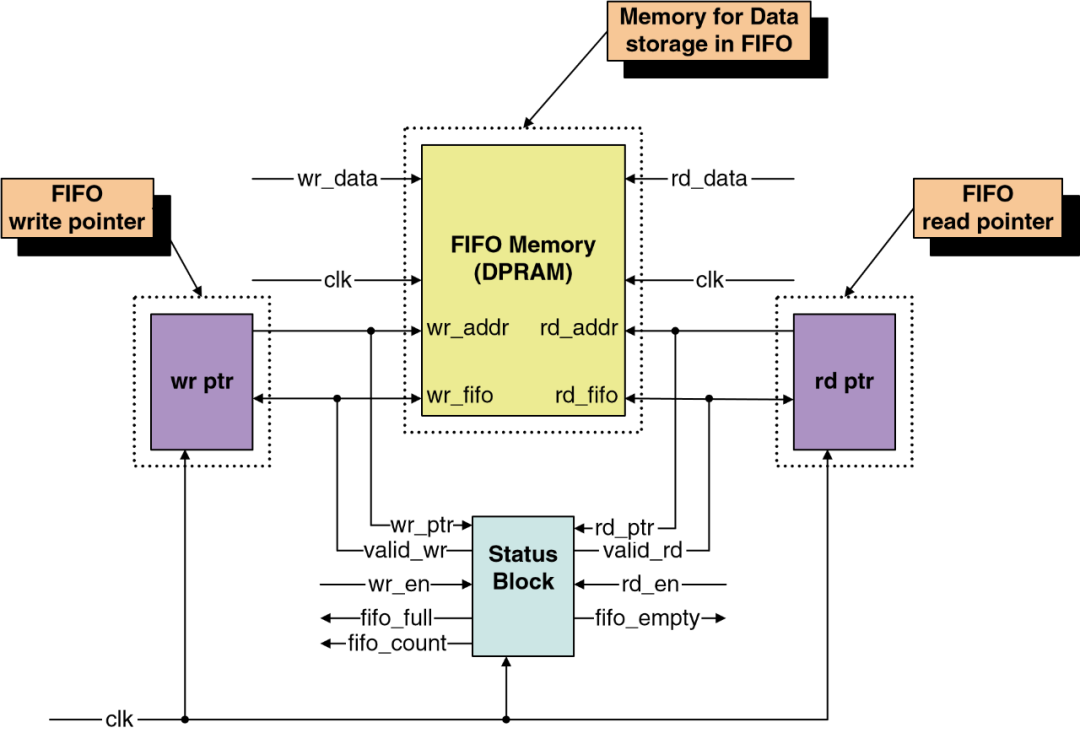

图1-1 同步FIFO结构

1.1同步FIFO的结构

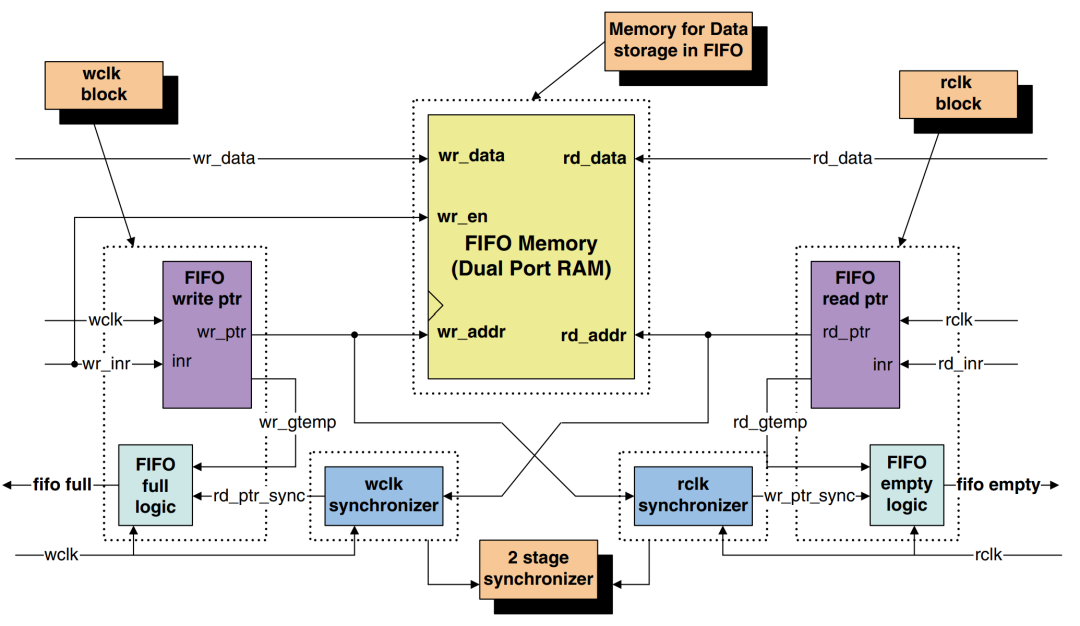

图1-1展示了同步FIFO的一般结构,DPRAM(双端口RAM)用作FIFO存储器,具有独立的读取和写入功能。

读写端口具有由两个读写指针生成的单独的读写地址。写指针指向下一步将要写入的位置,读指针指向下一步将要读取的位置。有效的写使能会增加写指针,而有效的读使能会增加读指针。

图1-1展示一个“Status Block”,该状态块生成“fifo_empty”和“fifo_full”信号。如果断言(断言就是把信号变为有效)“fifo_full”,则意味着没有更多空间可将更多数据写入FIFO。同样,“fifo_empty”表示FIFO中没有可用的数据可供外部模块读取。可以用两个指针的不同逻辑来表示某个时间点FIFO中数据空或者数据满的状态。

图中所示的双端口存储器(DPRAM)可以具有同步读取或异步读取的功能。对于同步读取,在FIFO输出数据有效(valid)前,就应该提供明确的读信号。对于异步读取,DPRAM没有寄存的数据输出;有效数据一经写入即可用(首先读取数据,然后指针递增)。

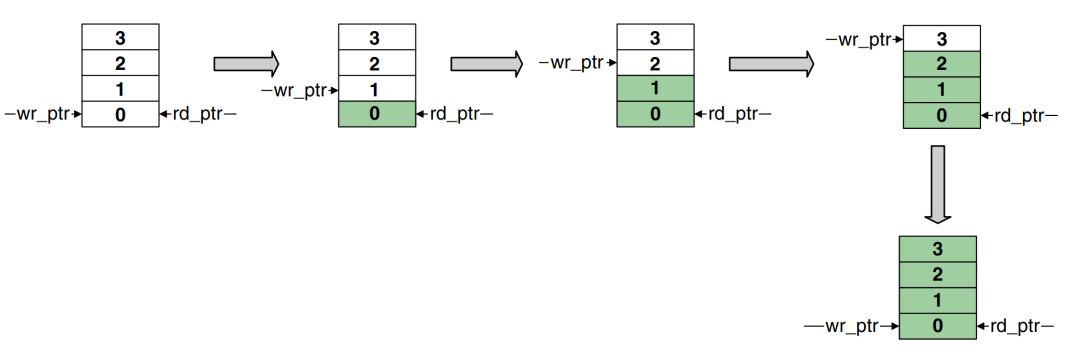

1-2 FIFO满状况

1-2 FIFO满状况

1.2同步FIFO的工作

复位时,读和写指针都初始化为零。在此期间,信号“ fifo_empty”被置为有效,“fifo_full”保持为“低”。当FIFO为空时,将阻止对FIFO的进一步读取,因此只能进行写操作。随后对FIFO的写操作会增加写指针,并置低“fifo_empty”信号。当到达没有空间容纳更多数据且写入指针等于RAM_SIZE -1的时候。此时,写操作将让写指针再次回滚至零,从而使“fifo_full”信号变为高电平。那么当读指针等于写指针时,FIFO是已满还是为空?因此有必要在这两个条件之间进行区分。

1.2.1 FIFO空和满的生成

图1-2展示了4深度同步FIFO的FIFO完整生成。图1-2所示的所有转换都在随后的时钟中。如图所示,当写入让两个指针在下一个时钟中变为相等时,FIFO变满。这使“fifo_full”信号有效的条件如下:

fifo_ full =(read _ pointer ==(write _ pointer +1))AND "write"

下面还展示“fifo_full”逻辑的示例Verilog代码:

always @ (posedge clk or nededge reset_n)

begin: fifo_full_gen

if (~reset_n)

fifo_full < = 1’b0;

else if (wr_fifo && rd_fifo)

;//do nothing

else if (rd_fifo)

fifo_full <= 1’b0;

else if (wr_fifo && (rd_ptr = wr_ptr + 1’bl))

fifo_full <= 1’bl;

end类似地,当读取导致两个指针在下一个时钟中变为相等时,FIFO变为空。这使“fifo_empty”信号有效的条件如下:

fifo_ empty =(write _ pointer ==(read _ pointer +1))AND "read"

下面还展示“fifo_empty”逻辑的示例Verilog代码:

always @ (posedge clk or negedge reset_n)

begin: full_gen

if (~reset_n)

fifo full < = 1’bl;

else if ( wr_fifo && rd_fifo)

; //do nothing

else if (wr_fifo)

fifo_empty <= 1’b0;

else if (rd_fifo && (rw_ptr = rd_ptr + 1’bl ))

fifo_empty <= 1’bl;

end1.2.2可选的方案

生成“fifo_full”和“fifo_empty”条件的另一种方法是使用一个计数器,该计数器不断指示FIFO中剩余的空间数量。

计数器的宽度必须等于FIFO的深度,以便存储最大值。计数器在复位时初始化为零值。任何后续的写操作会使计数器加一,而随后的读操作会使计数器减一。

现在,当计数器值达到“零”时,可以轻松生成FIFO空状态,而当计数器值等于FIFO的大小时,则可以轻松生成FIFO已满状态。

与本节中提到的方法相比,本节中提到的另一种方法虽然简单,但效率不高。因为它需要额外的硬件(比较器)来生成FIFO空和FIFO满的条件。随着FIFO的深度增加,计数器的宽度也增加。因此需要更高阶的比较器来产生FIFO空和FIFO满状态信号。最终,这会降低FIFO的最大工作频率。

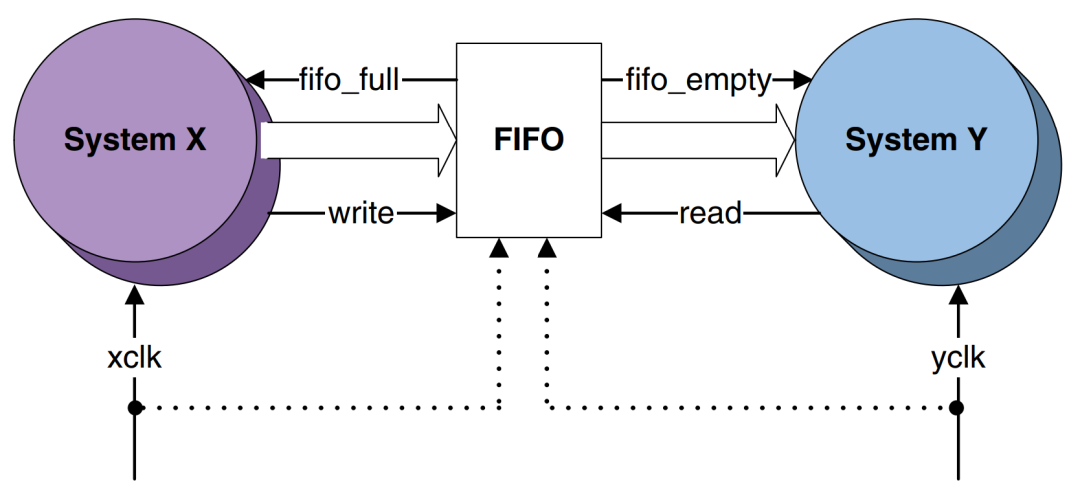

二、异步FIFO

异步FIFO用于在两个异步时钟域之间传输数据。图2-1展示两个系统“System X”和“System Y”,其中来自“SystemX”的数据被传输到“System Y”,这两个系统都在不同的时钟域工作。

2-1 异步FIFO的数据传输

2-1 异步FIFO的数据传输

“System X”将“xclk”时钟上的数据写入FIFO,并由“yclk”时钟上的“系统Y”读出。

“FIFO full”和“FIFO empty”信号负责下溢和上溢的条件。

上溢条件由“FIFO full”信号处理,即,如果断言“FIFO Full”信号,则不会将数据写入FIFO,否则数据将被覆盖。

通过“FIFO empty”信号来注意下溢条件,即,如果断言“FIFO empty”信号,则不会从FIFO读取数据,否则将读取无效数据。与握手信令不同,异步FIFO用于对性能至关重要的设计,在这些设计中,时钟延迟是一个更加重要的因素,而不是系统资源。

正如在同步FIFO中提到的,可以使用双端口RAM来实现简单的同步FIFO,该双端口RAM具有用于在同一时钟下进行读写操作的单独端口以进行读写操作。在设计异步FIFO时可以扩展相同的概念,并特别注意FIFO空和FIFO满信号的生成,以避免出现亚稳态情况。

2.1避免将二进制计数器用于指针实现

以写指针为例,每当有对FIFO的有效写请求时,写指针总是基于写时钟上递增。同样,只要有有效的读取请求,读取指针就会在读取时钟上递增。为了产生FIFO Full信号,需要将写指针与读指针进行比较,并且由于两个指针都与各自的时钟同步,但是彼此异步,如果将二进制计数器用于比较,则会导致指针值的采样错误以进行比较。指针实现。如下图所示。

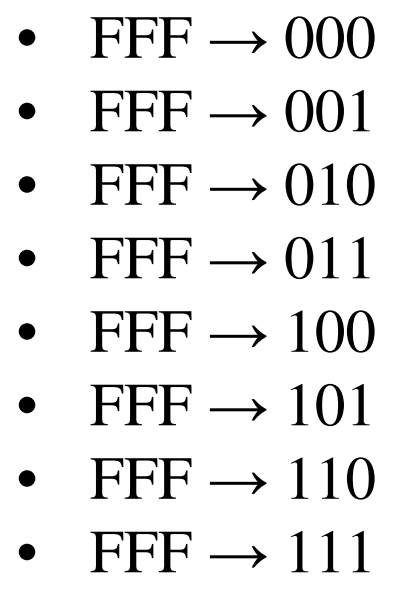

假设二进制计数器从FFF变为000,在这种情况下,所有位都将同时更改。(异步时钟域简单讲为什么要格雷码,计数器中的位数不应该同时改变,会增加错误概率,因为从FFF到000会有多种过渡态,这种过渡态可能会导致错误)可以通过使计数器同步来避免亚稳态,但是这仍然可能会获得超出范围的采样值,因此,并非最终解决方案中要同步计数器。

从FFF到000可能的过度:

如果同步时钟沿位于从FFF到000的过渡的中间,则有可能在新的时钟域中对3位二进制值中的任何一个数值进行采样和同步。

由于FIFO满标志和FIFO空标志的生成取决于这些指针值,因此这些指针的值不正确将导致标志的错误触发。可能存在以下情况:即使实际上FIFO已满,也不会触发FIFO满标志,从而导致数据丢失,或者未触发FIFO空标志,从而导致无效数据。

注意:考虑到以上情况,强烈建议避免将二进制计数器用于读写指针实现

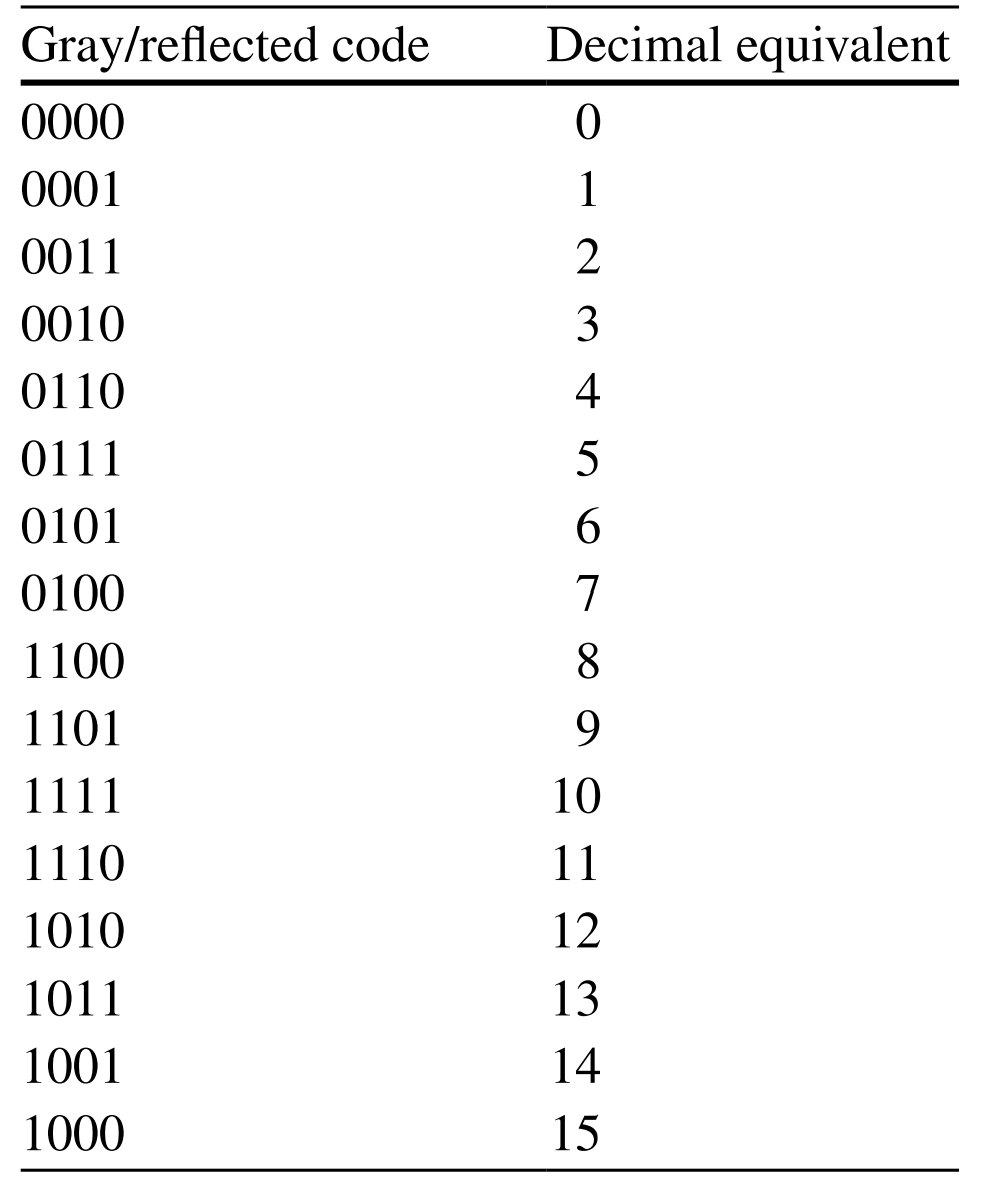

2.2使用格雷码取代二进制计数器

图2-2 同步对FIFO满逻辑的影响

格雷码相对于纯二进制数的优势在于,格雷码中的数字在从一个数字到下一个数字之间变化一位。要获得不同的格雷码,只要两个数字不相同,就可以从任意位组合开始,然后通过以任意所需的方式仅将一位从0更改为1或从1更改为0来继续获取其它格雷码,格雷码也称为反射码。由于格雷码是单位距离码,因此每个下一个值不同于上一个值的位仅有一个,即,如果出错将导致最多一位错误。举例,如果计数器从“1010”变为“1011”,那么即使出错,也只会读到“1010”,正确的话就会读出“1011”,相比较二进制的多种错误可能,这降低错误率和错误可能。

注意:同步格雷计数器很少会导致采样的计数器值出现亚稳态,其次,采样的值最多会有一位错误。

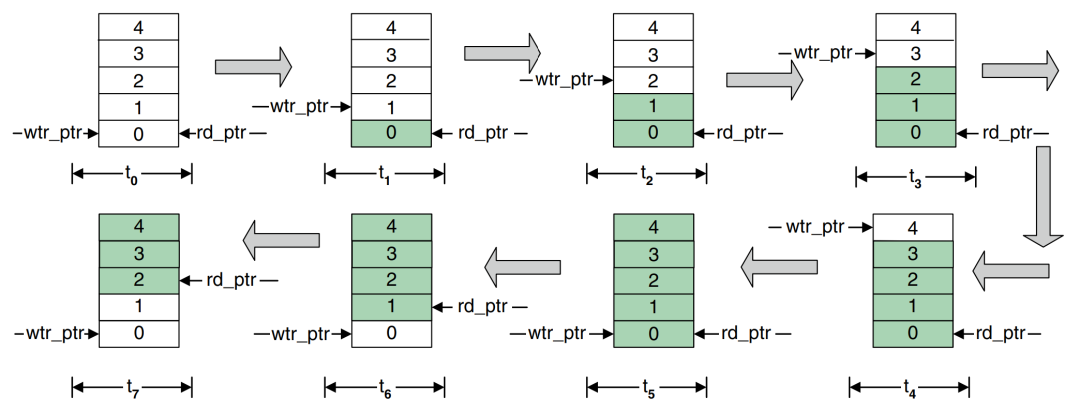

2.2.1指针同步的影响

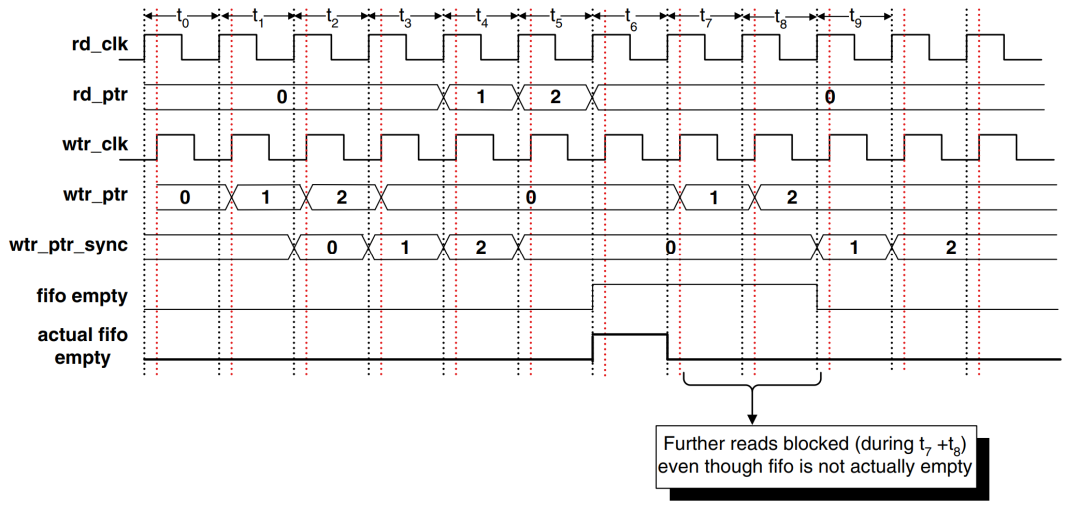

如果FIFO已满,应阻止对FIFO的进一步访问。为了计算FIFO满状态,必须对在各自时钟上递增的读和写指针进行比较。读指针(格雷编码)需要与写时钟同步。让我们举个例子。如图2-2所示,在FIFO为空的情况下,初始读取指针和写入指针在t0时为零。当随后的写操作在FIFO上进行时,写指针将递增。当写指针等于读指针并且FIFO变为FULL时,达到一个阶段。如图2-3所示,这发生在t5。现在,如果在t6发生读取,由于典型的同步器电路至少由两个触发器组成,因此在写入时钟上同步读取指针将导致在两个写入时钟之后反映出更改的读取指针。这导致在额外的周期中阻止对FIFO的其他写操作,但这是无害的。如果在FIFO实际上已满时没有阻止写操作,那将是一个问题。同样,当FIFO为空时,应阻止对FIFO的进一步读取访问

2-3 FIFO满时序

图2-4 同步对FIFO空逻辑的影响

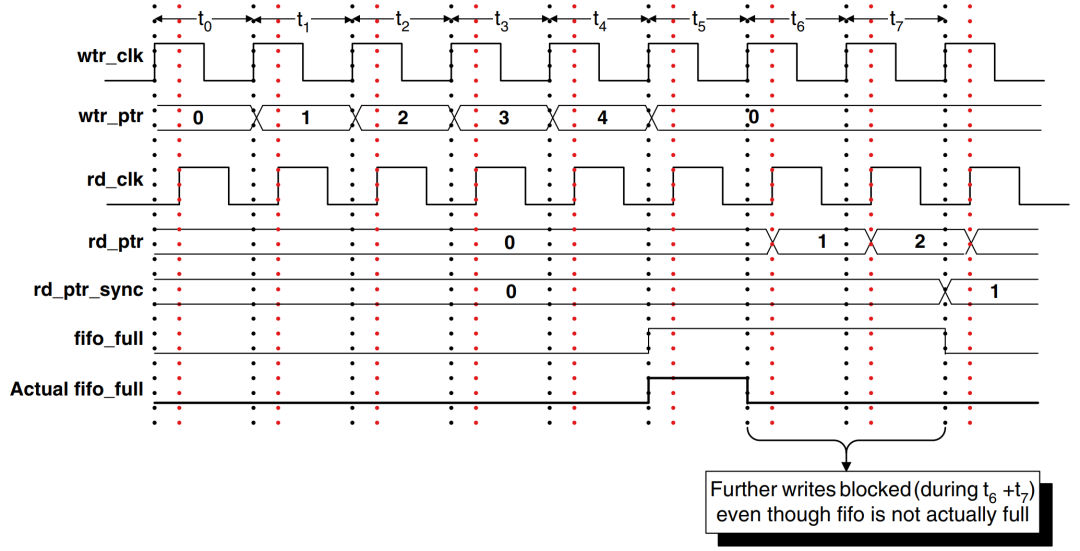

对于FIFO空计算,写指针与读时钟同步,并与读指针进行比较。因此,读取端会看到延迟的写入(两个时钟延迟的信号),即使实际上有一些数据,仍然会指示FIFO为空。这将导致读取被阻塞,直到写入对读取端可见为止。

如图2-4所示,在t0且FIFO为空的情况下,初始读取和写入指针为零。在FIFO上进行后续写操作时,写指针将递增。当写指针等于读指针并且FIFO变为FULL时,达到一个阶段。如图2-5所示,这发生在t3。

随后的读取在t4开始,并且FIFO在t6再次变空。现在,由于典型的同步器电路至少由两个触发器组成,因此在t7和t8再次写回FIFO,因此在读时钟上同步写指针将导致在两个读时钟后反映写指针的变化。这样会阻止对FIFO的其他读取,并且是无害的。如果在FIFO实际上为空的情况下不阻止读取,那将是一个问题。

图2-5 FIFO空

注意:向写方报告FIFO满时,FIFO是满的;向读方报告FIFO为空时,则为FIFO。即使指针的同步值(写期间的同步读指针和读期间的同步写指针)在短时间内保持亚稳态,其效果也将是阻止写操作。

2.3 FIFO指针的格雷码实现

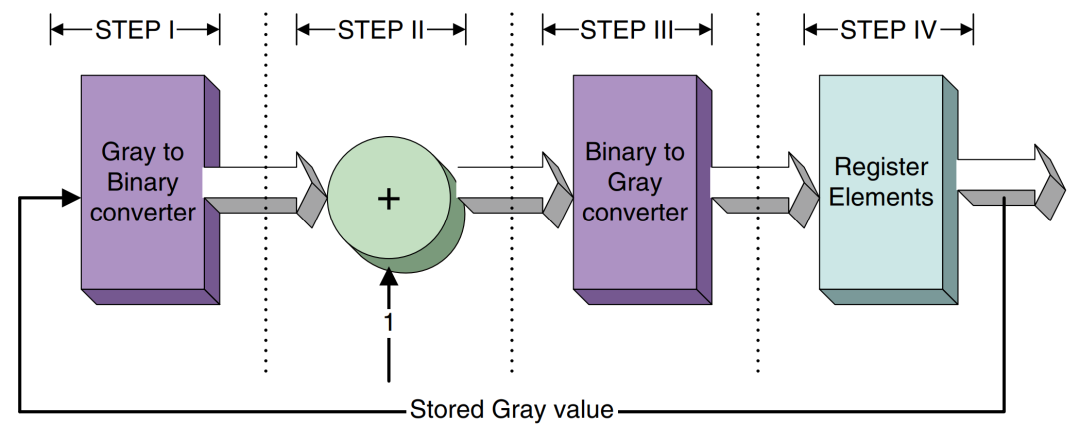

读和写指针值都需要正确采样,以完美生成FIFO空和FIFO满条件。在时钟域之间传递指针的最佳方法是将格雷码计数器用于指针实现,因为如果同步时钟信号进入计数器转换的中间,它们将消除大多数错误。设计一个格雷码计数器似乎很复杂,但确实很简单,应该做的所有事情如下:

步骤I:将Gray值转换为Binary值。

步骤II:根据某些条件递增二进制值。

步骤III:将Binary值转换回Gray。

步骤IV:将计数器的最终Gray值存储在寄存器中。

图2-6 展示生成格雷码计数器的步骤

图2-6 使用二进制加法器的格雷码计数器

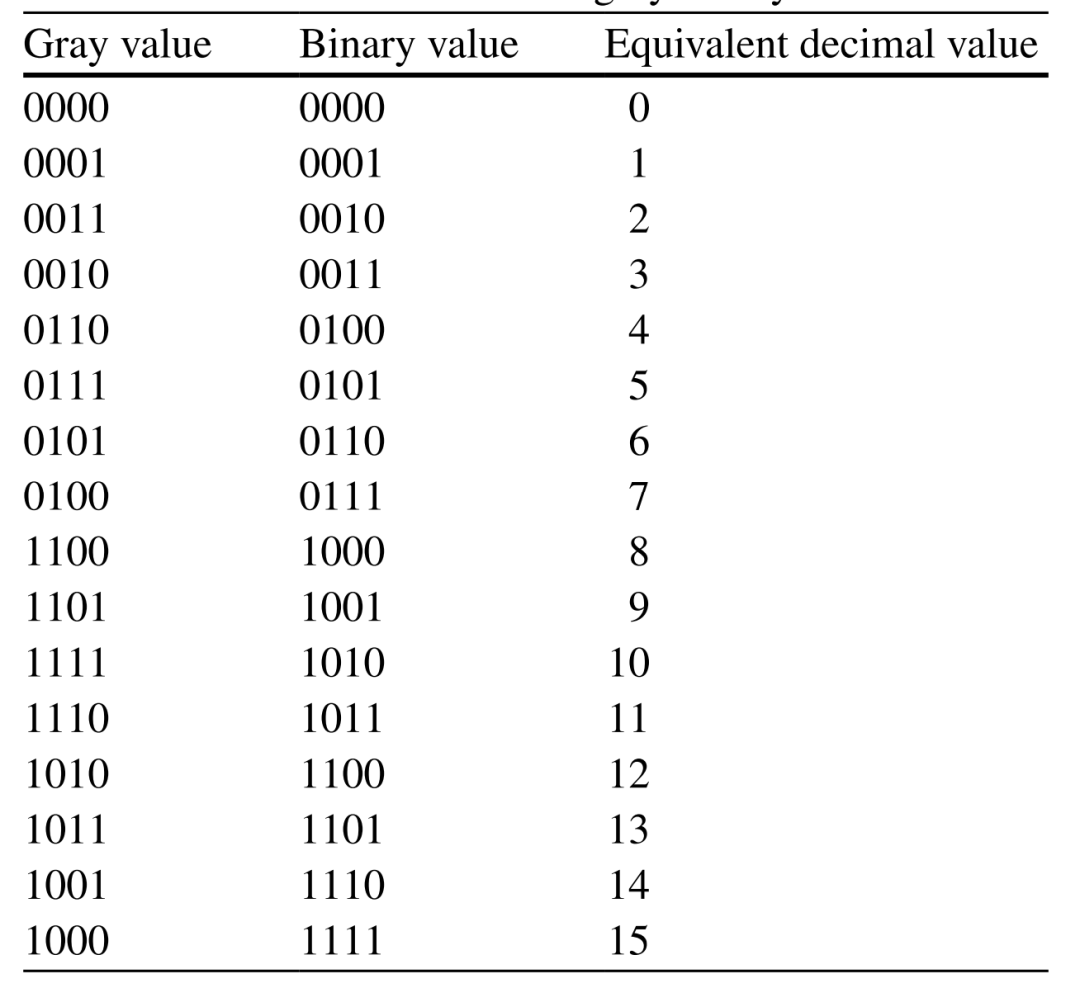

图2-7 计数器以格雷/二进制递增

2.3.1格雷码到二进制的转换器

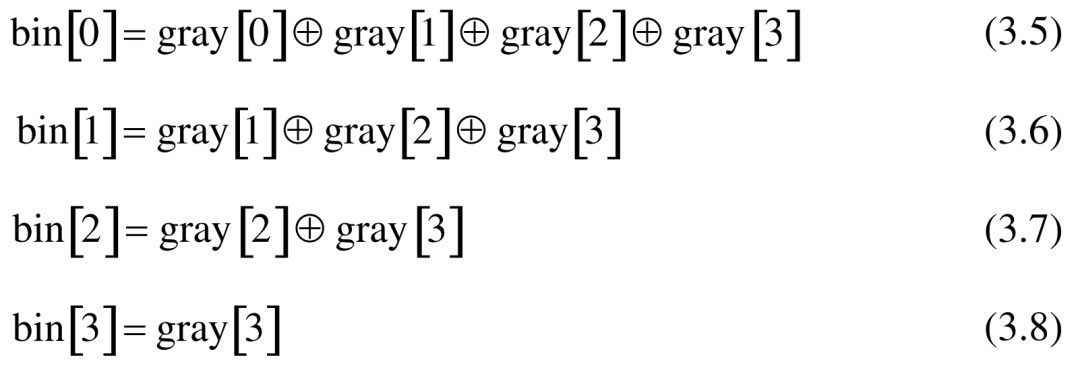

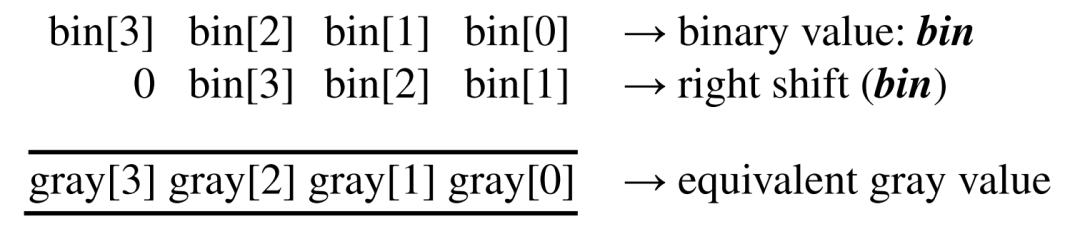

图2-7列出了用格雷码和二进制计数时的四位计数器值。当在时钟上递增时,特定列中的后续行将显示计数器的转换值。格雷码到二进制转换的方程式:

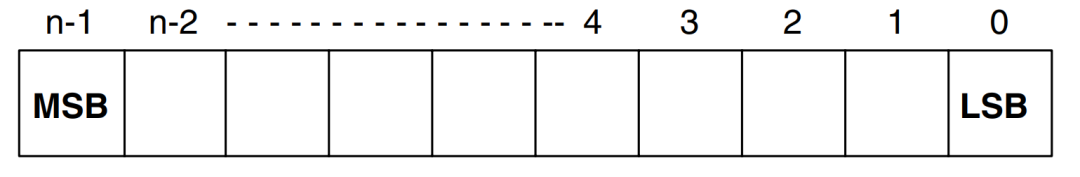

图2-6 计数器的位编号

其中i <n -1,在n位计数器

图2-5 展示计数器的位编号

让我们举一个简单的例子,将格雷码“ 1010”转换成它的二进制等效值。取n – 1 = 3

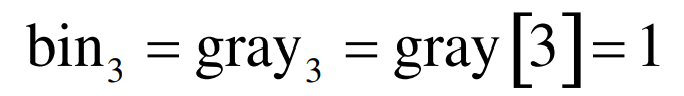

将i = 3 代入上面3.3的等式中:

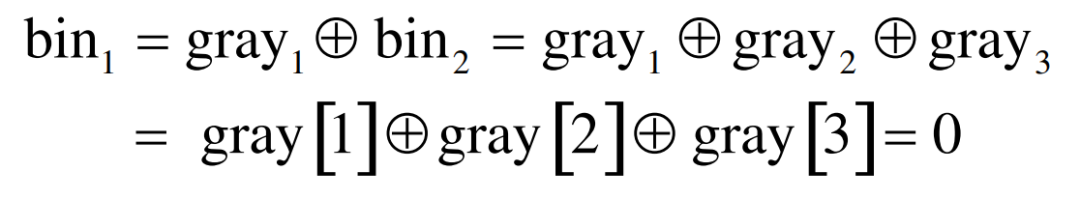

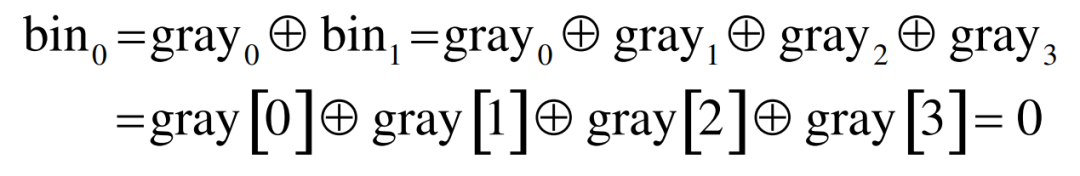

将i = 2 代入上面3.4的等式中:

将i = 1 代入上面3.4的等式中:

将i = 1 代入上面3.4的等式中:

因此,我们可以得到下面四个等式:

基于以上等式,格雷值“ 1010”的最终二进制等效值是“ 1100”。

因此,从上面的方程式中可以清楚地看出,可以通过将灰度值右移3来生成bin[3],通过将灰度值右移2来生成bin [2],通过将灰度值右移1来生成bin [1],然后将bin[0]生成 将格雷码右移0。

下面是上述格雷码到二进制转换器的Verilog代码:

module gray_to_bin (bin , gray);

parameter SIZE = 4;

input [SIZE] – 1:10] bin;

output [SIZE – 1:10] gray;

reg [SIZE – 1:10] bin;

integer i;

always @ (gray)

for ( i = 0; i <= SIZE; i = i + 1)

bin[i] = ^(gray >> i);

endmodule2.3.2二进制到格雷码转换器

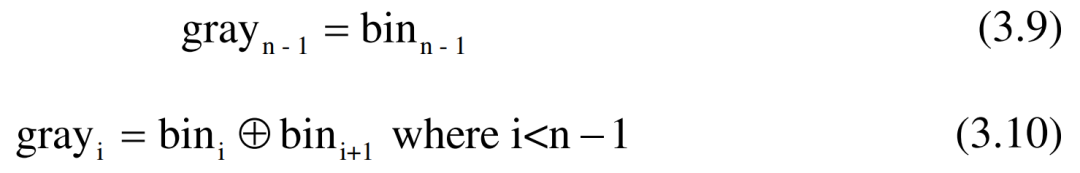

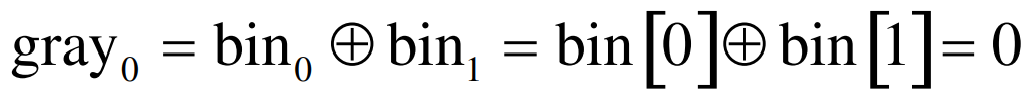

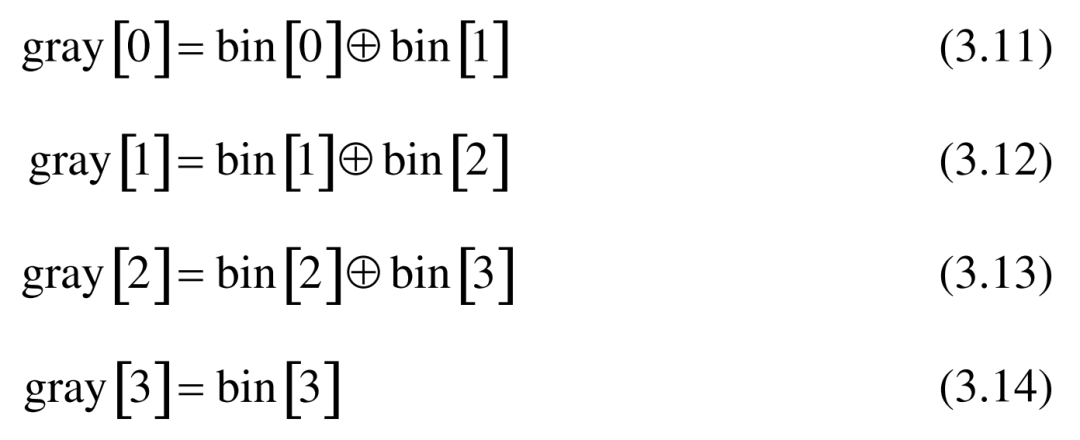

下面是二进制转换到格雷值的等式:

让我们举一个简单的例子,把二进制“1100”转回它等效的格雷值。

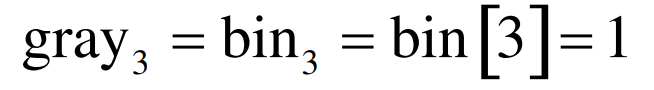

取n – 1 = 3

把i = 3 带入上面的3.9等式中:

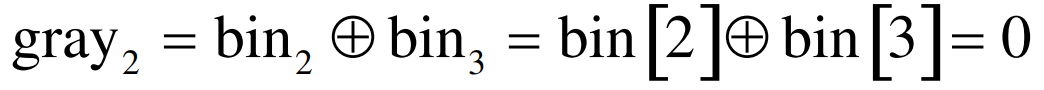

把i = 2 带入上面的3.10等式中:

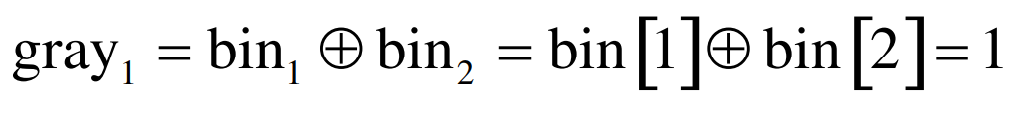

把i = 1 带入上面的3.10等式中:

把i = 0 带入上面的3.10等式中:

这给出了与给定二进制值“ 1100”等价的格雷值“ 1010”

基于以上的等式,我们可以得到下面四个等式:

从等式3.11–3.14推断,可以通过在二进制值与其右移得到的值之间执行异或运算来获得等效格雷值,如下所示:

下面是二进制转格雷码的Verilog代码:

module bin_to_gray (bin, gray);

parameter SIZE = 4;

input [SIZE-1:0] bin;

output [SIZE-1:10] gray;

assign gray = (bin >> 1) ^ bin;

endmodule2.3.3格雷码计数器的实现

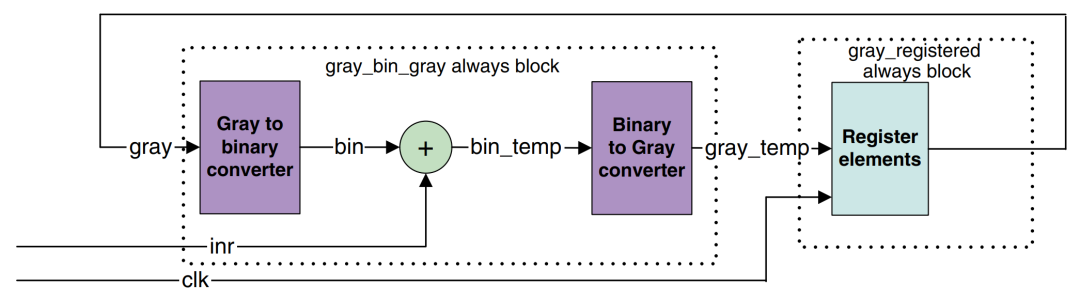

它是图2-6所示的所有四个步骤的组合(格雷至二进制转换器,加法器,二进制至格雷转换器以及最后一组用于存储格雷码的寄存器元素)。

以下是格雷码计数器的Verilog代码:

module gray_ counter (clk, gray, inr, reset_n)

parameter SIZE = 4;

input clk, inr, reset_n;t

output [SIZE -1 ] gray;

reg [SIZE] – 1 ] gray_temp, gray, bin_temp, bin;

integer i;

always @ (gray or inr)

begin:gray_bin_gray

for (i = 0; i<SIZE ; 1 = i +1)

bin[i] = ^(gray >> i); // gray to binary conversion

bin_temp = bin + inr; // addition in binary

gray_temp = bin_temp >> 1) ^ bin_temp; // binary to gray conversion

end

endmodule

图2-8 格雷计数器逻辑

下面的Always块显示了转换后的格雷值的register:

always @ (posedge clk or negedge reset_n)

begin:gray_registered

if (~reset_n)

gray <= {SIZE {1’b0}};

else

gray <= gray_temp;

end图2-8展示了上述格雷计数器代码的逻辑图。

2.4 FIFO空标志和满标志的生成

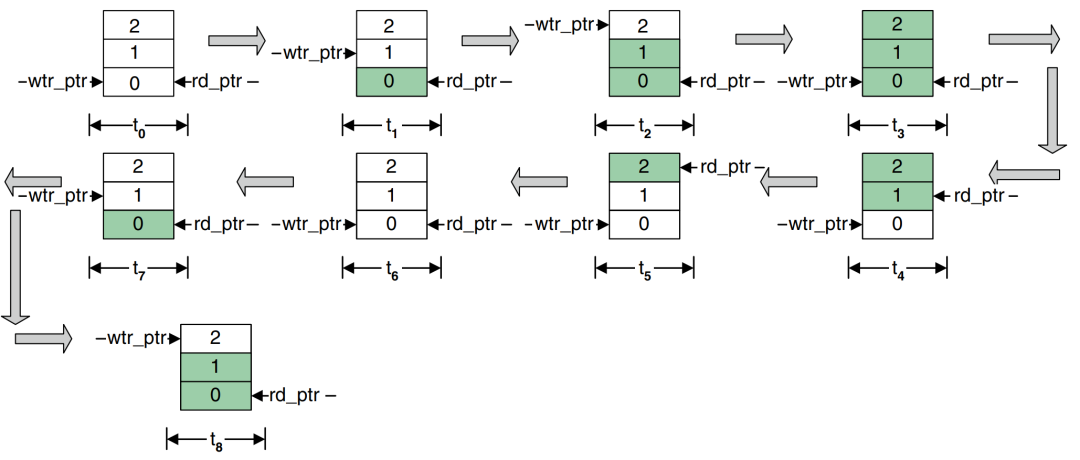

N位指针可以寻址FIFO中的2*N个位置。由于当两个指针相等时FIFO可能为空或已满,因此需要一个额外的位来区分这两个条件。当指针的二进制的最高有效位不同且其余N位相等时,FIFO已满。当指针的二进制在所有位位置完全相等时,FIFO为空。

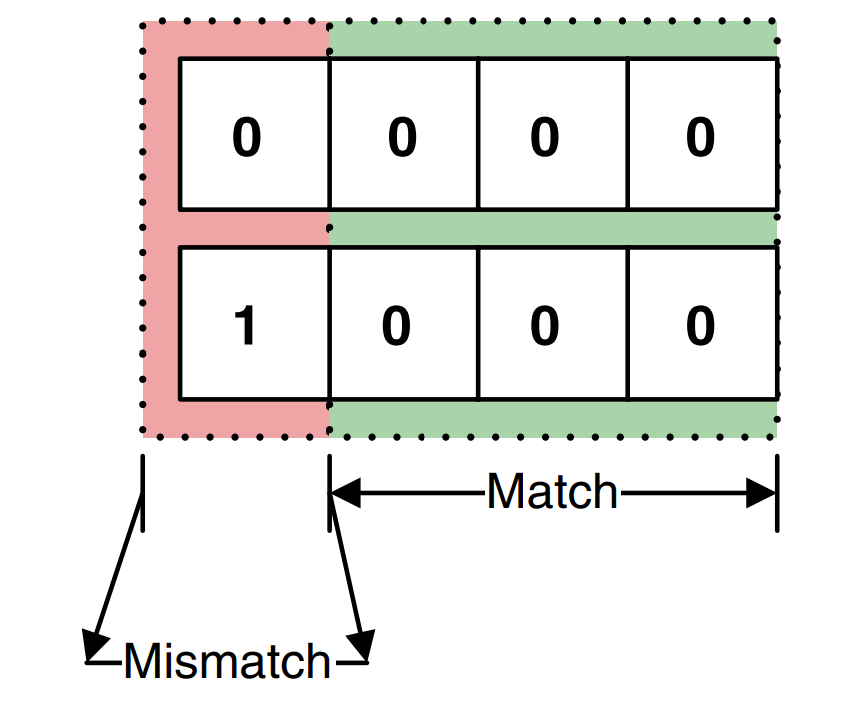

例如:考虑一个8深度的FIFO。需要三个位来寻址其所有八个位置,另外需要一个位来区分FIFO已满和FIFO空状态。最初,rd_ptr_bin和wr_ptr_bin均为“0000”,并且FIFO为空。现在,在对FIFO进行了八次后续写入之后,我们具有以下读取和写入指针值:

图2-9 FIFO满状况

图2-10 FIFO空状况

现在,在随后的八次读取中,读写指针具有以下值:

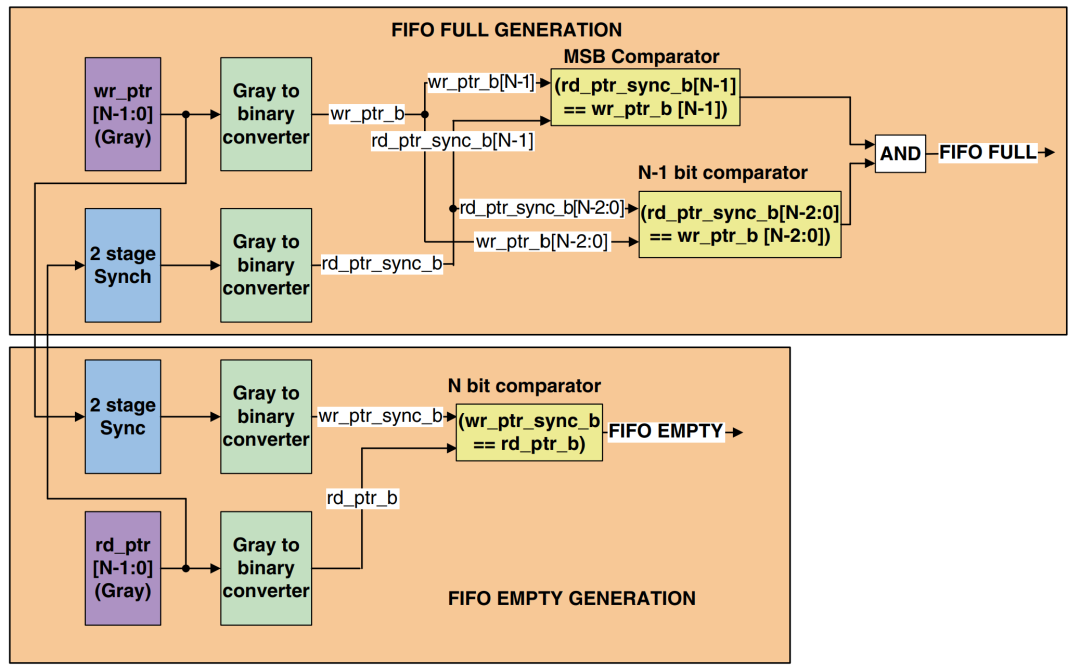

如图2-10所示,这是FIFO空状态。图2-11给出了显示FIFO空和FIFO满生成的框图:

在这种情况下,最大操作频率将取决于格雷码计数器的工作速度,因为它需要XOR门链。

由于“读/写”指针的值存储为格雷码,并且所有比较,指针的递增等均以二进制形式进行,因此实现和调试都非常简单。如图2-11所示,它需要四个格雷码到二进制转换器,如果直接用格雷码完成FIFO空和FIFO满生成的计算等比较,则可以避免。这有些复杂,并且需要一些其他逻辑。在下一部分中,让我们看看这种替代方法的工作原理。

2.4.1 FIFO满标志和FIFO空标志生成的另一种方法

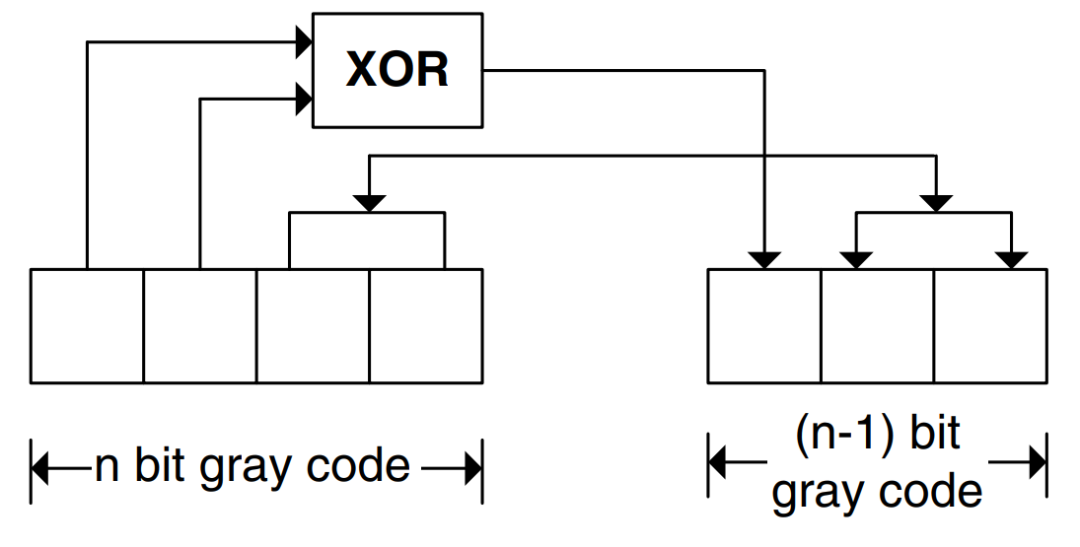

这种方法需要创建两个格雷码计数器,一个为n位,另一个为n-1位。可以通过单个n位计数器创建两个计数器,然后修改其第二个MSB以生成具有与n位计数器相同的LSB的(n-1)位格雷码计数器。

图2-11 FIFO满和空信号生成图

图2-12 四位的格雷码计数器

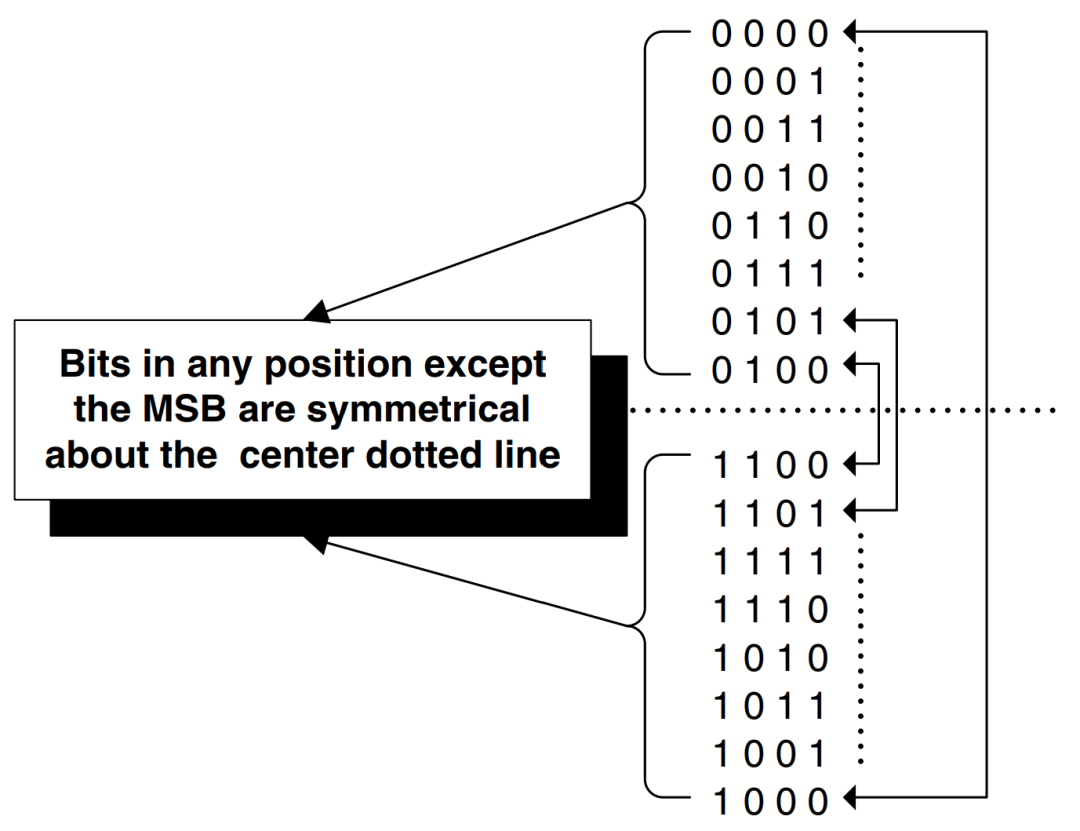

在开始主要逻辑之前,让我们先了解有关格雷码计数器的更多信息。图2-12显示了四位格雷码计数器。如上图所示,除MSB以外的任何列中的位均关于序列中点对称。因此,四位格雷码的后半部分是MSB反转后的前半部分的镜像。

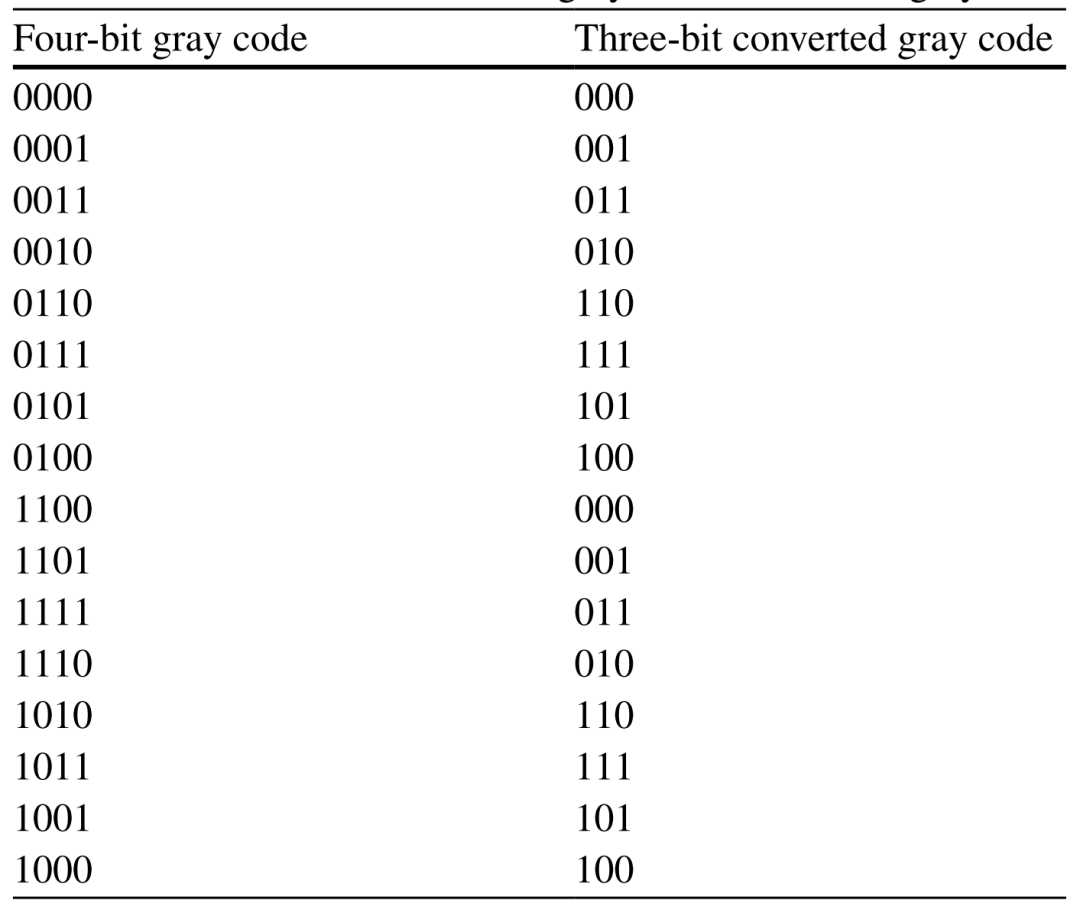

图2-13将四位格雷码转换为三位格雷码

下表是将四位格雷码转换为三位格雷码

现在,可以通过对n位格雷码的两个MSB进行XOR运算,轻松生成(n-1)位格雷码,以生成(n-1)位格雷码的MSB。其余(n-2)位可以简单地使用n位计数器的(n-2)位。图2-13显示了将4位格雷码转换为3位格雷码(上表)。此双n位格雷码计数器的用法FIFO空/满生成逻辑的逻辑将在下一部分FIFO设计中介绍。

2.5双时钟FIFO设计

图2-14显示了使用双端口存储器作为存储元件的FIFO的框图。

2-14 双时钟FIFO设计

2.5.1 FIFO空条件生成

当FIFO变空(即读指针与同步写指针匹配)时,将立即在读时钟域中生成FIFO空标志。2.4节中所示的实现。如果在比较之前首先将指针转换为它们的等效二进制数,则可以节省四个格雷到二进制的转换器。与先前的实现类似,指针比寻址FIFO存储器所需的指针大一位。将同步的写指针(wr_ptr_sync)与rd_gtemp(将在rd_ptr中注册的下一个格雷码)进行比较。下面是上述逻辑的Verilog代码:

always @ (posedge rclk or negedge reset_n)

begin: fifo_empty_gen

if (~reset_n)

fifo_empty <= 1’bl;

else

fifo_empty <= (rd_gtemp = = wr_ptr_sync);

end

2-15 FIFO空和满状况

2.5.2 FIFO满条件生成

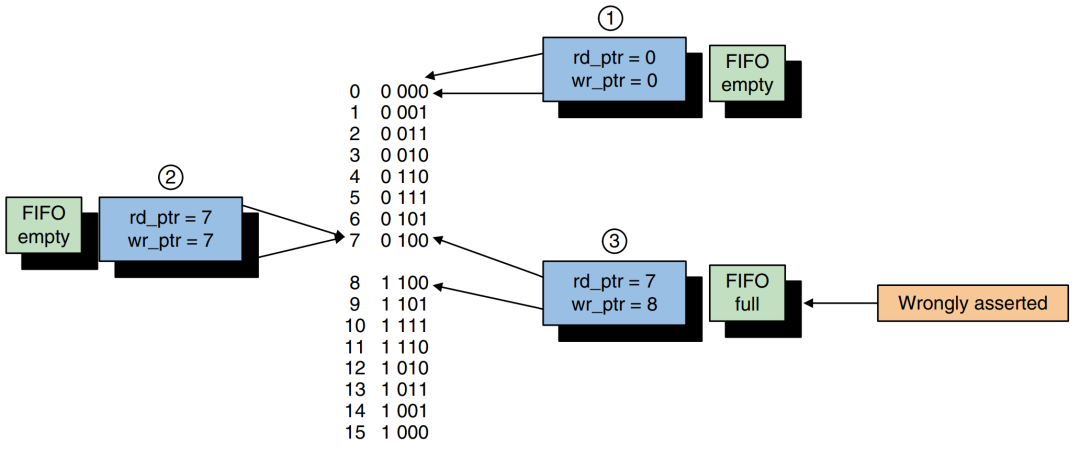

当FIFO变满时,即写指针与同步读指针匹配时,将立即在写时钟中生成FIFO满标志。请注意,写入指针和同步读取指针都直接用格雷码进行比较。与先前的实现类似,指针比寻址FIFO存储器所需的指针大一位。生成此条件的逻辑与以前的实现不同,因为指针比较直接以格雷码而不是二进制完成。让我们举一个例子。图2-15显示了在八深度FIFO上执行的步骤。

步骤1:最初,FIFO为空,“ rd ptr” =“ wr ptr” = 0,如图2-15所示。

步骤2:随后的写操作发生在FIFO上,直到FIFO变为“ rd ptr” = 0且“ wr ptr” = 7为止。如图3.35所示,“ rd ptr” =“ wr ptr” = 7,并且FIFO变空(因为读和写指针的所有位都相等)。

步骤3:此时一次写操作将导致“ rd ptr” = 7,“ write ptr” =8。如果使用与以前的实现(第2.4节)相同的逻辑,并且使用二进制比较,则FIFO将再次将其指示为“已满”,即使不是(图2-16)。

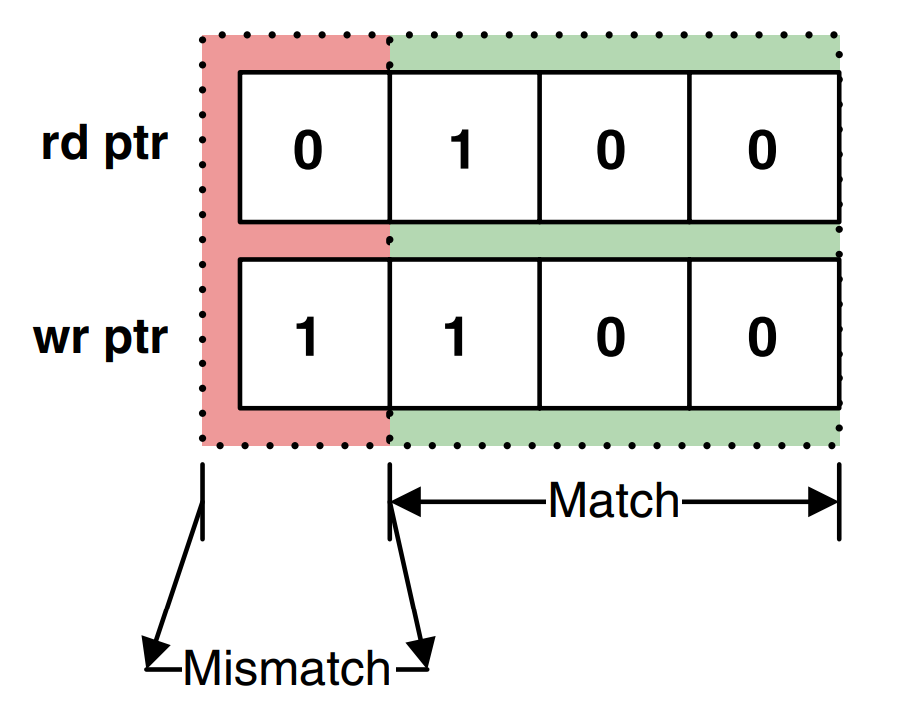

通过使用双n位格雷码计数器,可以轻松解决这种情况。通过将“ rd ptr”同步到写时钟域中,可以完成执行完全比较的正确方法。对MSB进行比较,并且在写指针比同步读指针多缠绕一圈的情况下,MSB应该有所不同。如果同步读指针的MSB为高,则在与(n − 1)位写指针进行比较之前,将同步读指针的第二个MSB(rd_ptr_sync)反转。

图2-16 FIFO满状况

因此,当以下三个条件全部成立时,将声明FIFO满标志:

1.同步读取指针(rd_ptr_sync)的MSB应该不同于将在wr_ptr中注册的写入指针(wr_gtemp)的下一个格雷码值的MSB。

2.写时钟域(wr_gtemp)中下一个格雷码计数的第二个MSB应等于已同步到写时钟域(rd_ptr_sync)中的读指针的第二个MSB。

3.两个指针中所有遗漏的LSB应该匹配。

注意:上面(2)中的第二个MSB是通过对指针的前两个MSB进行XOR运算而得出的。(如果两个MSB为高电平,则对其进行异或运算会使第二个MSB反转)。

下面是上面逻辑的Verilog代码:

wire rd_2nd _msb = rd_ptr_sync [SIZE] ^ rd_ptr_sync [SIZE - 1];

wire wr_2nd_msb = wr_gtemp [SIZE] ^ wr_gtemp [SIZE-1];

always @ (posedge wclk or negedge reset_n)

begin: fifo_full_gen

if (~reset_n)

fifo_full <= 1’b0;

else

fifo_full <= ((wr_gtemp [SIZE] != rd_ptr_sync[SIZE])

&&(rd_2nd_msb = = wr_2nd_msb) &&(wr_gtemp[SIZE -2:0]

= = rd_ptr_sync[SIZE-2:0]));

end翻译/摘自:硬件架构的艺术(英文原版),有部分加工,供参考学习。

译者:亦安

转自公众号:AriesOpenFPGA

本文内容仅代表作者观点,不代表平台观点。

如有任何异议,欢迎联系我们。