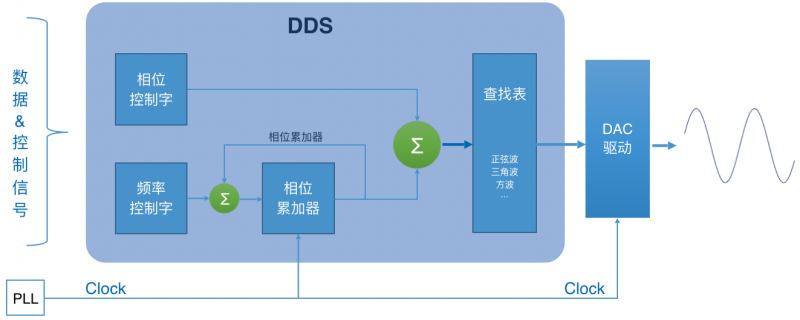

在每届的电赛中,DDS/信号产生是个必备的技能和训练,因为几乎每届的题目中都有涉及,DDS的构成无外乎两种方式:

购买现有的DDS芯片,搭配一个单片机来做参数配置,DDS芯片一般都会选用ADI公司的器件;

通过FPGA + 高速DAC实现,FPGA不仅可以非常灵活地用来产生DDS需要的数字逻辑,还可以做更多的控制。

用FPGA来实现所有的数字逻辑和存储功能

注:除了上图中的功能,按键输入控制和参数的输出显示乃至菜单,也都可以通过FPGA来实现

看电赛交流群里同学们的讨论,即便高速DAC也已经拼到50MHz的模拟信号,12位的DAC精度(其实没有必要这么高精度,10位足够)。要产生如此高频率的模拟信号,要让波形看起来不错,高速DAC的转换率至少也要200Msps以上(即便如此一个周期才4个采样点)。当然FPGA是没有压力的,小脚丫FPGA的任意一款都可以通过内部的PLL轻松达到400MHz。

今年比较特殊,很多元器件都很难买到,即便买到也有假货的风险,尤其是高速的DDS芯片、高速的DAC器件。

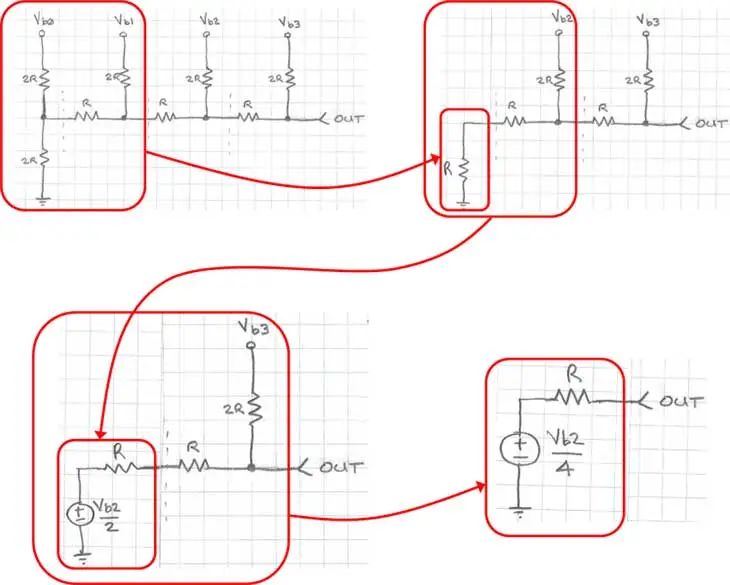

其实用R-2R做DAC可以用非常低的代价(两种阻值的电阻,总成本不到1元RMB)实现非常高的性能,即便你搭建一个12位的高速DAC,也仅需要24颗电阻,DAC的速度?轻松飙到400Msps,虽然会有一些性能上的折扣,但如果搞清楚了R-2R和商用DAC的区别,避开R-2R存在的问题,这自然是一种价廉物美的实现方式,足以满足电赛的要求。

下图就是R-2R的工作原理,网上有很多文章,在此不再赘述。

R-2R DAC的工作原理

R-2R DAC和商用DAC主要的两点区别(以10位的DAC为例):

基于上述的差异,在使用R-2R中要注意以下的几个问题:

要使用SMD封装的电阻,比如0603、0402的;

我们平常使用的大多数是5%精度的电阻,阻值的偏差会导致生成的波形上某些地方”起包“或“有坑”,影响了波形的美观,尤其是权重比较高的电阻对波形的影响会更大,选用1%精度的电阻会让波形变得更加“光滑”,即便如此,你也可以用万用表更精准地细挑一下,比如你需要1K和2K的电阻,1%精度的1K电阻也会有990欧姆到1010欧姆的差异,你可以通过挑选选出更接近1000欧姆的电阻,比如999和1001之间的,效果会更好,毕竟100只电阻才不到1块钱;

没有了同步时钟,自然要尽可能保证每个数据线从源端到电阻的节点处是等延时的,也就是说你在PCB布线的时候尽量做到每个数据线的长度相等、FPGA内部做时序约束,让送到DAC的10根数据线内部的延时一致;

有了高速DAC,如何通过FPGA的逻辑编程实现DDS/信号源的功能?可以扫描下面的二维码到相应的资源页面,会点击左下角的“阅读原文”跳转。

DDS生成任意波形的方法及Verilog代码示例

与电赛相关的更多资源,可以扫面下面的二维码。