LTCC技术是诞生于上世纪80年代的多层电路技术,其首先采用生瓷粉料通过流延形成生瓷带,然后在各层生瓷带进行冲孔、通孔金属浆料填充、电路图形印刷、电阻印刷,最后将各层生瓷片对位叠层、压合后在850℃~900℃的温度下烧结为一体,形成多层陶瓷电路。LTCC技术以其特有的技术特点广泛应用于射频电路系统。

LTCC多层电路基板制造工艺流程较长,工艺复杂,基板收缩率、翘曲度、层间对位精度等都是影响产品性能的重要因素。本文针对上述技术难点开展研究,并阐述了如何优化工艺参数以解决上述问题。通过大量的工艺试验和数据测试,结果表明,新的工艺方案可有效解决这些工艺问题。

三大影响因素分析

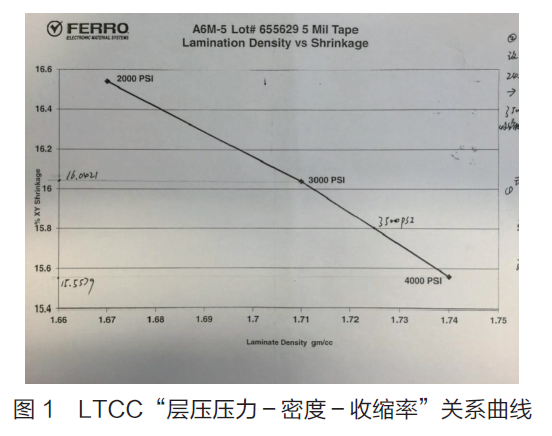

1、收缩率偏差

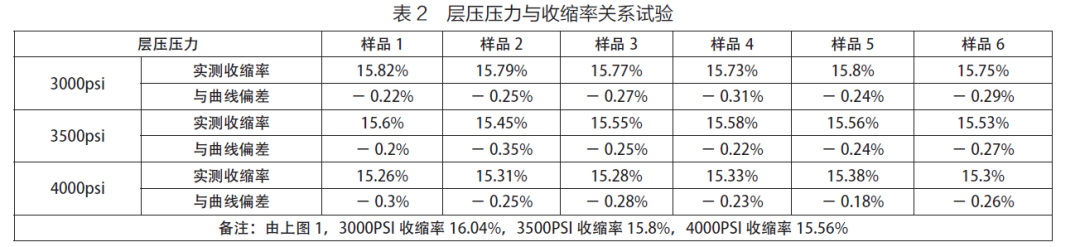

LTCC收缩率与其密度有直接关系,密度越大收缩率越小,密度越小收缩率越大,反应到工艺参数上来,密度与层压压力相对应,因此可以通过调控层压压力来改变LTCC产品的收缩率,使之达到设计要求,如下图1所示是LTCC材料厂商提供的本批次材料“层压压力-密度-收缩率”关系曲线。

2、基板翘曲

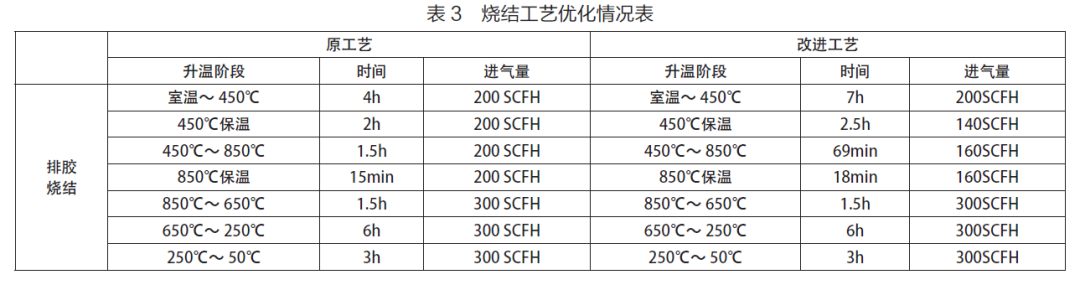

(1)烧结原因:烧结工艺与基板翘曲度、收缩率有直接关系,LTCC基板的烧结过程实际是一个放热吸热反应的过程。排胶阶段(室温至500℃左右)基板中有机物分解挥发,质量减轻;烧结阶段(700℃~850℃左右)基板发生结晶和析晶反应,伴随反应的进行,基板收缩。因此低温阶段、高温阶段的烧结时间,升温速率与基板收缩程度、翘曲程度关系密切,需要优化烧结曲线,通过试验调整排胶阶段升温速率、时间,烧结阶段升温速率、时间,各阶段空气流量等重要工艺参数。

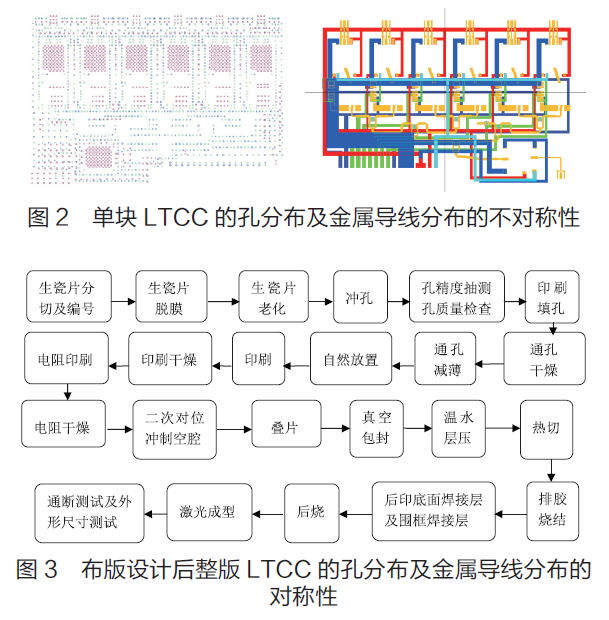

(2)基板结构及金属分布问题:LTCC 基板的结构也是决定LTCC 基板烧结翘曲度的关键因素,当LTCC 基板上存在多种规格的空腔结构时,其结构难以均衡对称,同时由于LTCC 基板上含有大量通孔及密集金属导线,这些都难以均匀分布,这样就容易导致其翘曲度超差。

(3)浆料选用问题:不同银浆、金浆与生瓷带热膨胀系数匹配性不同,因此大面积印刷层选用不同浆料时对基板翘曲度的影响尤为明显。

3、通孔层间对位偏差

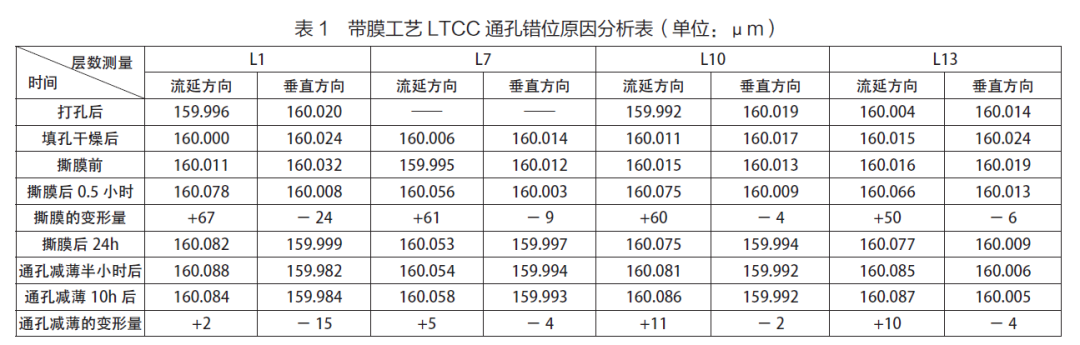

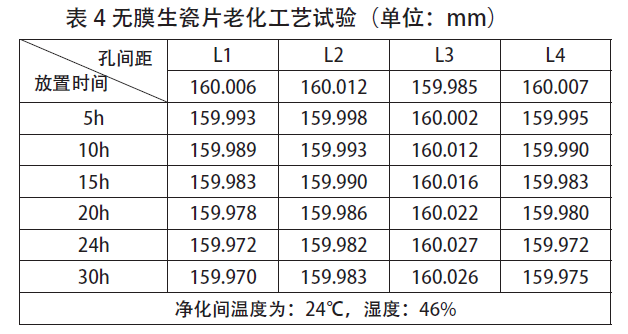

LTCC 基板层间对位偏差与打孔精度、生瓷片自身收缩情况、各层印刷导体情况,叠层对位精度等众多因素相关,是控制的难点,因此需要对整个工艺流程进行监控,找出主要影响因素,进行优化控制。按照带膜工艺流程进行LTCC制造,对全过程进行错位监控,具体如表1所示:

本轮试验通过全流程跟踪监测,由表1数据可知,带膜生瓷片在撕膜后会有一个应力的释放,导致较大变形,其中主要形变方向为生瓷流延方向,表现为放大,范围约为40μm~70μm,垂直于流延方向则表现为收缩,范围约为10μm~20μm,是带膜工艺通孔错位的主要原因。

工艺方案及试验结果

1、收缩率偏差控制工艺方案

为了寻求实际收缩率与曲线上收缩率的误差,如下所示是开展了多批次不同层压压力下实际收缩率测试实验。

2、基板翘曲度控制工艺方案

(1)烧结工艺优化:降低排胶阶段升温速率,优化各阶段气流量,缓解不同材料热膨胀系数不匹配的应力 。

按照上述方案进行工艺优化后,将生产的LTCC基板进行了基板外形尺寸及翘曲度测试,测试表明,通过上述改进,基板外形尺寸精度及翘曲度指标完全满足过艺要求,改进效果明显,基板本身及空腔底面平整度均达到了较好效果,基板均达到小于2‰的翘曲度。

3、通孔层间对位偏差控制

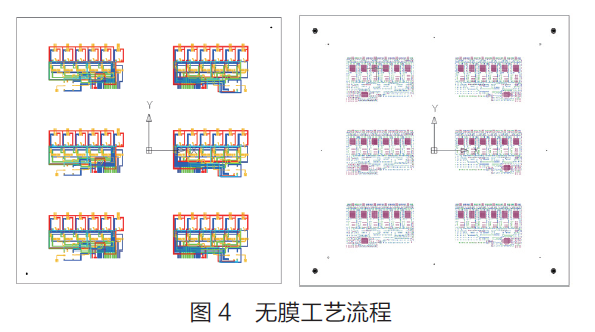

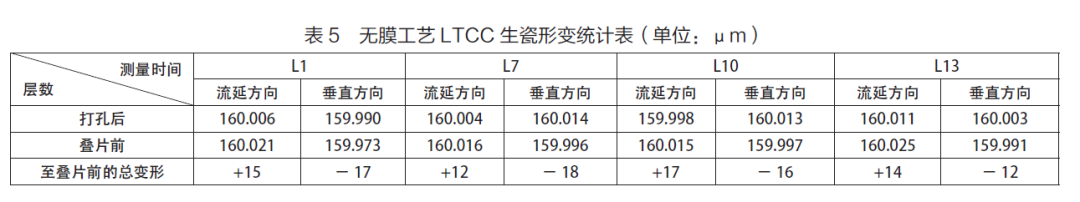

带膜工艺,在叠片前撕膜,生瓷片在流延是积累的应力在撕膜时集中释放,造成生瓷片无规律性变形,引起生瓷片上通孔及导线位置偏移。改为无膜工艺,在打孔前对生瓷片进行撕膜、自然放置老化处理,以释放应力;更改后工艺流程如下图4所示,该此工艺流程瓷片叠片前形变如表5所示。

表5测试数据表明,无膜工艺流程下打孔后至叠片前,打孔、填孔、印刷、浆料干燥等工序操作造成的生瓷片形变约在+15μm左右,完全满足工艺要求,该工艺流程下填孔层间对位偏差将得以改善。

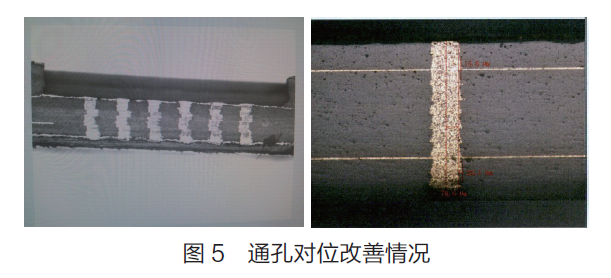

采用上述方案后,改进后通孔对位精度明显提高,达到≤40μm水平,如图5所示。

从上述试验可知,实际LTCC基板由于存在金属通孔、印刷金属导线,这些金属的收缩率不同于白瓷收缩率,因此相同层压压力下LTCC产品的收缩率与白瓷的收缩率有一定差异,可通过积累工艺数据,进行层压压力相应的调整来解决收缩率偏差问题。对于LTCC基板烧结收缩率,其不仅与烧结工艺有关,还与基板对称性设计、电路布局、浆料选用关系密切;带膜工艺较无膜工艺在通孔层间对位精度控制上难度更大,撕膜时应力释放是导致层间通孔对位偏差的主要原因,无膜工艺更适合层间对位精度要求较高的应用。

文章来源:LTCC基板关键工艺问题解决方案 贾耀平 中国电科集团公司第十研究所

|推荐阅读|

如何正确校准网络分析仪及S参数测量

怎样正确使用1/4波长线代替一级电感

© 滤波器 微信公众号