台积电最近在VLSI 研讨会上展示了其对片上水冷的研究,作为解决散热问题的一种方法。它涉及将水道直接集成到芯片的设计中。

首先,我们应该问自己为什么可能需要在芯片内部或芯片上进行直接水冷。像NVIDIA的A100加速器这样的芯片,连同HBM2E和作为SXM4模块,已经有高达500W的废热。对于英特尔的Xe-HPC芯片Ponte Vecchio来说,甚至还有高达600W的余热。因此,尽管采用现代制造技术,冷却此类芯片变得越来越困难。水冷在数据中心区域没有什么特别之处。冷却器安装在处理器和加速器上,去除废热。但即使芯片的面积有几百平方毫米,在这么小的面积上产生400+W范围的废热也不容易处理。

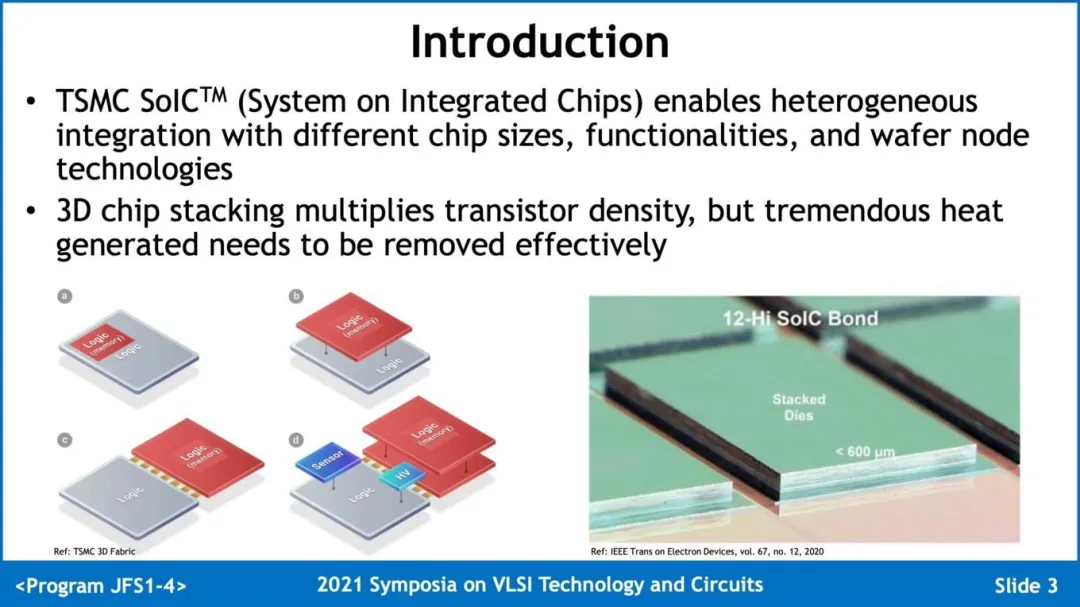

此外,未来将越来越多地使用具有3D集成的芯片。 从 2021 年底/2022 年初开始,AMD 将使用 3D V-Cache 作为处理器的附加 SRAM。额外的缓存直接位于现有的 L3 缓存之上,而不是位于 Zen 3 核心之上,这将使冷却它们变得更加困难。但 3D 堆叠不会就此止步;越来越复杂的连接正在计划中。如果您不想在 X 和 Y 方向完全扩展它们,就像 Ponte Vecchio 的情况,那么在较低层堆叠和冷却芯片变得越来越重要。

台积电的研究人员认为解决方案是让水在夹层电路之间流动。这是一个非常简单的理论解决方案,但对于电子产品而言,这是一项极其困难的工程壮举。

数学很简单:当前的冷却解决方案通常通过与给定芯片的散热器直接接触、直接芯片接触技术或完全浸没在非导电流体中来工作。其中,前两种解决方案只能有效地冷却它们直接接触的层,这给垂直芯片堆叠带来了巨大的问题。较低的层在散热方面会遇到更多困难,会造成损坏或不得不节流,这两种情况都会对性能不利。

不仅如此,由于必须将整个封装的热量传递到散热层,芯片的顶层还会增加压力。液体浸没虽然效率高且可能更适合堆叠芯片,但成本昂贵且难以部署在已经适合空气或传统水冷的专业场景中。

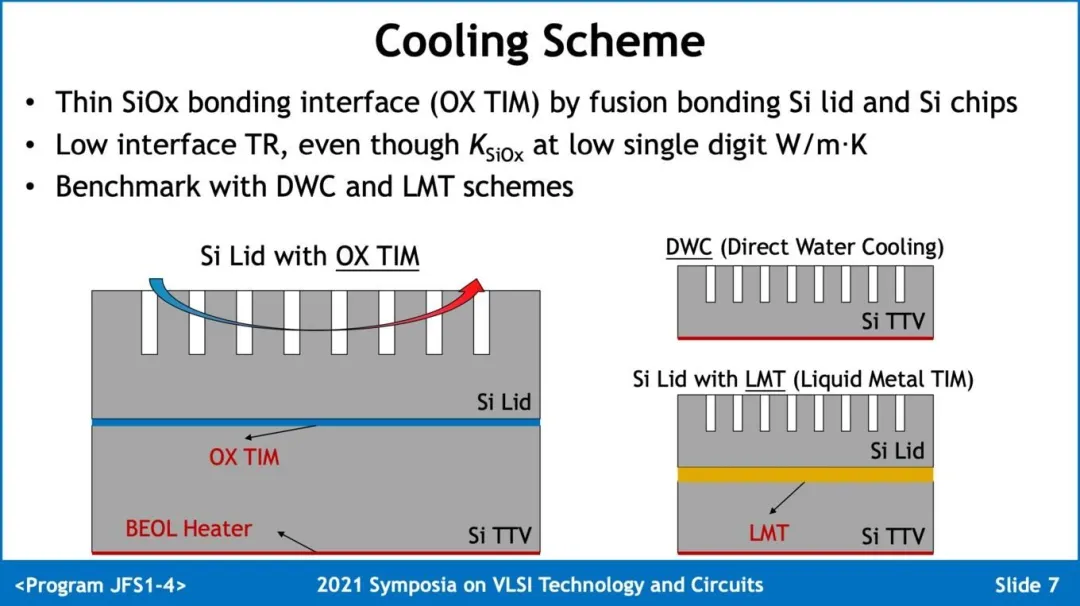

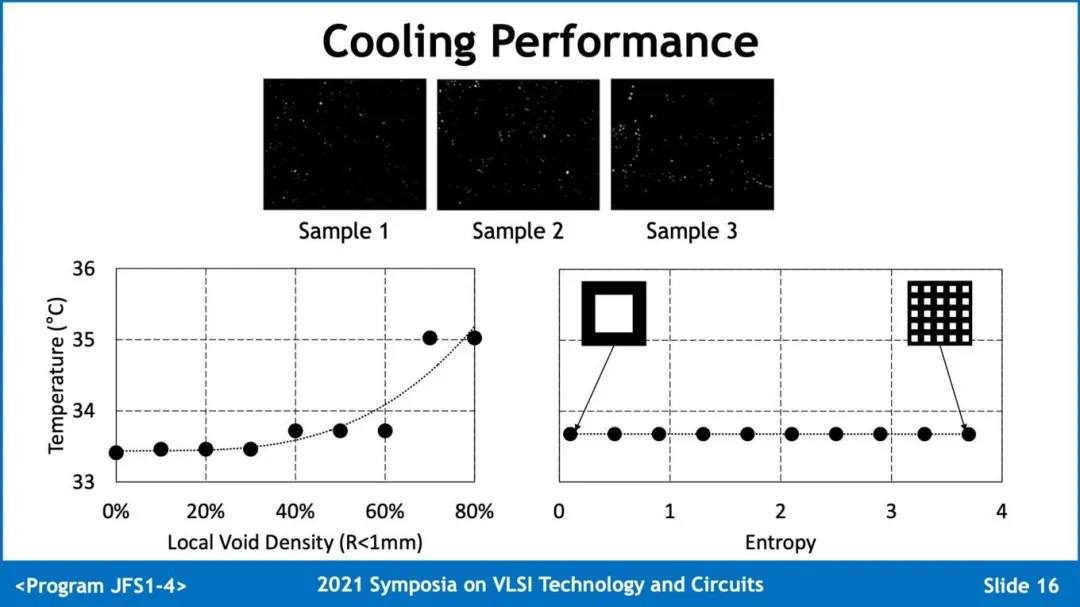

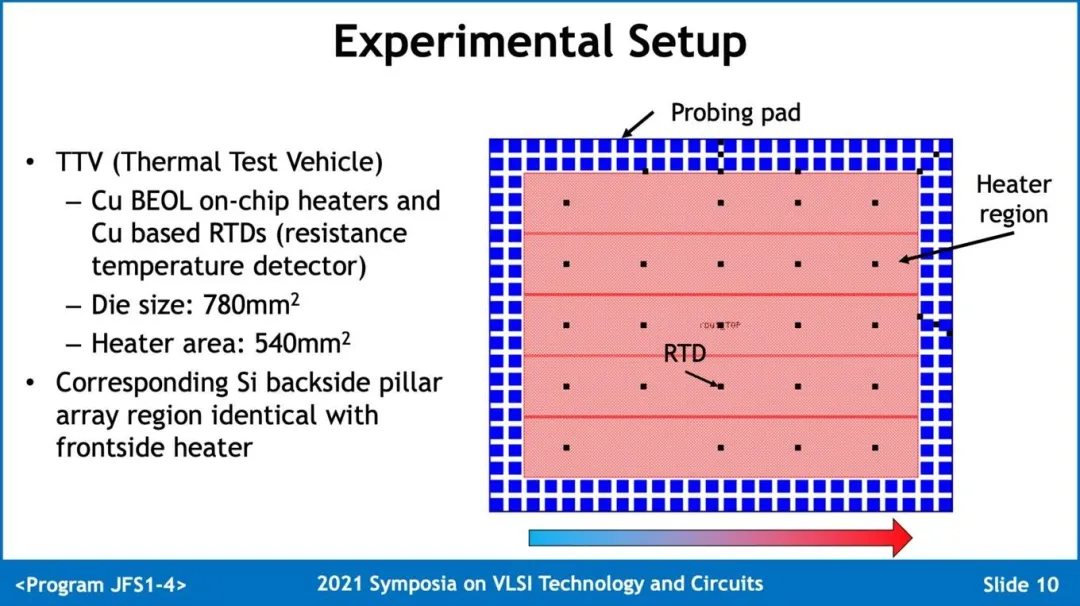

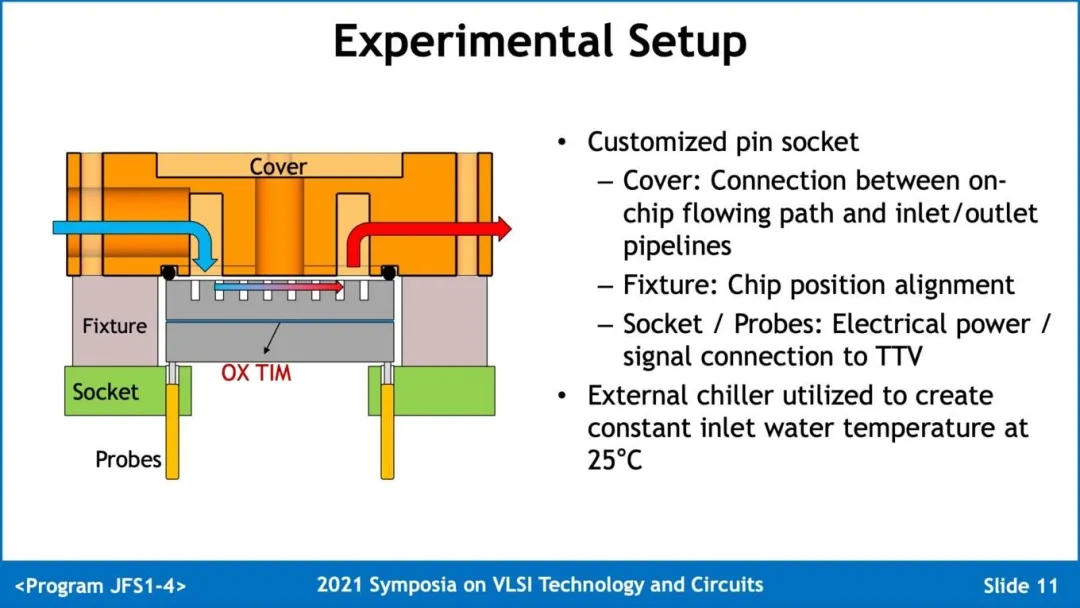

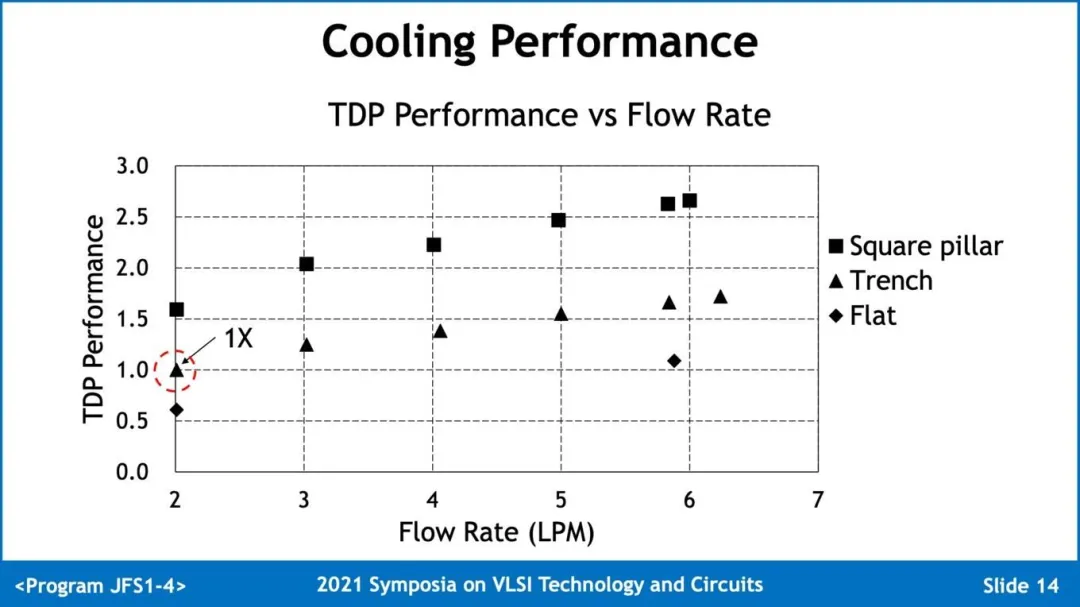

台积电在受控实验室条件下对虚拟半导体进行了测试——一种热测试载体 (TTV),它本质上是一种由铜制成的加热元件。该公司在受控条件下测试了三种类型的硅水通道集成:它使用基于柱的通道,水可以在有源半导体柱周围流动以冷却它们(想想岛屿周围的水);以沟渠设计为特色的设计(想象一条河流,由其海岸控制);以及位于硅芯片其余部分的简单平坦的水道。水通过一个外部冷却机制,从它通过硅芯片的过程中将水冷却到 25 ºC。

为了将通道加工到硅中,使用了一种技术,该技术也用于从晶片上切割芯片。金刚石锯可切割 200 至 210 µm 宽和 400 µm 深的通道。对于 300 mm 晶片,硅层的厚度为 750 µm。该层当然应该尽可能薄,以简化来自下方有源芯片的热传递。台积电还测试了一个方向的通道是否足够,或者方柱(即横截面和纵向截面)是否提供最好的散热。还测试了没有通道的简单平面。

TV(Thermal Test Vehicle)由铜制加热元件组成。加热元件本身有温度传感器。加热元件的表面为 540 mm²,TTV 的总面积为 780 mm²。TTV 在它自己的基地中被拉伸,这使得电力供应、供水和排放以及传感器的连接成为可能。在25°C的恒温下引入水。

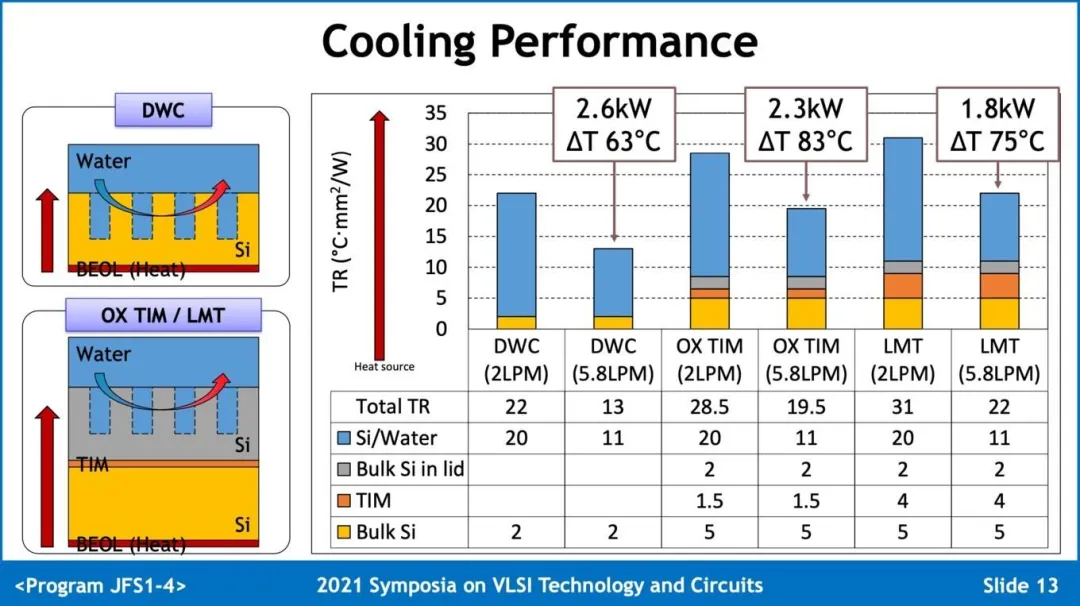

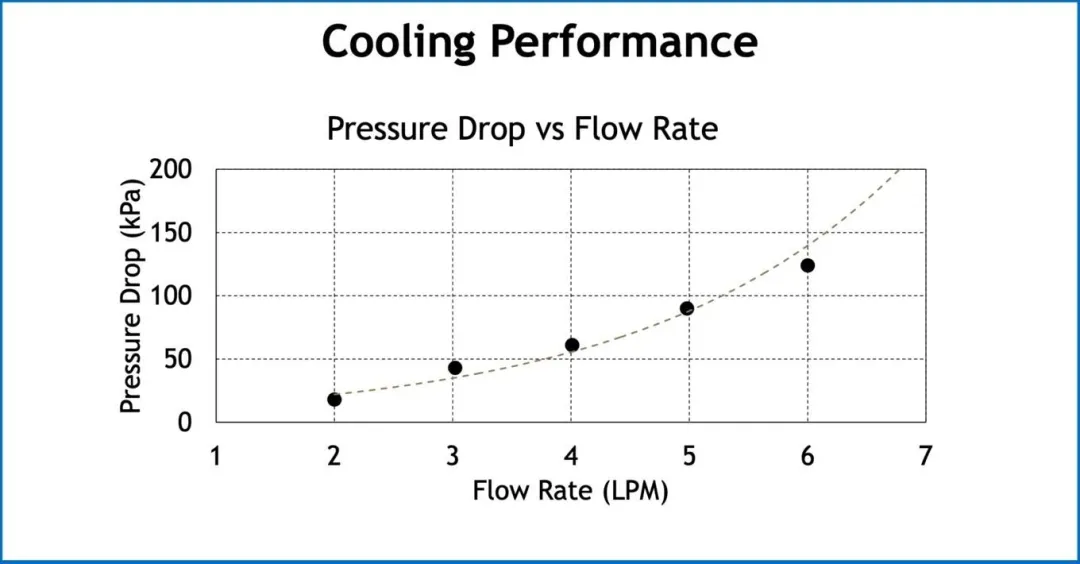

对于直接水冷,即芯片本身存在冷却,台积电设法散发 2.6 kW 的废热。温差为 63°C。芯片与硅层之间采用OX TIM水冷连接,台积电可以散掉2.3kW的废热,温差为83°C。两层之间的液态金属仅能去除 1.8 kW 和 75°C 的温差。台积电还测试了两种流速——一种是每分钟 2 升,一种是每分钟 5.8 升。然而,关于废热和温差的信息仅为每分钟 5.8 升,因为这是获得可行值的唯一方法。

热阻应尽可能低。台积电还确定了传热的最大障碍在哪里。对于 DWC,只有硅和水之间的过渡是最大的困难。如果使用单独的电平,这里还有另一个过渡,最好通过 OX 连接来解决。

台积电为此对三种不同的硅水道做了相关的模拟试验,一种是直接水冷方法,水有自己的循环通道直接蚀刻到芯片的硅片中;另一种是水通道蚀刻到芯片顶部硅层,使用 OX(氧化硅融合)的热界面材料(TIM)层将热量从芯片传递到水冷层;最后是一种将热界面材料层换成简单便宜的液态金属.

声明:

投稿/招聘/推广/宣传 请加微信:15989459034