为满足数据处理速度越来越高的需求,工艺节点逐渐变小。而提高产品良率不仅是代工厂的责任,同时设计阶段也应加以应对可能存在的制造风险。机器学习作为一种实现AI的方法,也在帮助应对先进制程的新挑战。从不同的方向提供各种应用模式,帮助产品设计者改善设计,提高良率。

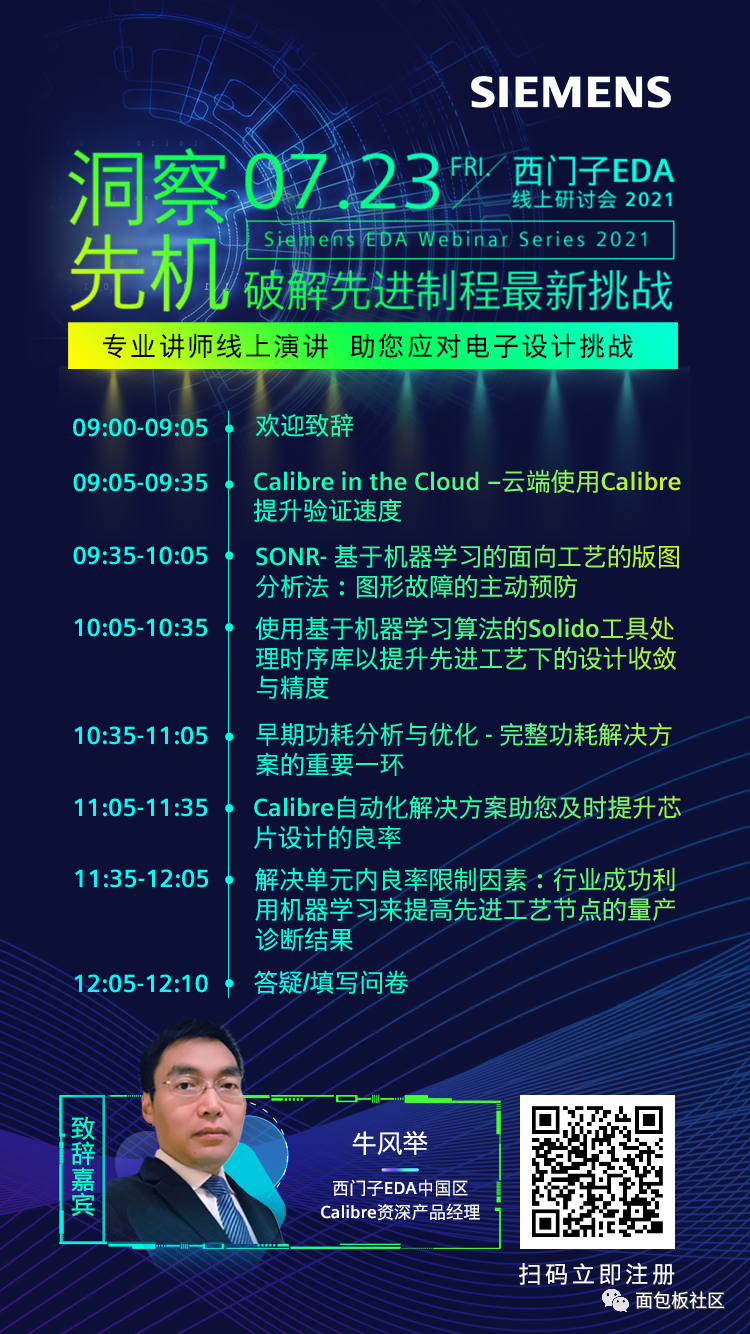

西门子“洞察先机破解先进制程最新挑战”线上研讨会即将在7月23日为您精彩呈现。【报名参加研讨会即可参与送纸质书活动】

活动规则:按照报名排序抹黑抢书:末尾逢5为书籍获得者。(即5、15、25以此类推,奖励10位)

👇扫码报名

👇下载EDA资料

新时代下的EDA工具

西门子 EDA 在如何破解先进制程最新挑战方面,不只是Calibre一个产品线的与时俱进,同样在Design Creation方面有优化功耗的PowerPro产品,在library cell 优化方面有优化标准单元库性能的Solido产品,在Design -for-Test方面有更高压缩倍数的Testkompress SSN产品,以及能够做到Cell - Aware - Diagnosis的RCAD产品Tessent Diagnosis。

图形故障的主动预防

引入一个全新的基于设计特征的机器学习工具 SONR,可根据图形在晶片上的曝光行为进行设计分析,这种新的方法在处理大量图形时,比传统的基于几何形状的图形匹配方法更高效且更有效。SONR 可以应用于许多不同的领域,包括在测试掩模改进中进行版图分析以及在闭环DFM 中预测潜在的风险图形。在本次讲座中,将介绍仅依据设计端的版图信息而未获得制造端信息的前提下,从不同的方向提供各种应用模式,以帮助产品设计者改善设计,提高良率。

提升先进工艺下的设计收敛与精度

由于更低的电源电压和更高的时钟频率在先进工艺节点(例如 16nm/12nm 及更小的线宽)上很常见,因此设计裕量大幅缩小。Liberty 模型的特征提取精度必须比过去更加精确。此外,设计还必须应对新的挑战,例如库单元数量增加、对更多工艺、电压、温度 (PVT) 极端情况的覆盖要求,以及表现为Liberty偏差格式 (LVF) 的精细偏差模型。所有这些新的考虑因素都大幅增加了针对时序库特征提取的 SPICE 仿真需求。如果不能对所有 .lib 数据实现充分的验证覆盖,设计团队将会面临更高的设计流片延迟和潜在芯片故障风险。

在此研讨会中,将介绍 Solido Characterization Suite 如何利用机器学习将时序库特征提取的速度相对 SPICE 提升 100 倍,同时提供全面的 .lib 验证。

早期功耗分析与优化

功耗在设计周期的早期受到的影响最大。PowerPro 的早期功耗检查功能无需输入激励,便可帮助识别 RTL 级别的触发器、存储器和 CGIC 相关设计中存在的功能和结构冗余。

PowerPro 的功耗检查功能非常适合回归测试,通过此测试,可以在 RTL 设计的早期阶段找出电源问题并迅速加以解决。

自动化解决方案及时提升设计良率

在前沿工艺节点,图形填充不仅有助于缓解制造方面的额外问题,例如制造应力,还有助于减少由蚀刻、光刻和快速热退火造成的各种误差。此外,随着芯片尺寸的增大以及图形间距和特征尺寸的缩小,需要使用新的填充形状,以确保开放区域可以被有效填充,且仍然符合 DRC 的要求。填充区域和填充形状数量的增加已经导致设计中使用的填充量呈指数增长。

Calibre YieldEnhancer 版图修改平台为设计人员提供了各种自动化解决方案。本次研讨会描述了填充管理和数据库控制所需的新策略,以确保设计过程易于管理,填充流程始终有效,并且对进度的影响最小。

提高先进工艺节点的量产诊断结果

半导体制造商长期依靠扫描测试和诊断,协助进行失效分析并解决良率问题。随着设计变得更加复杂,失效隔离技术遭遇挑战,提高诊断分辨率以应对单元内部问题,成为缩短生产预备时间的首要任务。

将 Tessent YieldInsight 的机器学习与单元感知 Tessent Diagnosis 相结合,可以利用大量的扫描数据准确地掌握先进工艺节点关键良率制约因素的根本原因。非监督式机器学习技术 — 根本原因反卷积 (RCD) 可以找出最有可能的缺陷分布并消除低概率怀疑点,从而提高分辨率和准确性。