1981年,加州大学伯克利分校的一个研究团队起草了RISC-1,这就是今天RISC架构的基础。RISC-1原型芯片有44500个晶体管,拥有31条指令。包含78个32位寄存器,分为6个窗口,每个窗口包含14个寄存器,另外还有18个全局变量,寄存器占用大部分面积,控制和指令只占用芯片面积的6%,而同时代的芯片设计里要占用约50%的面积。

随后在1983年发布了RISC-II原型芯片,包含138个寄存器,分为8个窗口,每个窗口有16个寄存器,另外还有10个全局变量,但是只有39000个晶体管。接着在1984年和1988年发布了RISC-III和RISC-IV。

2010年,Patterson教授的研究团队准备启动一个新项目,需要设计CPU,因而要选择一种指令集。他们调研了包括arm、MIPS、SPARC、X86等多个指令集,发现它们不仅设计越来越复杂,而且还存在知识产权问题。

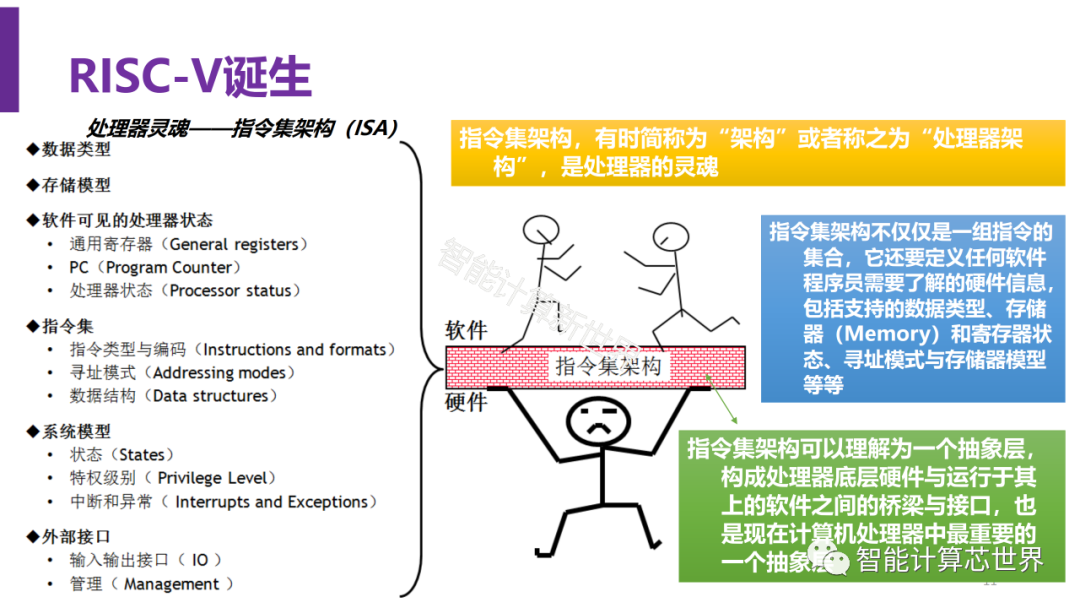

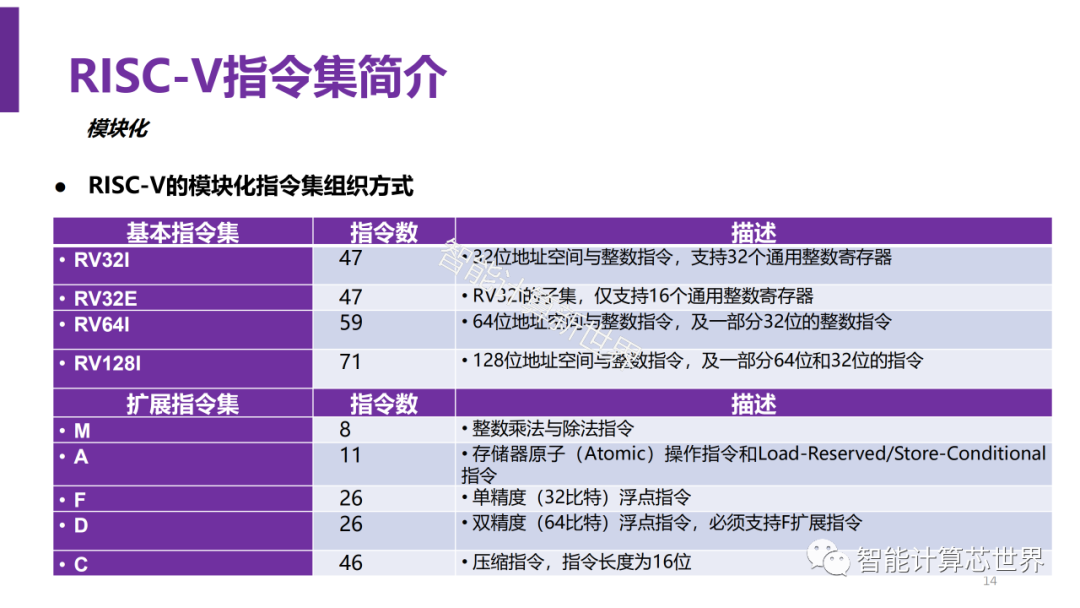

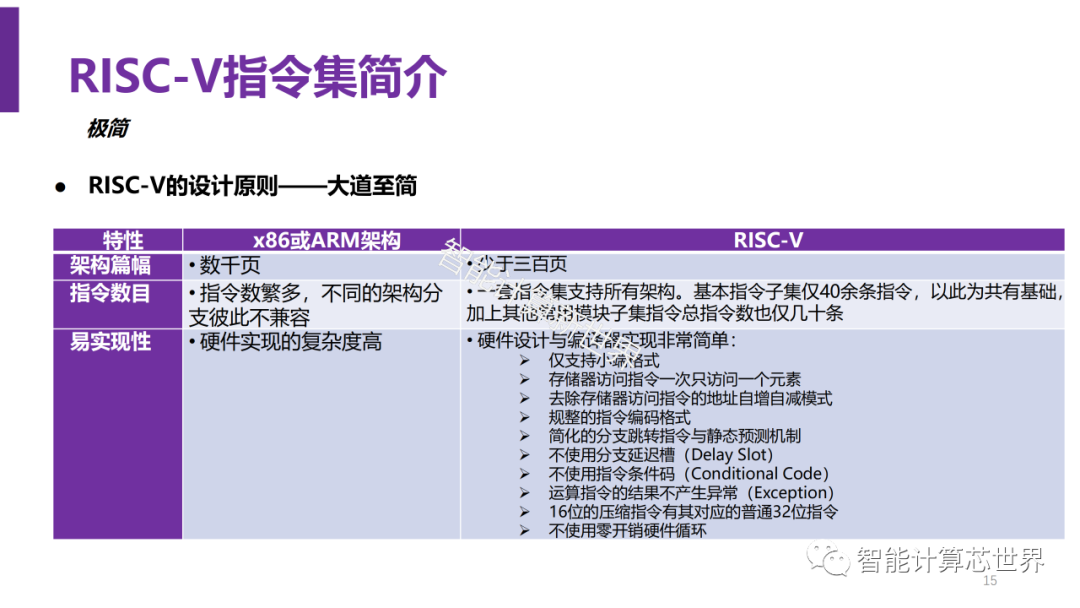

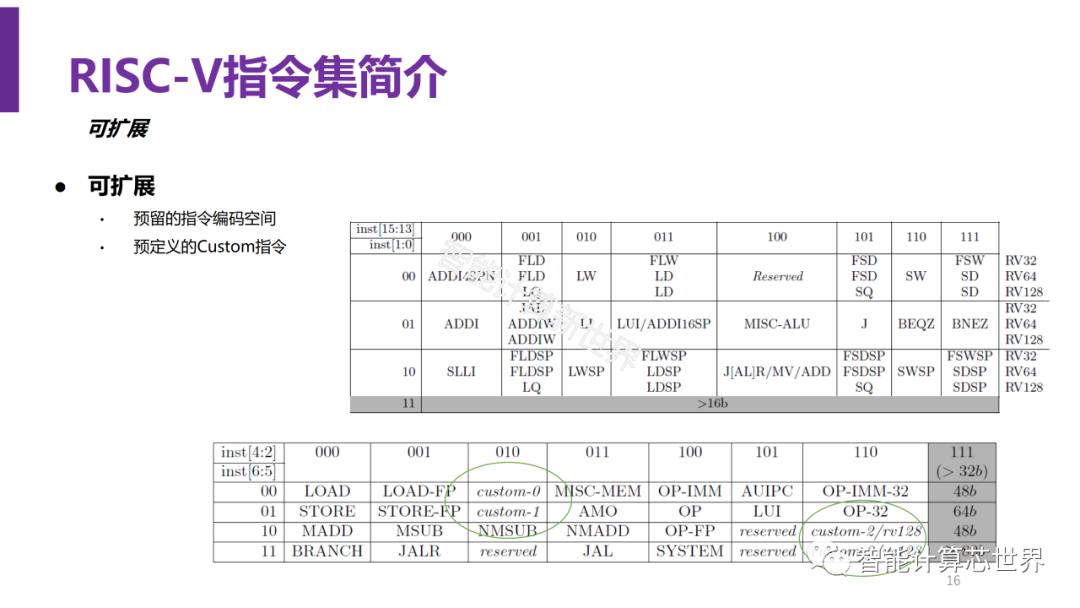

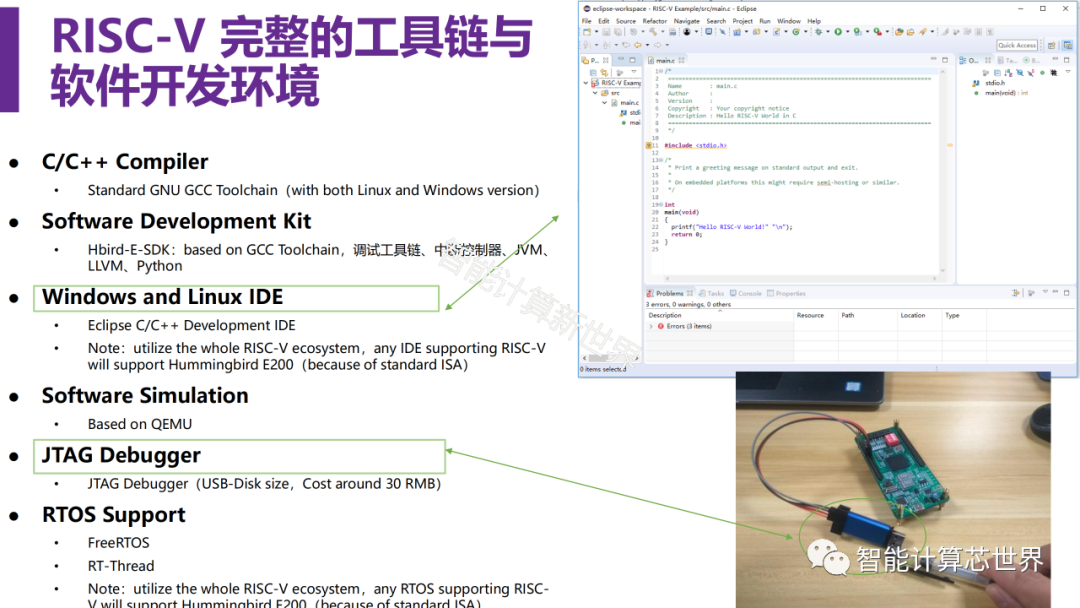

RISC-V(第五代精简指令集)是David Patterson教授基于其30多年在精简指令集RISC领域的深入积累,在2010年到2014年期间带领团队研发出的最新一代CPU芯片设计指令集。RISC-V是基于精简指令集计算(RISC)原理建立的开放指令集架构(ISA),RISC-V是在指令集不断发展和成熟的基础上建立的全新指令。RISC-V指令集完全开源、设计简单、易于移植Linix系统,采用模块化设计,拥有完整工具链。

下载链接:开源RISC-V设计与实现

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

下载链接:开源RISC-V设计与实现

深度报告:RISC-V异构IoT全新架构

面向AIoT的RISC-V原生操作系统研究

玄铁C910实现RISC-V用户自定义指令

龙芯LoongArch指令集全集

人工智能核心技术产业白皮书(2021)

中国高性能计算挑战与进展

高性能深度学习计算框架

超级计算机研究报告

阿里云弹性高性能计算

中国高性能计算挑战与进展

高性能深度学习计算框架

超级计算机研究报告

深度报告:GPU研究框架

基于CPU/GPU异构量子高性能计算

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

电子书<服务器基础知识全解(终极版)>更新完毕,知识点深度讲解,提供182页完整版下载。

获取方式:点击“阅读原文”即可查看PPT可编辑版本和PDF阅读版本详情。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。