导 读

总 结

通过和 Intel 院士Johanna Swan的深入交流和沟通,我们可以得出以下几点结论:

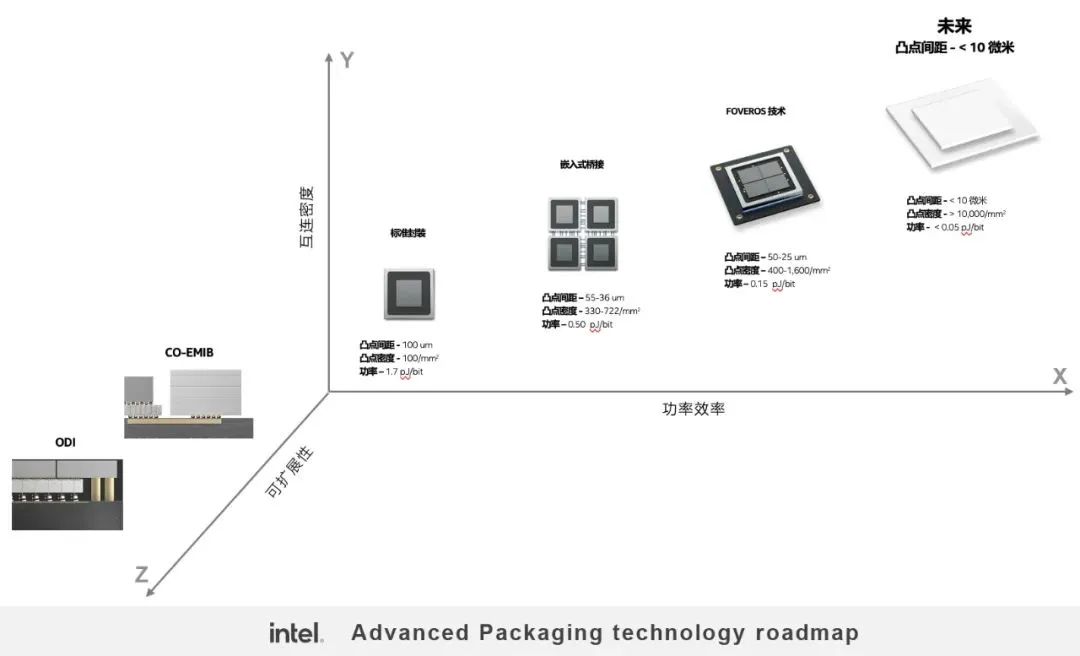

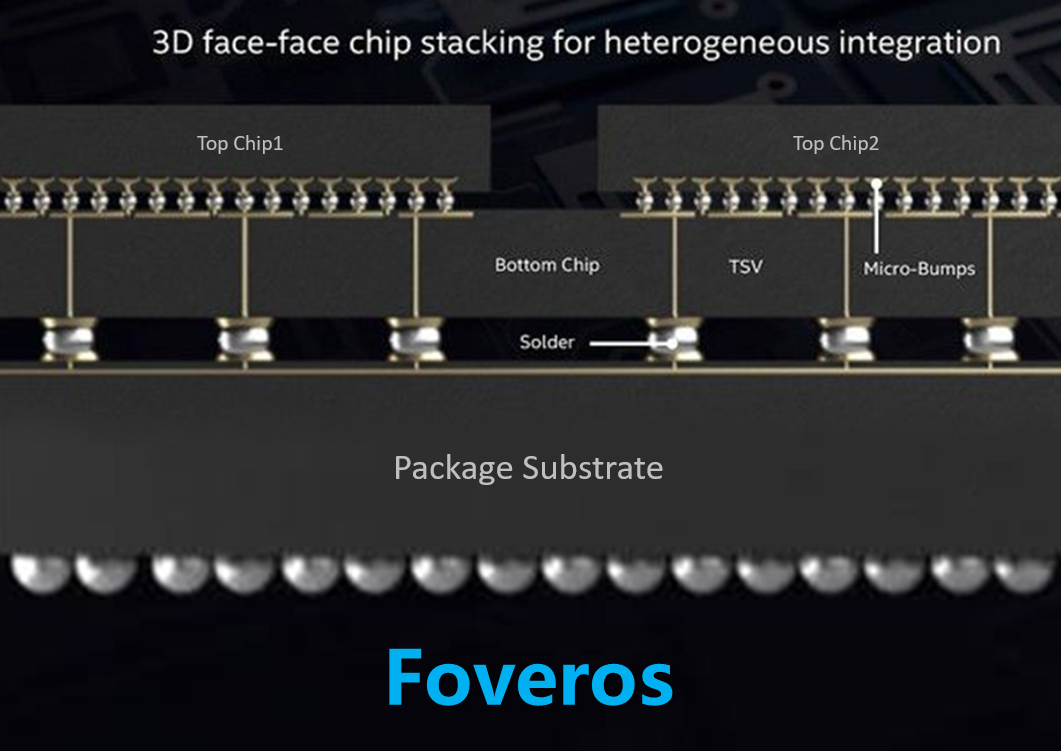

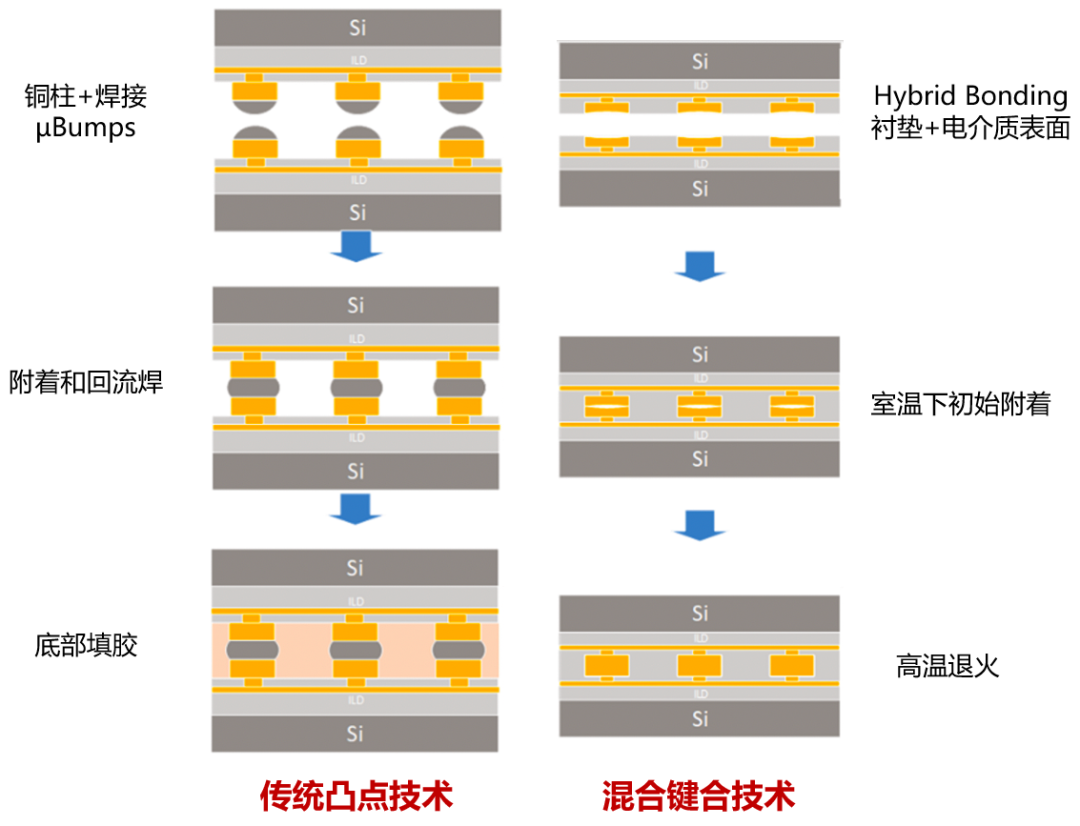

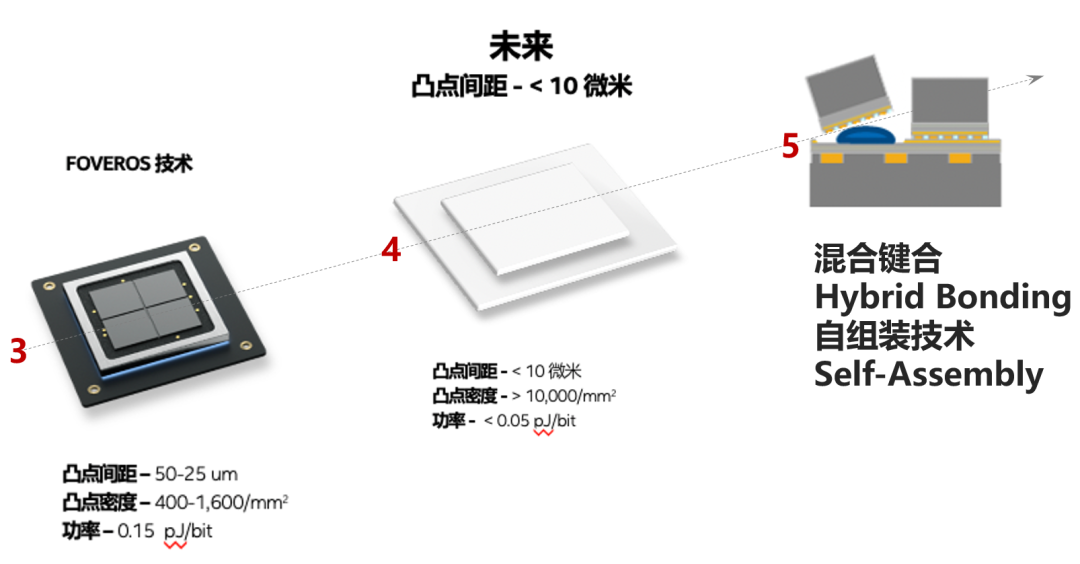

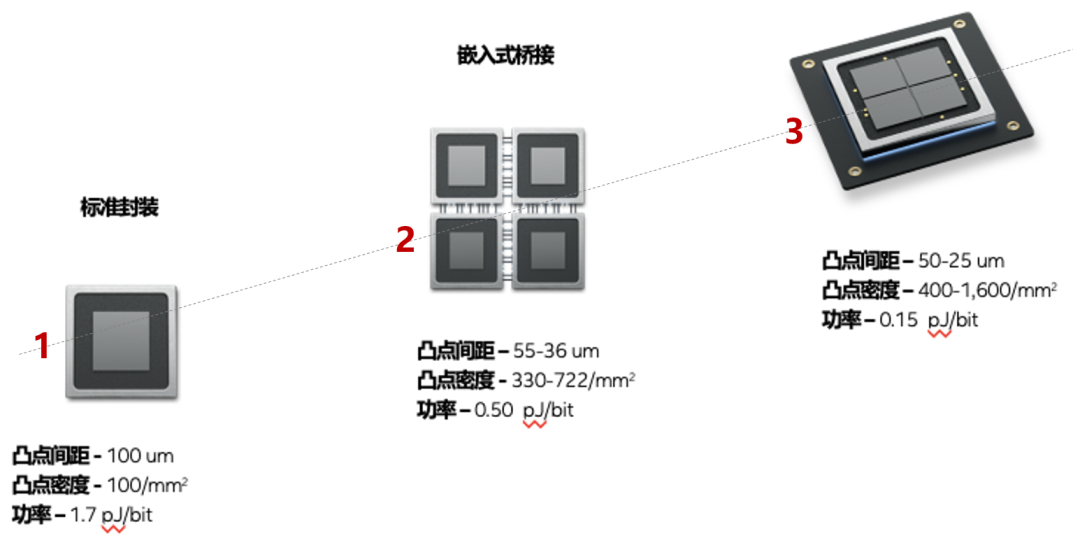

1)未来先进封装中,互联的密度会更大,界面间连接的凸点间距会缩小到10um 以下,每平方毫米的凸点数量会超过10,000个。

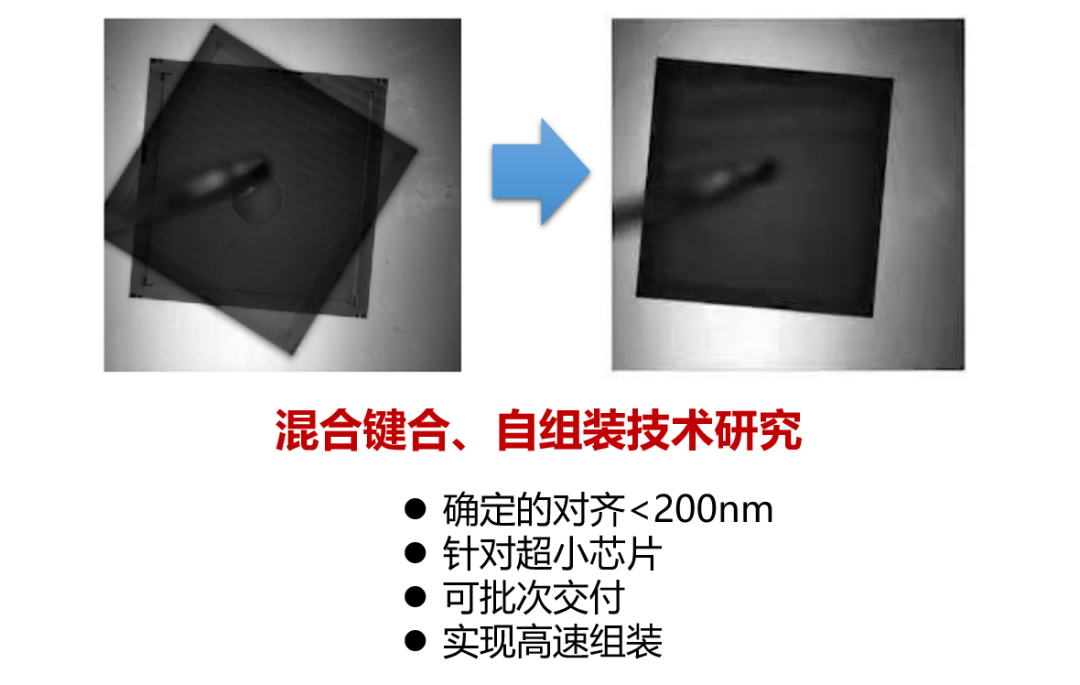

2)混合键合技术Hybrid Bonding在高密度先进封装中的普遍应用,在混合键合中,凸点已经不存在,除了金属键合在一起,硅体也会键合在一起,硅片间没有了空隙,无需填充胶,并具有更好的散热性能,因为硅本身就是良好的导热材料。此外,Intel提出的Hybrid Bonding技术和TSMC-SoIC技术具有异曲同工之妙。

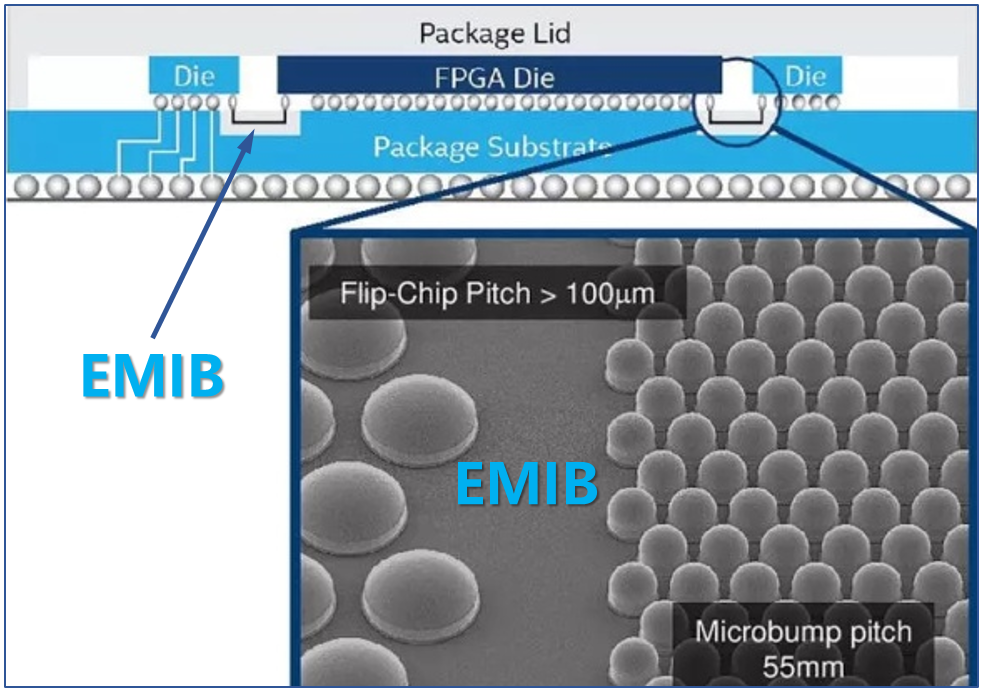

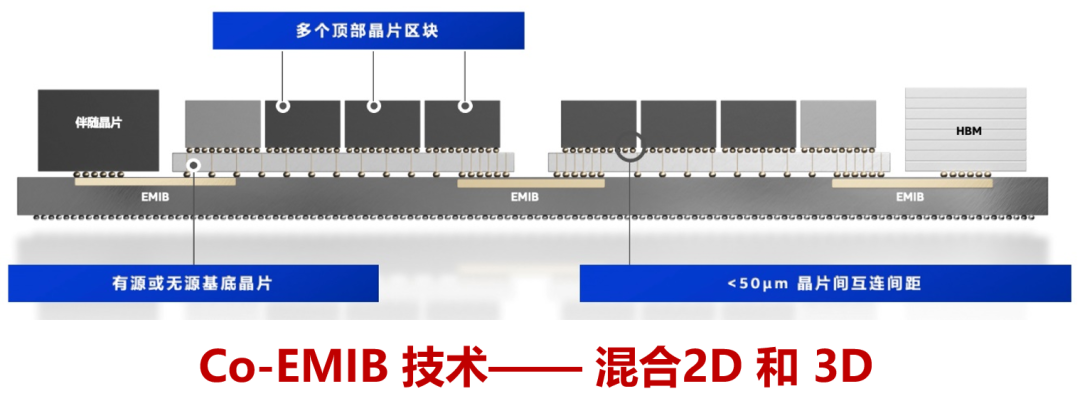

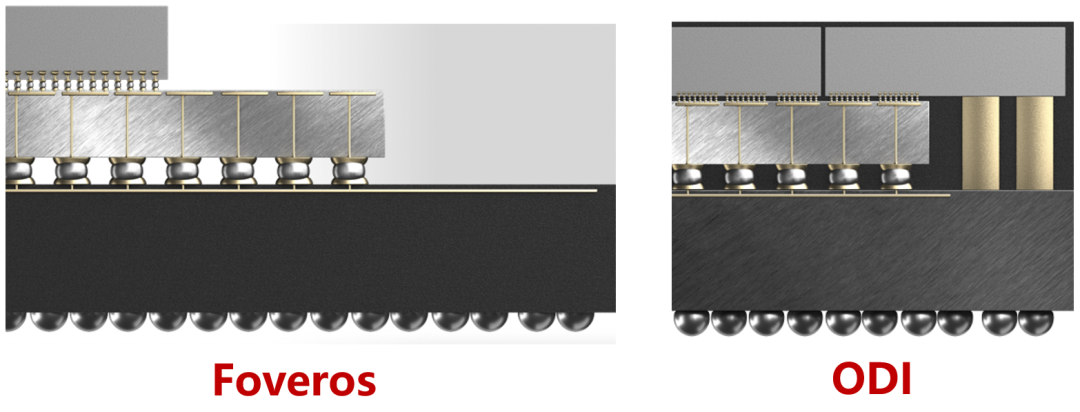

3)从 Intel的技术路线图中,我们看出,先进封装除了向更高密度方向发展,在扩展轴上,同样关注集成的灵活性,Co-EMIB和ODI就体现了这样的特点。

4)从SoC到SiP再到Chiplet,电子集成更关注高时效、低缺陷率、高可重用性。

5)Intel提出的每毫米立方体里的功能,和我在新书中提出的功能密度定律 (Function Density Law)里描述的单位体积内的功能单位 (Function UNITs)是同样的概念,也从侧面印证了功能密度定律的正确性。Intel致力于实现每毫米立方体里最大的功能,和功能密度定律的描述一致,真是英雄所见略同。

6)集成电路制造和封装测试和逐渐融合,这包括生产层面的融合和设计层面的融合,会带来挑战,也带来了更多协同的机会。

7)先进封装技术的发展需要以客户需求为导向,针对客户的需要研发特定的技术,这也是Intel先进封装的发展模式,可供国内的封测厂借鉴。

8)异构集成依然是先进封装发展的方向和未来的趋势。

免责声明:本文系网络转载,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请第一时间告知,我们将立即删除内容!本文内容为原作者观点,并不代表本公众号赞同其观点和对其真实性负责。