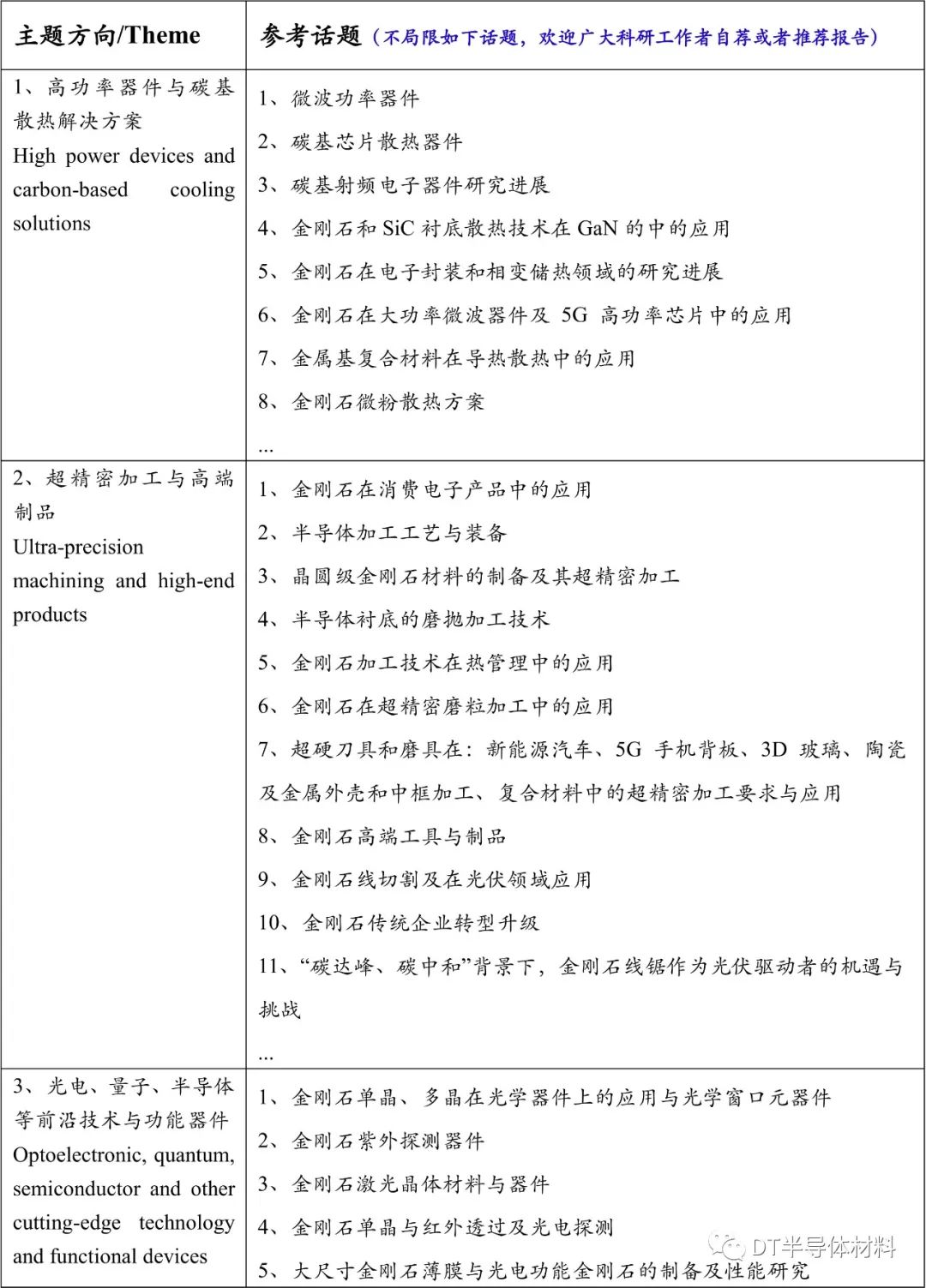

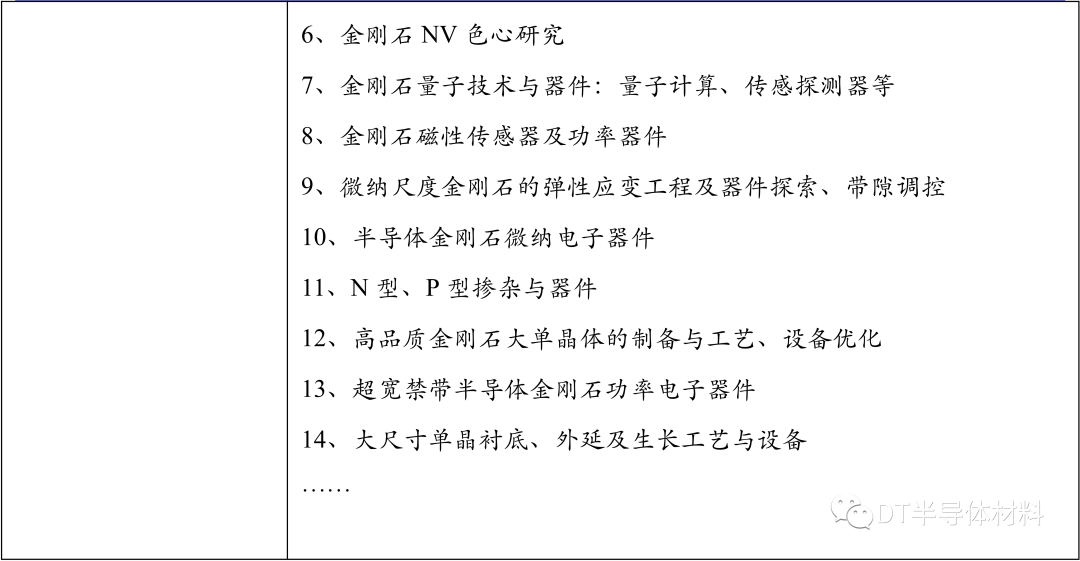

摘要:碳纳米管凭借其优良的电学性质、准一维尺寸以及稳定的结构成为后摩尔时代最理想的半导体材料. 目前碳基电子学已经取得很大进展, 例如可以在4寸晶圆上得到高半导体纯度(超过99.9999%)的密排(100~200 CNTs/μm)阵列碳纳米管, 晶体管栅长可以缩至5 nm且具备超越硅基的性能, 世界首个碳基现代微处理器RV16X- NANO已经问世. 本文综述了近年来碳纳米管在材料、器件和集成电路方面的发展, 以及未来可能在光电、传感、显示和射频等领域的应用前景. 最后, 文章列举了碳基CMOS集成电路推向产业化的过程中面临的一系列挑战, 并对碳基技术发展路线做了进一步展望。

关键词:碳纳米管, CMOS晶体管, 集成电路, 纳米电子学

引言

半个多世纪以来, 硅基集成电路的发展带来整个人类社会信息技术的巨大变革, 而以硅基互补性金属氧化物半导体(Complementary metal oxide semiconduc- tor, CMOS)技术为核心的集成电路也一直按照摩尔定律每隔18个月集成度翻倍且成本降低一半发展. 但是随着技术节点的不断缩减, 硅基集成电路已渐近物理和工程的极限. 为了延续摩尔定律, 推动集成电路的持续发展, 人们开始寻求新的材料作为突破口, 其中碳纳米管(Carbon nanotube, CNT)被列为考虑的方案之一。

单壁碳纳米管可以看成是单层石墨烯沿某一个方向卷曲而形成的圆柱形的准一维晶体, 根据卷曲方向的不同, 碳纳米管有不同的手性, 对应不同的晶体结构和能带[5], 不同直径的单壁碳纳米管可以嵌套成为多壁碳纳米管(以下未经说明默认为单壁碳纳米管)。

碳纳米管是准一维结构, 并且碳原子之间的sp2杂化决定了其具有化学性质稳定、机械强度高以及热稳定性好等优势[6], 是探索一维电子输运的理想材料. 自1991年碳纳米管被发现以来[7], 便成为最具潜力的构筑未来电子学的材料, 不仅仅是由于它的纳米尺寸天然适合制备纳米器件, 更重要的是具备电子学方面的优势[8~12]. 碳基信息电子器件主要的科学技术优势包括:

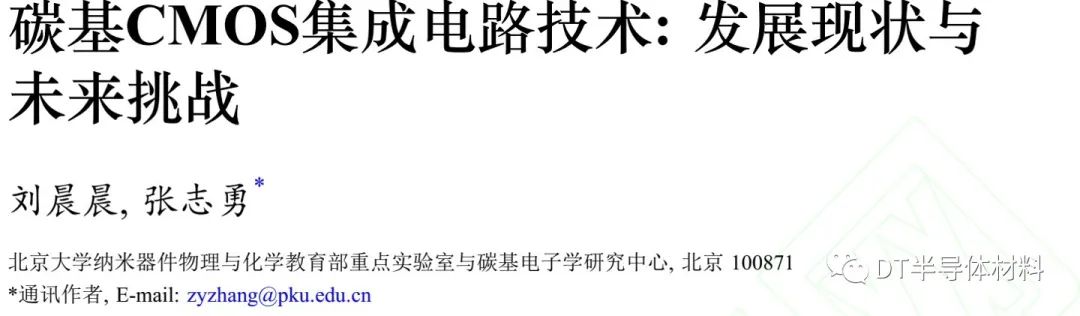

(1)高能效(即高性能与低功耗)优势. 碳纳米管载流子迁移率高、平均自由程长、本征电容小, 因此在晶体管层面, 碳基器件的性能功耗综合优势为传统晶体管的5倍(实验结果)[4], 如果上升到集成电路层面, 碳基集成电路的性能功耗综合优势可达传统电路的50 倍(理论仿真结果)(图1a, b)。

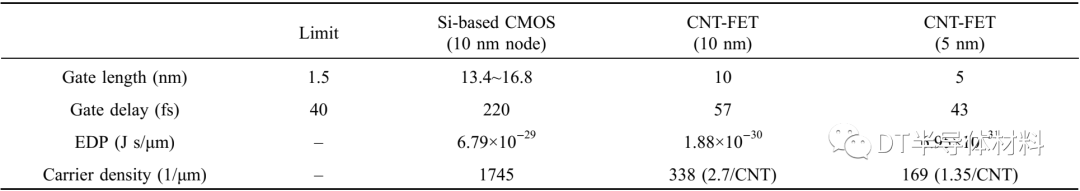

图 1 碳基集成电路与硅基集成电路在性能功耗方面的理论仿真结果[13]. (a) 硅基FINFET与碳基平面晶体管的器件模型; (b) 不同阈值电压下碳基集成电路相比于硅基集成电路的能量延时积(Energy delay product, EDP)优势; (c) 硅基MOSFET与碳基MOSFET在低至5 nm节点的工艺路线图比较[37] (网络版彩图)

图 1 碳基集成电路与硅基集成电路在性能功耗方面的理论仿真结果[13]. (a) 硅基FINFET与碳基平面晶体管的器件模型; (b) 不同阈值电压下碳基集成电路相比于硅基集成电路的能量延时积(Energy delay product, EDP)优势; (c) 硅基MOSFET与碳基MOSFET在低至5 nm节点的工艺路线图比较[37] (网络版彩图)

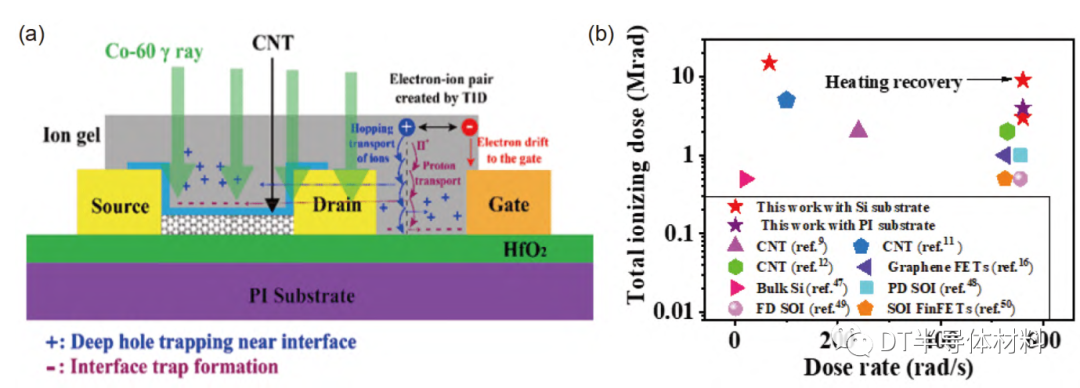

(2)对恶劣环境耐受能力强. 碳基器件具有优良的抗辐照性, 采用辐照加强技术的碳基器件抗辐照总剂量可达9 Mrad, 是传统SOI辐照加强芯片的30倍(300 krad); 抗单粒子辐照反转能力是传统芯片的20倍[14]; 碳基芯片工作温度宽,可在零下273℃低温到130℃高温环境中工作[15,16].

(3)器件的形态和功能丰富. 由于碳纳米管材料具有优良的机械柔性、高透光性和基底兼容性, 碳基技术可以实现柔性、透明、瞬态(可消失)等特种芯片, 也可以实现传感、存储和逻辑、模拟电路等多种功能器件, 满足不同应用功能和场景的需求[17~28].

(4)易于三维异构集成. 碳基器件加工温度低、工作功耗低, 易于克服三维集成电路面临的主要挑战——热预算需求, 因此更易实现三维异构集成[29]. 理论仿真结果表明, 采用三维集成的碳基集成电路较传统集成电路具有1000倍的性能功耗综合优势. 而且, 碳基材料可以实现多种功能器件, 有利于实现感存算一体芯片或者三维单片集成芯片[30~36].

(5)工艺流程短、成本低. 碳基晶体管通过控制载流子的注入来实现开启与关断, 无需掺杂过程, 而且在微缩过程中对短沟道效应有很好的免疫, 采用简单的平面器件工艺即可实现亚5纳米晶体管[4]. 相比于传统硅基工艺, 工序流程可缩短一半; 碳基技术具有良好的工艺兼容性, 沿用现有的硅基集成电路加工装备, 采用落后主流技术3代的硅基加工技术, 可制备出同等性能和集成度的碳基芯片[37,38] (图1c).

碳基集成电路的发展与现状

随着摩尔定律对硅基集成电路的发展指导作用逐渐减弱, 而全球的科技发展形式比如5G的应用、人工智能的普及以及大数据处理等对集成电路的要求越来越高, 半导体行业的供求关系出现倒挂. 硅基半导体在提升芯片性能上越来越后继无力, 而碳基作为新型的半导体材料, 具备独特优秀的电学性能和本征材料优势, 为芯片未来的发展提供新的可能选择.

碳纳米管材料

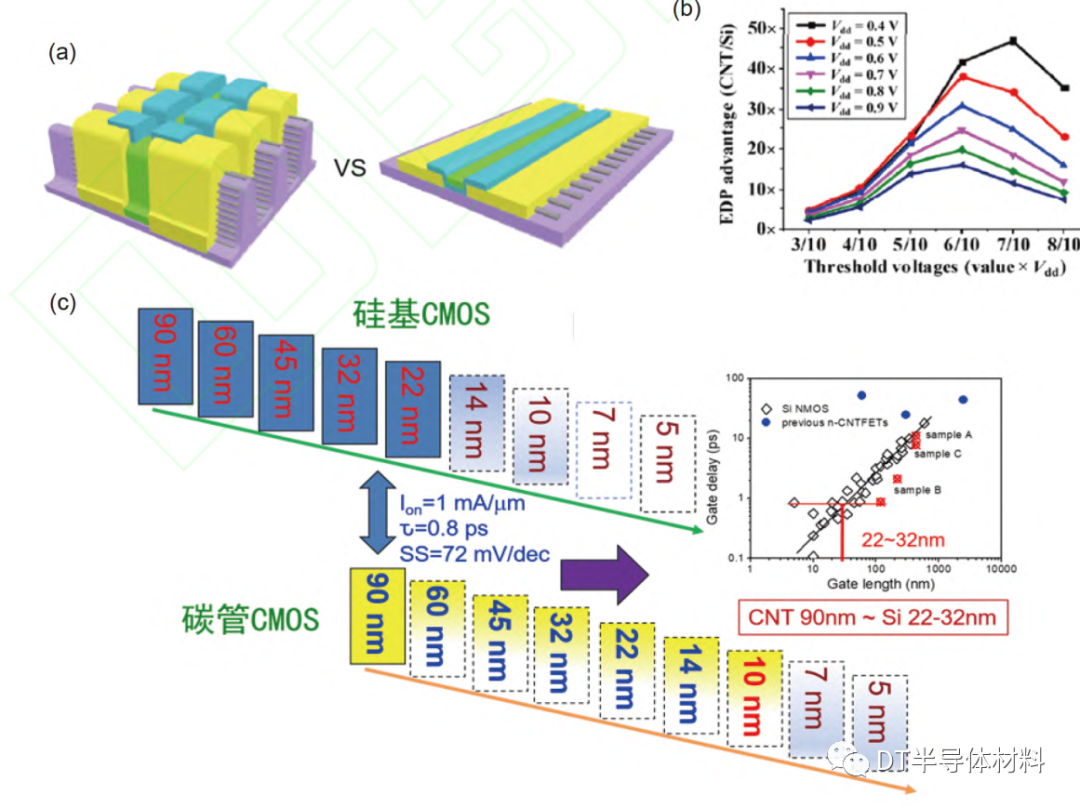

根据IBM沃森(Watson)研究中心[39]对碳纳米管做高性能集成电路的规划来看, 理想的材料是定向排列的碳纳米管阵列, 碳纳米管的最佳间距为5~10 nm, 对应阵列碳管的密度为100~200根/μm, 并且半导体型的碳纳米管纯度要大于99.9999%, 即至少“6个9”的水平. 除此之外, 由于碳纳米管的直径会影响带隙大小, 进而影响肖特基势垒的高低以及器件的接触性能, Chen等人[40]在2005年的研究结果证明了这一结论, 从欧姆接触、器件静态功耗以及均一性的角度考虑, 碳纳米管的直径分布应该在1.2~1.7 nm, 为了满足产业化的需要, 碳纳米管阵列需实现全晶圆范围的覆盖(图2).

图 2 满足产业化需求的阵列碳管示意图及关键参数[40] (网络版彩图)

制备高半导体纯度和高密度碳管的方法主要分为两种, 一种是通过CVD法利用石英或者蓝宝石的晶格取向来导向性地生长阵列碳管, 并通过一些后处理手段, 比如大电流烧断金属管等提高半导体管的纯度. 以这种方式得到的材料制备的晶体管通常具有低的开关比或低驱动电流, 且不同器件间的均一性较差. 另一种方式是先在溶液中通过离心等方式进行提纯, 得到高半导体纯度的碳管溶液, 再通过沉积、提拉等方式将碳管排列在基底上, 更易实现大规模的制备以及性能的均一.

目前在基底上排列碳管的方法有很多, 2011年Khondaker研究组[41]报道了用高质量的无表面活性剂的稳定单壁碳纳米管溶液通过交流介电电泳来组装排列碳纳米管阵列, 通过优化交流频率, 沉积时间以及碳纳米管溶液的浓度可以控制阵列管的密度在0.5~30 根/μm. 并且密度越高, 顺排性越好. 在30根/μm的密度下, 取向角的变化不超过10°, 平均直径为2 nm, 长度分布从500 nm到10 μm. 2013年IBM的Cao等人[42]展示了用Langmuir-Schaefer方法组装阵列排布的碳纳米管, 这种方法得到的碳纳米管的半导体纯度达到99%, 密度超过500根/μm, 碳纳米管直径分布在1.4±0.4 nm. 用这种方法得到的碳纳米管的间距是由碳纳米管的直径和范德瓦尔斯力决定, 排列之后碳管的本征迁移率仍然保持不变. 但是由于密度过大, 远超过理想的150根/ μm, 在做成FET器件的时候栅控效率不太理想.

2014 年威斯康星大学的Gopalan研究团队[43]研发了一种新型的“剂量控制, 浮动蒸发自组装”的方式来排列阵列碳纳米管, 这种方式可以很好的控制单壁碳纳米管排放位置和质量. 该方法利用有机溶剂在水-空气界面上的分离, 将半导体纯度为99.9%的s-SWCNT管沉积在部分淹没的疏水性基体上, 疏水性基体垂直从水面提取即可得到排列好的阵列管薄膜. 用这种方式得到的阵列碳纳米管的取向角的偏差可以控制在14°以内, 阵列管的密度达到10根/μm, 并且可以在基底上形成良好的单分散层, 碳纳米管的直径分布在0.8~1.1 nm.

在碳纳米管的纯度、排列以及密度控制等方面国内的研究团队也取得了很大的进展, 2016年北京大学彭练矛研究组[44]展示了一种“蒸发诱导自组装”方法, 可以实现微米级别的阵列排布, 并且对碳纳米管排列的偏振度进行了定量表征, 平均值为76.8%. 2018年该课题组又发展了一种“薄膜定向收缩法”, 这是一种基于随机排列的碳纳米管薄膜通过定向收缩形成高密度排列的碳管薄膜的方法[45,46], 其原理是将随机取向的碳纳米管溶液转移到可拉伸的膜上, 再进行定向的收缩, 碳纳米管的取向会随着收缩倍数的增加而逐渐趋于统一, 密度也会随着收缩程度的增大以及碳纳米管溶液密度的增加而增大. 在这项工作中, 碳纳米管溶液经过提纯得到99.9%的半导体型溶液, 收缩之后的密度达到37根/μm, 并且可以实现全晶圆的覆盖, 碳纳米管的取向角变化控制在13°以内.

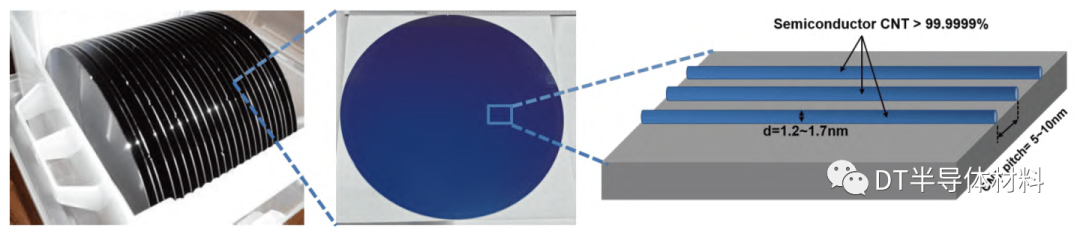

图 3 碳基数字集成电路技术中的晶体管结构以及材料要求[48]. (a) 基于碳纳米管的顶栅FET示意图, 并且碳纳米管间距在5~10 nm, S代表源端, D代表漏端; (b) 各项工作中阵列碳纳米管的密度与半导体型纯度的展示, 满足集成电路需求的是图中蓝色框区域, 这项工作的结果用粉色区域中的五角星表示 (网络版彩图)

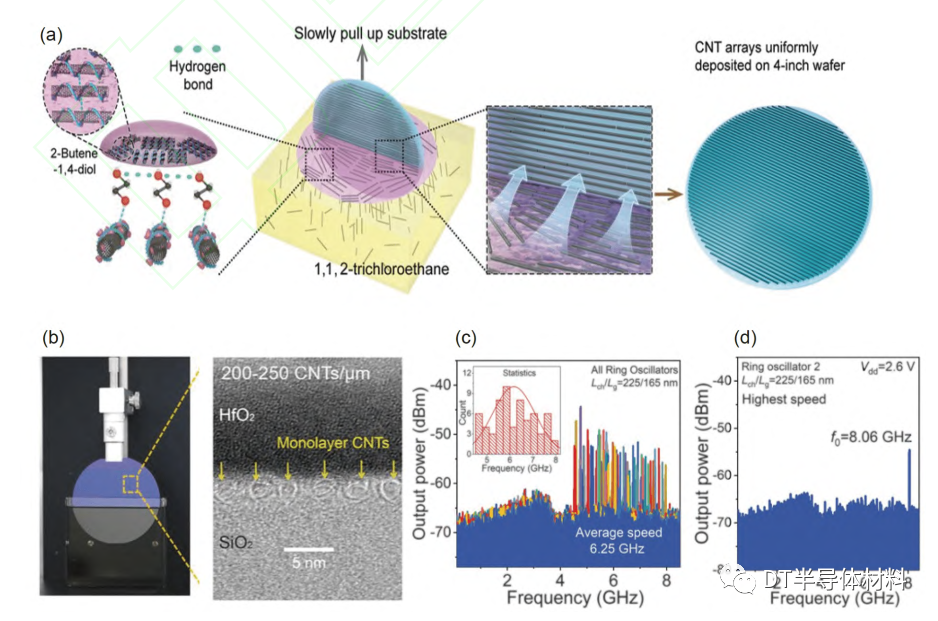

2020年该课题组又发展了“维度限制自组装(Dimension-limited self-align- ment, DLSA)”以及“DNA限制自组装”的方法[47]. 前者的原理是首先经过一个多重分散与筛选的过程得到高纯度半导体型的碳管溶液, 能够实现99.9999%的纯度, 满足了高性能碳纳米管集成电路对材料的要求, 该体系下碳纳米管分散在溶液与空气的分界二维平面上, 将晶圆衬底浸入溶液中, 与液面形成一维方向的接触, 通过垂直方向拉伸晶圆, 液面上的碳纳米管由二维向一维过渡进而沉积到晶圆表面, 形成定向排列的碳纳米管薄膜. 这种方法形成的碳纳米管阵列的密度可以控制在100~200根/μm, 同样满足高性能碳基集成电路对材料的要求(图3).

除此之外, 根据偏振拉曼光谱的结果显示, 碳纳米管阵列的取向角控制在8.3°的范围内, 碳纳米管的直径也控制在1.45±0.23 nm, 该方式得到的阵列碳纳米管首次达到碳基数字集成电路的材料标准. 第二种“DNA自组装”的方式是利用DNA分子对碳纳米管的选择性, 使单根碳纳米管固定在两个DNA 分子中间, 再通过化学方式去除DNA分子就可以得到间距和取向一定的碳纳米管阵列薄膜, 这种方式得到碳纳米管取向性很好, 有56%的取向分布可以控制在1°以内, 90%的碳纳米管取向分布控制在7°以内.

碳纳米管器件

碳纳米管具有原子级厚度, 这使得它具备天然优势制备亚10纳米器件, 为CMOS电路的尺寸缩减提供了一种解决方案. 为了展示碳纳米管在电学方面的本征优势以及工艺加工能力, 基于单根碳纳米管的器件研究比较多[40,49~54]. 2009年彭练矛研究组[51,55]发展了一种无掺杂方法, 用Pd接触实现P型晶体管, 用Sc或Y 接触实现N型晶体管, 并且P型和N型的性能对称匹配(图4). 该工作展示了栅长为1 μm的晶体管在0.1 V的偏压下, P型晶体管可以实现5个量级的开关比, 亚阈值摆幅(Subthreshold swing, SS)约90 mV/dec, 跨导gm达到

17.0 μS, 而N型晶体管可以实现5个量级的开关比, 以及100 mV/dec的SS, 跨导gm为14.5 μS. N型和P型的晶体管的门级延时可以到2×10−11 s, 并且随着栅长的缩减而变小. Franklin研究组[54]在2010年探究了基于单根碳纳米管Pd接触的P型器件的尺寸缩减行为, 他们研究了沟道长度从3 μm到15 nm下的器件性质, 在最小的沟道长度也就是15 nm的条件下可以达到室温下最高的电导和跨导, 分别为0.7 G0和40 μS.

图 4 (a) 一对P型与N型场效应晶体管构成的碳管CMOS器件的侧视示意图. P型晶体管由Pd接触实现, N型晶体管由Sc 接触实现; (b) P型(蓝色)与N型(红色)对称的输出特性曲线, 从下往上, |VGS|以0.05 V的步长从0 V增加至2 V[56] (网络版彩图)

同时他们也研究了接触长度和接触电阻的关系, 在接触长度和沟道长度均为20 nm的器件中, 可以实现10 μA的开态电流, 5个数量级的开关比以及20 μS的跨导. 2012年IBM 研究组首次将栅长缩减到10 nm[53], 器件结构是简单的局域底栅, 用Pd接触来实现P型, 在0.5 V的偏压下得到归一化之后大于2.41 mA/μm的开态电流, 是当时硅基最好的工艺下FET开态电流的四倍, 同时SS为94 mV/dec. 2017年彭练矛-张志勇团队[4]率先实现了5 nm栅长的高性能P型CNT-FET. 该晶体管的综合性能比当时最好的硅基晶体管领先十倍, 接近理论极限, 其工作速度是Intel当时最先进的14 nm商用硅材料晶体管的3 倍, 能耗却只有其四分之一, 并在尺寸能耗等关键参数上超过硅基当时最先进的技术节点——10 nm工艺(表1). 5 nm栅长的晶体管归一化载流子密度为169/μm, 即每根碳纳米管中只有1.35个载流子参与导电, 证明了极限尺寸下的碳管晶体管可实现对单电子的调控(图5).

碳基集成电路

制造可与硅基匹配甚至超越硅基的高性能碳基集成电路一直是研究碳纳米管电子学的各个科研团队的目标, 一直以来, 研究者们从CMOS器件、小中大规模电路到具备简单功能的计算机, 一步步进行突破与建设[55~65].

2013年斯坦福大学的Shulaker等人[66]展示了全球首台碳纳米管计算机的原型. 在这项工作中, 整个碳纳米管计算机是在一个4寸的晶圆上制造的, 每个晶圆包含197个die, 每个die包含5个碳纳米管计算机, 每个计算机包含178个碳纳米管场效应晶体管(Carbon nano- tube field effect transistor, CNFET), 每个CNFET包含10~200根碳管, 其中碳管的数量取决于CNFET的尺寸以及碳纳米管之间的间距. 该计算机依旧采用冯诺依曼架构, 通过外部互联线将计算部分与外部存储器相连, 子系统(如D锁存器)的良率是80%到90%之间, 工作频率为1 kHz. 2014年Shulaker等人[31]首次展示了逻辑电路与存储电路, 硅基电路与碳纳米管集成电路的单片三维集成电路, 该结构一共分为四层, 底层是传统的硅基逻辑电路, 中间两层是低温工艺制造的电阻随机存储器(Resistive random access memory, RRAM), 顶层是碳纳米管逻辑电路.

图 5 极限尺寸下晶体管开启状态下的载流子输运模型示意图. (a) 硅基MOSFET开态下, 沟道中有众多载流子参与输运; (b) 5 nm栅长碳纳米管晶体管在开态时只有1个载流子参与沟道输运过程[4](网络版彩图)

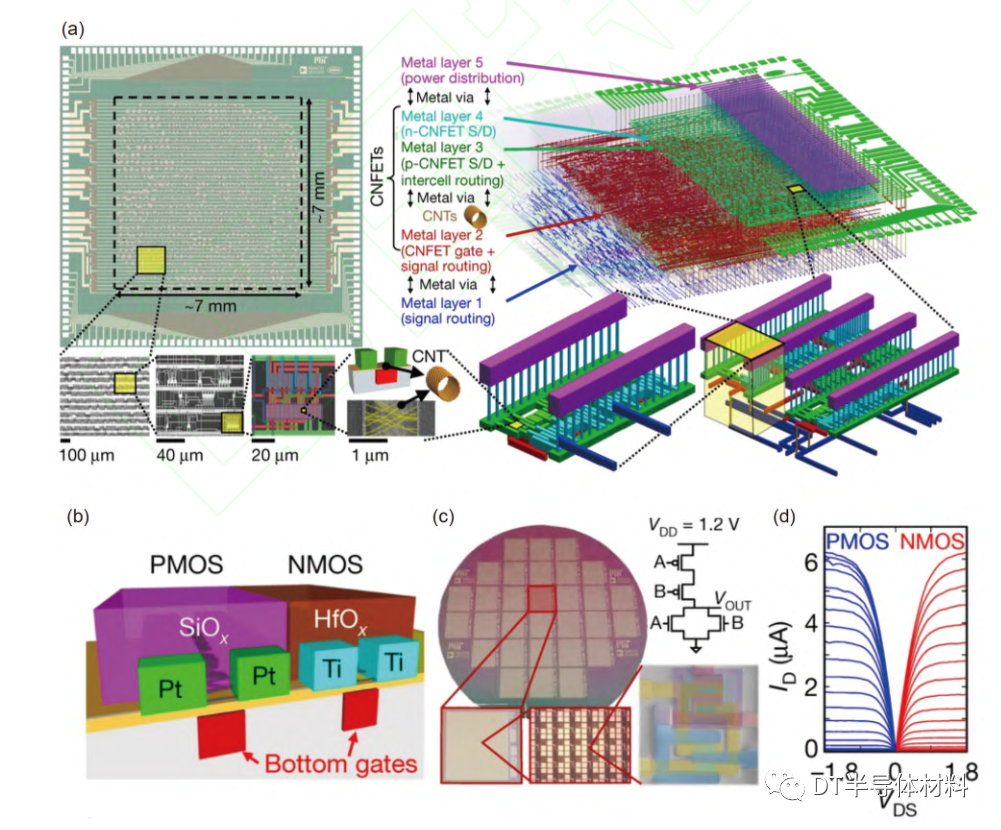

该结构实现了逻辑与存储在任意垂直堆叠顺序下的三维集成, 且二者可以用传统的层间通孔工艺连接, 这为数字系统带来了巨大的速度和能量效益. 2018年他们实验性地展示了一个使用CNFET和RRAM单片3D集成构建的端到端超维计算纳米系统[34]. 该系统可以对21种语言进行分类, 在超过20000个句子(640万个字符)中, 测量平均准确率高达98%. 该系统与传统硅基CMOS电路相比, 不仅面积缩减了三倍, 在对于语言分类数据集的训练和推理方面有35倍的EDP改善. 该系统采用3 V的工作电压, 工作频率为1 kHz, 内部晶体管的栅长为1 μm, 共包含1952个CNFET以及224个RRAM. 2019年, Shulaker团队[59]又发布了全球首个碳纳米管通用现代微处理器RV16X-NANO, 这是碳基集成电路发展史上里程碑式的成果, 该微处理器是基于RISC-V指令集, 可以实现对16位数据和地址运行标准的32位指令进行处理. 该处理器包含超过14000个互补型金属氧化物半导体CNFETs, 并且整个设计和加工制造的过程均采用业界标准的工具和工艺, 可以执行指令获取、解码、寄存、执行单元以及写回存储器等功能.

表 1 不同场效应晶体管以及理论极限的关键参数对比

碳纳米管CMOS电路的实现是通过不同功函数的金属接触 (Pt接触实现P型, Ti接触实现N型)和对沟道进行的电学掺杂(SiOx实现P型掺杂, HfOx实现N型掺杂)实现. 该处理器是在150 mm的晶圆上制作, 每个晶圆上包含32个die, 每个die包含10400个碳纳米管CMOS逻辑门电路, 碳纳米管的半导体纯度为99.99%, 每个CNFET里包含15到25根碳纳米管. 微处理器的工作频率为10 kHz, 功耗约为969 μW. 这是迄今为止用碳纳米管制造的最大的芯片, 其规模达到Intel公司于1985年推出的80386处理器芯片的水平. 2020年, Shu- laker团队证实碳纳米管场效应晶体管已接近商业化应用, 可在200 mm晶圆上快速制备大量的碳纳米场效应晶体管. 此外, 研究人员还证实, 碳纳米晶体管还可以在室温下进行堆叠制造, 从而制成多层芯片, 而传统的硅晶体管需要在450~500℃的高温下制造, 难以进行堆垛. 这些工作是在商业硅基生产线上进行的, 表明碳纳米管集成电路已具备较大的量产可能性.

2018年IBM 的Tang等人[67]开发出基于碳纳米管且延迟低于10 ns 的柔性CMOS集成电路. 由于柔性碳纳米管薄膜晶体管的性能通常比刚性碳纳米管晶体管低, 逻辑门延迟超过1 μs, 限制了其实际应用. 研究团队通过可扩展的工艺在柔性聚酰亚胺基板上制造高性能碳纳米管薄膜晶体管和互补电路, 实现高电流密度、大开/关电流比、小亚阈值斜率、高场效应迁移率以及出色的机械柔韧性. 该电路最低延迟仅有5.7 ns. 该电路是在4寸晶圆上制作的16×16的碳纳米管薄膜晶体管的阵列, 所用的随机分布的半导体型碳纳米管纯度大于99.99%, 平均长度为1 μm, 密度约为100根/μm2.

图 6 (a) Co-60 γ射线辐照损伤免疫的碳管晶体管原理示意图; (b) 碳基晶体管与其他类型晶体管的辐射损伤免疫性能对比(该工作中碳管晶体管的性能用红色五角星标注)[68] (网络版彩图)

我国在碳基集成电路也有很大的进展, 2017年彭练矛-张志勇团队[63]制备高性能碳纳米管电路, 最高速度达到了5.54 GHz, 2020年通过改进材料, 将电路速度提升到8.06 GHz[48]. 在抗辐照方面, 2020年, 该团队制备了超强抗辐照的碳纳米管集成电路, 通过系统地对碳纳米管晶体管进行抗辐照加强设计, 将碳基晶体管和集成电路的抗辐照总剂量能力提升到15 Mrad(Si), 在此基础上, 发展了可修复辐照损伤的碳纳米管集成电路. 结合超强抗辐照能力和低温加热可修复特性, 构建了对高能辐照免疫的碳纳米管晶体管和集成电路(图6)[68].

碳基CMOS集成电路可能应用的领域

随着人们对碳纳米管以及碳管晶体管工作原理的了解逐渐加深, 碳纳米管在多个领域的应用优势逐渐显现, 比如工作电压低、速度快和本征一维特性使其可用于高速低能耗的数字集成电路; 碳纳米管的载流子迁移率高, 使其在空间通信, 高速无线电路, 车辆雷达等需要在高速信号传播的射频器件领域有很大优势; 除此之外, 碳纳米管作为纳米材料, 其集体性能在宏观弯曲条件下变化不大, 因此可用于可穿戴式传感器, 显示器等柔性或透明的领域.

数字集成电路

早期科研人员在单根碳纳米管上制作小规模的电路, 实现简单的逻辑功能, 比如反相器、或非门、与门、环振电路、以及存储单元等. 2001年Bachtold 等人[61]在单根碳纳米管上通过栅极的调控作用实现N型“掺杂”和P型“掺杂”, 并基于少量晶体管制备了多组逻辑门电路.

后来, 科研人员通过催化等方式提高了CVD法生长碳纳米管的密度, 形成碳纳米管阵列, 一些研究团队基于阵列碳纳米管制备集成电路. 2014年, Shulaker等人[62]首次制备了超大规模碳纳米管数字集成电路, 并将沟道尺寸缩减到<20 nm, 接近硅基先进技术节点, 并制备出全集成的碳基红外光传感和接口电路. 但是CVD方式生长并转移到基底上的碳纳米管半导体纯度不高, 因此科研人员采用了多种方法提纯, 比如选择性气体刻蚀金属管[69], 溶液法离心提纯[70], 电击穿[71]等.

图 7 基于碳纳米管薄膜的中等规模集成电路. (a) 6寸碳基集成电路晶圆的图像; (b) 基于碳管网络薄膜制作的4位加法器的显微照片[56] (网络版彩图)

在现阶段, 发展最成熟的碳管材料是通过溶液法制备的高纯度随机取向的碳纳米管薄膜, 又称碳纳米管网络薄膜(network-CNT). 彭练矛-张志勇课题组[56]在2017年通过溶液法提纯制备碳纳米管薄膜, 并实现了100%良率的高性能中等规模集成电路(图7). 2019年, 该课题组研究了随机取向碳纳米管薄膜晶体管的性能极限, 探索了晶体管的横向、纵向尺寸的微缩规律, 制备的120 nm栅长的network-CNFET 性能可满足大规模数字集成电路的需求[64].

模拟/射频电路

碳纳米管由于其高迁移率, 高饱和速度以及小电容, 被认为是构建射频器件的理想材料. 早期, 碳管射频器件性能的提升主要依靠材料的进步, 比如半导体纯度、取向以及洁净度等等. 2006年, 里法尔大学的研究人员使用金属Al作为底栅电极, 其表面的自然氧化层Al2O3作为栅介质, 通过电泳将提纯后的碳纳米管沉积在栅介质表面, 接着沉积接触金属, 完成射频器件的制作, 该方法制备的器件本征截止频率(fT)可以达到8 GHz[25]. 2007年该团队优化材料制备的工艺, 得到顺排性更好的碳管阵列, 将射频器件的本征截止频率提高到30 GHz[24]. 2009年, 该课题组将碳纳米管的半导体纯度提高到99%, 使本征截止频率上升一个台阶, 达到80 GHz. 除此之外, 碳纳米管对衬底的选择很多, 比如寄生电容小的石英衬底, 其上生长的碳管迁移率可以超过1000 cm2/(V s), 是更适合制备碳基射频器件的衬底材料. Rogers研究组[72]近些年来系统地研究基于CVD在石英衬底上生长碳管的射频应用.

2007年该研究组在石英基底上实现了截止频率为0.42 GHz的碳基射频器件, 并于2008年构建了一个碳纳米管收音机[73], 其中包含四种碳纳米管射频器件, 与无源器件如电阻、电容、电感连接起来, 组合成锁存放大器、混频器以及音频放大器等, 这是目前为止构建的最为复杂的碳纳米管射频电路. 2009年, 该课题组优化了碳管材料的生长工艺和射频器件的结构, 将截止频率提高至30 GHz[74].彭练矛课题组[75]发现在石英衬底上以CVD生长的碳管阵列做成的晶体管具有双极性的特点, 并将其应用在高性能倍频器和混频器上, 可以实现40 GHz的工作频率. 南加利福尼亚大学Zhou等人[76]创新地使用T-gate的器件结构, 将碳纳米管射频器件的本征截止频率提升至102 GHz.

传感平台

碳纳米管具有原子级厚度、大的比表面积、良好的生物兼容性以及优异的电学性能, 因此可以作为MOSFET的沟道材料来构建超灵敏的传感器. 碳纳米管的尺寸很小, 可以用来制备超精细的传感器件用于精密仪器的传感探测或者植入到生物体内; 碳纳米管阵列或者无序的碳纳米管薄膜能实现晶圆级别的覆盖, 可以用来实现大面积高精度的探测. C–C键是自然界最强的化合键, 碳纳米管也具有很好的化学稳定性, 可以在较恶劣的环境中保持性能稳定. 半导体型碳纳米管的态密度随费米能级的位置移动发生明显改变, 所以暴露在环境中的碳原子对电荷转移非常敏感. 因此碳纳米管在生物化学传感领域有巨大的应用潜力. 以气体传感器为例, 碳基气体传感器可以分为两大类: 基于纯碳纳米管材料和基于碳纳米管复合材料.

有关前者的研究最早可以追溯到2000年, Collins 等人[77]发现碳纳米管的电阻对测试的气体环境变化非常敏感. 他们在真空中以及氧气环境中测试碳纳米管器件的传输特性以及扫描隧道谱, 发现碳管的电阻和态密度受到氧气浓度的强烈影响, 且这种变化是可逆的, 这项工作展示了碳纳米管在化学传感领域的应用潜力. 同年Dai等人[78]发现单根半导体型碳纳米管在室温下就可以对氨气和二氧化氮的吸附产生响应, 相较于传统的需要高温环境工作的金属氧化物半导体有巨大的优势. 该研究团队基于碳纳米管底栅FET, 利用通入气体前后转移特性曲线的变化实现对气体类型以及浓度的判断.

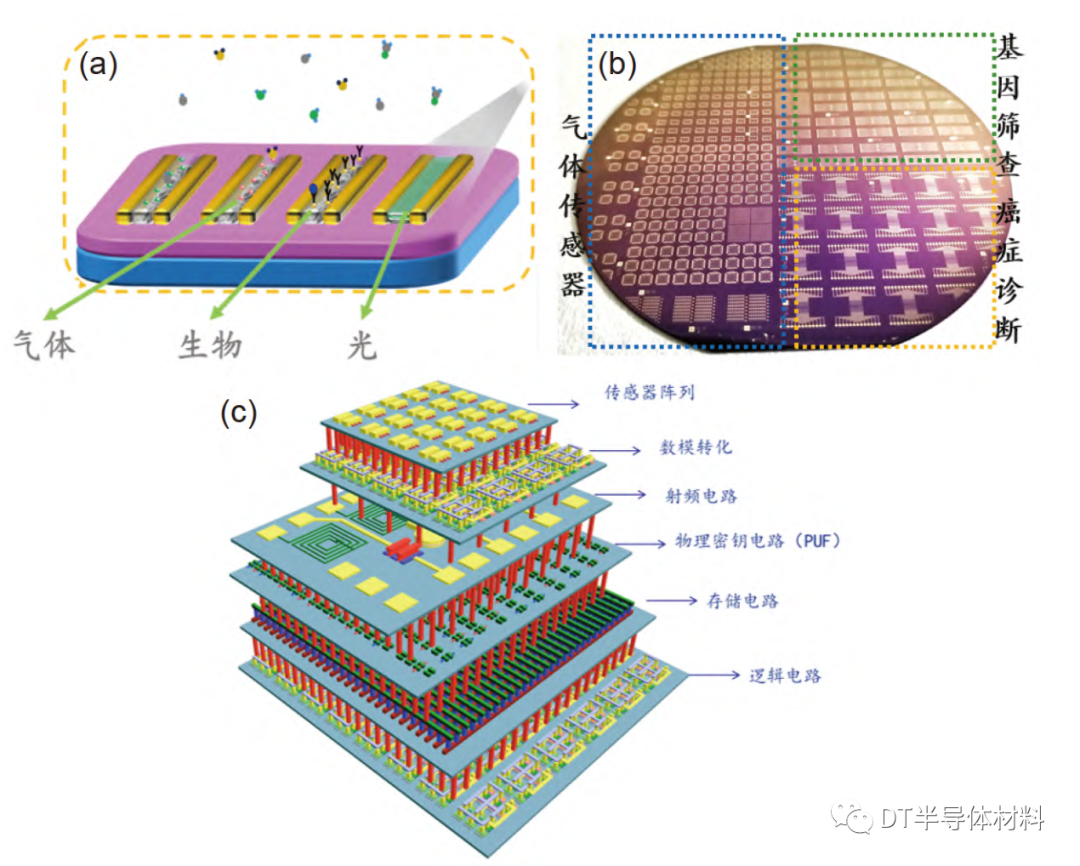

图 8 基于碳管材料的多功能传感平台[84]. (a) 集成“气体”、“生物”与“光”信号复合传感的小型芯片; (b) 集成气体传感、基因筛查与癌症诊断功能的4寸基片; (c) 集信号检测、数据传输、存储及计算系统于一体的三维集成电路模型[84] (网络版彩图)

本征的碳纳米管对氨气、氧气、水这类可以强烈吸附并可与碳原子发生电荷转移的气体分子产生明显响应, 但对于一些不能有效吸附的分子, 响应能力会下降很多, 因此科研人员对本征碳纳米管进行多种方式的修饰, 形成功能性的碳纳米管, 以实现对多种物质的探测. 2001年, Dai等人[79]将0.5 nm的Pd金属蒸镀到CVD生长的单根半导体型碳纳米管上, 放入氢气氛围中, Pd与氢气相互作用导致其功函数降低, 与碳管之间发生电荷转移, 进而改变碳纳米管的电导, 可以实现40 ppm的探测灵敏度. 2007年Mubeen等人[80]采用无序碳纳米管薄膜制备底栅器件, 并采用电化学方式在碳管薄膜上沉积一层Pd纳米颗粒, 极大地提升了碳管传感器的规模制备能力. 除此之外, 2006年, Star等人[81]采用电化学修饰在无序碳纳米管薄膜上修饰了18种金属颗粒, 系统地探究了不同的金属修饰对氢气、硫化氢、甲烷以及一氧化碳等气体的响应以及选择性, 并在一个芯片上集成了Pt、Pd、Rh、Au修饰实现了碳纳米管传感器阵列电子鼻系统, 并采用模式分析法研究了传感器阵列对有毒/可燃性混合气体的响应, 并辨识出混合气体的成分. 这种传感器阵列极大地增强了对于混合气体的分辨和选择性, 可用于制备低功耗, 小尺寸的便携传感阵列体系用于个人防护以及空气检测等方面. 除了金属修饰之外, 半导体金属氧化物颗粒也可作为修饰因子与碳管形成复合材料, 如N型半导体SnO2、TiO2、ZnO以及P型半导体Co3O4、CuO等, 2010年, Chen等人[82]采用SnO2修饰多壁碳纳米管, 实现了室温下对低浓度的二氧化氮, 氢气以及一氧化碳的检测, 相比于单一的碳纳米管, 灵敏度有所提升, 响应速度也得到了改善. 有机聚合物也可以作为修饰碳纳米管的材料, 2003年, Dai等人[83]利用强电子掺杂的聚亚乙基亚胺(PEI)作为修饰, 提升了碳纳米管传感器对二氧化氮这种强电子施主型气体的灵敏度, 将灵敏度推进到100 ppt, 同时也抑制了对NH3这类强电子受主型气体的响应, 提升了传感器的选择性.

除此之外, 半导体型碳纳米管对生物、化学分子以及光信号等都有不同程度的响应, 可以通过修饰增强, 来构建一个超灵敏的多功能复合的传感平台, 实现对多种传感信号的响应. 2020年, 彭练矛课题组[84] 利用修饰后的碳管对生物分子的选择性检测, 在4寸基片上集成基因筛查与癌症诊断的传感功能, 实现对生物信号的多功能检测(图8b). 未来可通过三维集成等方式将传感阵列与逻辑、存储、射频电路等整合到一起, 构建一个完善的集信号检测, 数据传输与信息计算于一体的系统 (图8c), 在军事勘测、生产生活以及安全检测等方面都有非常广泛的应用前景.

柔性智能系统

柔性电子是将有机/无机材料电子器件制作在柔性/可延性基板上的新兴电子技术. 相对于传统电子, 柔性电子具有更好的机械柔韧性, 能够在一定程度上适应不同的工作环境, 满足设备的形变要求. 除优异的电学性能外, 碳纳米管的光学和力学性能也使其适用于柔性电子器件的制造. 此外碳纳米管具有柔韧性好、耐弯曲和耐疲劳强度高等特性, 这些在柔性智能的应用领域是必不可少的条件.

碳基半导体材料有望在实际中满足多种柔性电子器件的应用场景: (1)柔性应变/压力传感器, 该类传感器通常由导电传感元件与弹性聚合物或其他柔性/可拉伸基材(如纤维、纱线和纺织品)耦合组成, 通过应变/压力刺激引起的导电元件间接触电阻的变化来检测材料应变或外界压力; (2)柔性/可穿戴电子器件, 由于柔性电子器件具有很好的柔性和延展性, 可与人体的外形特性和运动特性相匹配, 并完成传感、显示等功能, 可应用于消费电子、医疗保健等行业; (3)柔性能源系统, 该类系统的定义为柔性甚至可伸缩的能源装置, 包括超级电容器、电化学电池(例如锂电池、钠电池和金属空气电池)、光伏装置和发电机等; (4)透明导电薄膜(TCFs)类应用, 该类应用包括柔性触摸板、柔性有机发光二极管(OLED)和柔性有机太阳能电池(OSC)等(图9).

图 9 基于碳纳米管的柔性智能化集成传感系统[19] (网络版彩图)

相关的研究工作也比较热门, 在传感方面, 2017年Baughman等人[85]利用碳纳米管纱线制备了TWIS- TRON传感器件, 这种传感器件可与衣物编织在一起, 来探测人体呼吸过程中产生的胸腔起伏变化. Kim等人[28]利用碳纳米管拉丝纤维制成超弹性材料, 拉伸率高达99%, 并利用拉伸过程中导电通路的变化实现应力传感, 用于人体运动以及呼吸的监测. Cao等人[86]利用双螺旋型过加捻的碳纳米管在拉伸过程中的电阻变化, 实现大应变(高达500%)的测试. 碳纳米管薄膜作为一种膜材料, 在压力传感领域也有广泛的应用, Khine 等人[87]利用褶皱纳米管薄膜在压力作用下产生的电阻变化, 制备了高灵敏的压阻型传感器, 可测压力最高可达278.5 kPa, 最低能够探测到人体脉搏跳动引起的微小压力变化.

在柔性/可穿戴电子器件方面, 2018年北京大学胡又凡课题组[19]制备了晶圆级别的碳纳米管薄膜晶体管和集成电路, 且可以转移到多种基底上, 比如可生物降解的聚合物, 植物叶子以及人体表面等等, 以实现不同应用场景下的多种功能(图9).

显示驱动系统

平板显示作为支柱型的消费电子产业, 占据巨大的市场空间. 随着平板显示向大尺寸、高刷新率以及高分辨率等方向的发展, 以及柔性、透明等特殊需求的增加, 驱动所用的薄膜晶体管(Thin-film transistor, TFT)的种类和性能也有了更高的要求. 碳纳米管具有超薄、柔性以及高迁移率等优势, 因此基于碳纳米管的薄膜场效应晶体管(Carbon nanotube thin-film tran- sistor, CNT-TFT)具备满足未来显示领域需求的潜力, 或许是碳纳米管率先实现产业化应用的突破口. 目前国际上已经广泛地开展了将CNT-TFT应用于显示驱动方面的研究, 并展示了基于CNT-TFT显示器的原型.

2011年, Zhou等人[88]报道了CNT-TFT驱动的20×25阵列像素的OLED显示屏. 每个像素采用2T1C 的驱动方式, 晶体管的栅压扫描范围在−5 V~5 V, 开关比大于104, 电流驱动能力约为0.8 μA/μm, 500个像素中有348个被成功开启, 产率为70%. 随后在2016年, 该课题组实现了CNT-TFT驱动的七段码液晶显示[89], 通过改变晶体管的输入电压, 来调节液晶电容的透光率. 驱动晶体管的平均迁移率在13 cm2/(V s), 开关比有106, 栅压扫描范围在−10 V~10 V.

2015年, Zhang等人[90]也利用2T1C的电路驱动OLED, 并实现了6×6阵列像素的静态和动态显示, 所制备的CNT-TFT 的开关比为10 5 , 迁移率约为45 cm2/(V s), 器件的栅压扫描范围在−10 V~10 V. 从显示结果来看, 像素的显示效果差异较大, 亮暗不一, 说明器件的均一性比较差.

2019年Sun等人[91]在柔性衬底上制备了64×64的阵列OLED显示屏, 其像素产率高达99.93%, 整个显示屏的驱动电路包含了8000多个CNT-TFT, 器件的均一性较好, 开关比可达到107, 迁移率在16 cm2/(V s)左右, 栅压的扫描范围在−5 V~2.5 V, 但是存在较大的回滞, 显示效果也只呈现了全亮的静态显示.

光电集成

但是以上基于单根碳纳米管的器件只能作为原理性的展示, 并不能投入实际应用. 业界所使用的光电探测是一种依赖外界信号的光输入才能产生输出的器件, 对器件工作中的载流子数目是有一定的要求的, 器件只有拥有足够的光敏面积和厚度, 才能尽可能多地吸收光信号, 产生更多的光载流子. 因此基于碳纳米管光电探测的研究从单根碳管材料转移到薄膜碳管材料. 2016年, 王胜-彭练矛团队[96]基于溶液法提纯的高纯度半导体碳纳米管薄膜, 制备了大面积的碳纳米管光电探测器的阵列, 并在这种薄膜材料上实现了线性的光伏倍增.

碳纳米管CMOS器件与光电器件可以通过集成工艺自然结合, 有望为纳米电子和光电子电路的开发提供一个统一的平台, 而电子和光电子器件的集成, 特别是光通讯电路与高性能计算电路的集成有可能极大地提高计算机系统的能力, 为后摩尔时代的电子学带来新一轮的繁荣.

4

碳基CMOS集成电路技术发展面临的挑战

在碳纳米管材料制备, 高性能晶体管以及小规模集成电路方面, 我国的科研实力在世界上占据领先地位, 但是大规模集成电路方面与国外有一定的差距, 因此要发展碳基大规模集成电路, 使其能够成为打破芯片领域桎梏的突破口, 依旧任重道远. 目前技术研发的障碍与难点可以分为四个部分: 高质量阵列碳纳米管的大面积低成本制备, 碳纳米管器件性能稳定性以及均一性, 集成电路设计所需的EDA平台, 碳基集成电路的材料标准、工艺流程的确立.

高质量阵列碳纳米管的大面积低成本制备

碳纳米管集成电路批量化制备的前提是超高半导体纯度、顺排、高密度、大面积均匀的碳纳米管阵列薄膜, 且需将制备成本降到最低以提高竞争优势. 2013 年, Franklin提出[97], 半导体纯度超过99.9999%、密度达到100~200根/μm, 取向角<9°, 才可用于实现超大规模高性能集成电路. 这是因为碳纳米管中的金属碳纳米管会导致设备短路, 只有极高半导体纯度才能获得高良率的芯片. 此外, 高性能芯片必须精确地控制各个碳纳米管之间的距离, 间距过大意味着碳纳米管密度低, 晶体管的驱动能力不足, 而若间距太小即碳纳米管太密的话, 相邻碳管之间会出现静电屏蔽, 导致栅控能力降低. 长期以来, 学术界发展了多种制备、提纯、排列碳纳米管的方法, 但是始终无法达到实用化标准[41~44]. 这使得碳纳米管晶体管和电路的实际性能远低于理论预期, 甚至落后于相同技术节点的硅基技术至少一个量级.

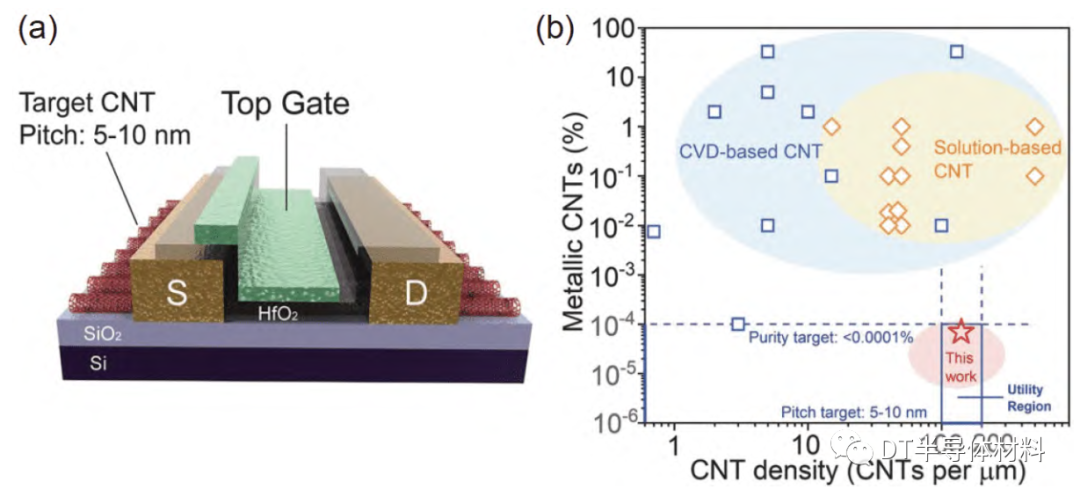

图 10 (a) “DLSA”法制备晶圆级阵列碳管原理示意图[48]; (b) “DLSA”法在4寸硅晶圆上沉积阵列碳管的光学图像及碳管截面的TEM图像; (c) 2.5 V的工作电压下65个CNT-RO的功率谱; (d) 最高振荡频率为8.06 GHz的环振电路功率谱 (网络版彩图)

2020年, 北京大学彭练矛-张志勇团队[48]通过多次分散提纯以及维度自限制的碳管排列——“DLSA” (图10a, b), 得到大面积, 高半导体纯度, 排列均一的阵列碳管, 突破了关键的材料瓶颈, 且以此为基础制备出的器件和电路在真实电子学表现上首次超过了硅基产品, 这意味着碳基集成电路已经初步具备产业化基础. 基于此种材料, 研究团队还批量制备了场效应晶体管和环形振荡器电路, 其中环形振荡器电路的成品率超过了50%, 最高振荡频率达到8.06 GHz, 远超已发表的基于纳米材料的电路性能, 且首次超越相似尺寸的硅基CMOS器件和电路(图10c, d). 虽然碳纳米管材料制备取得了突破, 但其距离其大规模应用还存在诸多挑战. 例如, 在纯度方面, 目前碳纳米管的半导体纯度达到了“6个9”, 但是对于极大规模集成电路应用来说, 还需要再提升2~3个数量级. 然而, 对碳纳米管进一步提纯会增加工艺步骤和成本, 降低产量. 此外, 如何表征极高的纯度本身也是一个挑战. 同时, 基于溶液分散和排列的碳管, 表面会包覆聚合物, 这些聚合物不仅会影响晶体管的源漏电极的接触性能, 也会影响栅介质层制备以及界面态, 甚至降低器件和电路的工作稳定性与均一性. 因此, 去除碳纳米管阵列中的金属管, 聚合物以及其它杂质, 得到洁净的高半导体纯度的碳管阵列薄膜, 是最终实现高性能集成电路的必要条件.

碳纳米管器件稳定性和均一性

碳纳米管晶体管尤其是目前主流的低功函数金属接触实现的N型晶体管在未封装的情况下暴露在空气中, 其性能会逐渐下降甚至失效. 热载流子效应、强电场下的雪崩击穿等都会影响碳纳米管晶体管的使用稳定性. 目前, 研究人员发现, 可通过多通道结构提高碳纳米管场效应晶体管的稳定性, 使其在几个月的时间内依然保持稳定的性能.

同时, 器件性能的均一是制备集成电路系统的必要条件, 不同器件之间的阈值电压、驱动电流、开关比等参数的波动需稳定在一个较小的范围内, 否则不仅扰乱电路的逻辑输出, 对整个电路系统的良率和长期可靠性也有很大的负面影响. 目前碳基电子的研究还主要集中在器件性能的提升以及中小规模电路的发展, 均一性方面的研究比较少. 2016年北京大学彭练矛课题组[98]基于碳管薄膜制备的P型晶体管具备高均一性, 阈值电压波动可以控制在34 mV以内, 并以此为基础制备高良率的中等规模集成电路. 2019年胡又凡课题组[19]基于碳管薄膜制备了晶圆级别高良率的可降解电路, 其中TFTs的阈值电压波动和反向器的转换电压波动范围分别控制在55 mV和60 mV. 这保证了中小规模高性能碳基电路的实现.

图 11 碳纳米管通用计算芯片RV16X-NANO[59]. (a) RV16X-NANO的制作流程图以及三维缩放渲染示意图; (b) CNFET- CMOS工艺原理图; (c) 150 mm晶圆上包含30个模块, 每个模块包含10400个CNFET-CMOS数字逻辑单元; (d) P型晶体管与N 型晶体管对称的输出性能 (网络版彩图)

但是真正投向实际使用的超大规模集成电路对均一性的要求更为苛刻, 现有碳纳米管晶体管的性能与高集成度难以兼顾, 这导致芯片整体性能不足. 以麻省理工学院2019年发布的全球首个碳纳米管通用计算芯片RV16X-NANO为例(图11)[59]. 虽然该芯片的规模与英特尔1985年发布的80386芯片相当, 但其在运行频率上和80386芯片仍有不小差距. 80386的运行频率为16MHz, 而碳纳米管芯片的最大频率仅为1.19 MHz. 造成这种差异的原因在于电子元件的电容太大以及晶体管的驱动电流有限. 单个硅晶体管可达到大约1 mA/μm的电流密度, 而该碳基芯片中晶体管只有约6 μA/μm的电流密度 (图11b~d). 尽管北京大学彭练矛- 张志勇团队已经实现了电流密度高达1.3 mA/μm的碳管晶体管, 超过了对应技术节点硅基CMOS器件, 但是由于工艺稳定性以及器件均一性的限制, 还未能实现大规模的集成电路.

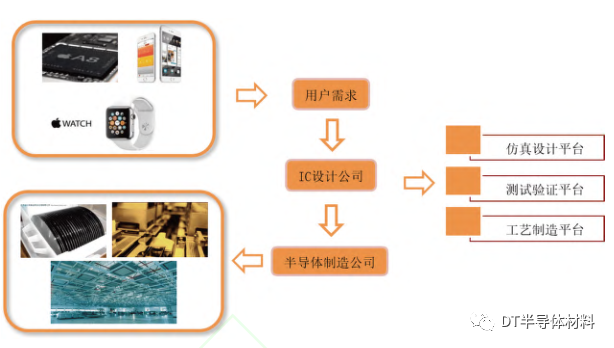

集成电路设计所需的EDA平台

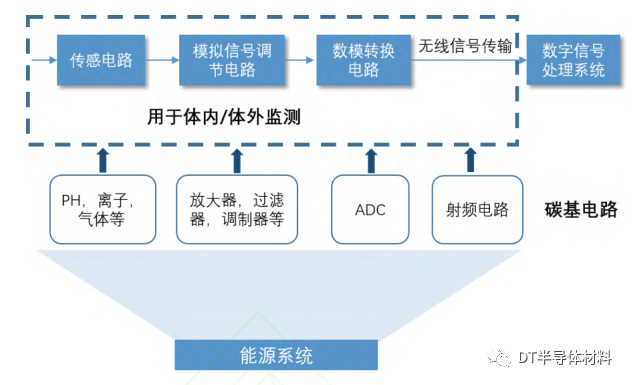

半导体产业链环节众多, 除了上述提到的材料和集成电路的制备外, 系统电路的设计优化也是一个重要模块, 包括仿真设计电路、检查缺陷、判断功能实现等等, 这些需要EDA平台的帮助. 目前我国在EDA 工具研发方面处于劣势, 缺乏自主研发的EDA平台, 并受到国外的科技制约, 同时碳基集成电路所需要的晶体管模型与主流的硅基晶体管模型不同, 因此需要建立全新的基于碳纳米管的器件电路模型[99,100], 并开发一套完整的工艺设计工具包(Process design kit, PDK), 用作沟通IC设计公司, 代工厂以及EDA厂商的桥梁(图12).

图 12 EDA平台在用户需求与半导体制造之间发挥桥梁作用 (网络版彩图)

材料指标, 表征方法, 工艺流程标准的建立

不同的电子器件应用对碳纳米管材料会有不同的要求, 即使是数字集成电路, 不同技术节点下的碳纳米管CMOS器件对材料也有不同要求指标. 因此建立阵列碳纳米管薄膜材料的标准, 包括衬底类型、碳纳米管半导体纯度、阵列密度、管径和长度分布、取向分布、缺陷密度、方块电阻分布、金属离子含量、表面聚合物含量, 以及其他反映材料完整程度的指标, 给出以上标准参数的测量方法、参考范围和测量仪器, 是碳纳米管材料在集成电路应用的基础.

碳基半导体产业是一个全新的生态链, 硅基生态链上的相关技术与工艺设备流程并不完全适用于碳基生态链, 例如碳纳米管材料的清洗、刻蚀等步骤需要特殊处理, 碳纳米管器件的模型也需单独建立. 当前硅基生产线内所有半导体设备需经过调试才能适合于碳基电路, 这个过程将消耗大量资金及时间. 当前, 碳纳米管晶体管尚处于实验中少量制备的阶段, 无法满足商业领域对碳纳米管晶体管快速低成本制备的需求. 未来, 还需进一步突破技术和成本限制, 在设备和器件等工艺方面建立成熟的规范流程, 降低成本, 提高稳定性, 向商用标准迈进.

总结与展望

综上, 碳纳米管在CMOS集成电路方面具有巨大的优势, 在光电、传感、显示以及柔性智能方面也具有很大的发展空间. 近年来碳纳米管在材料的制备, 器件性能的优化以及电路系统的搭建等方面已经取得很大的进展, 但实现碳基集成电路产业化和实际应用仍存在一些限制与挑战. 目前在我国芯片行业被桎梏, 硅基的发展达到摩尔定律极限之时, 碳基半导体为我国提供了一次“换道超车”的机遇. 我们认为, 根据材料和工艺的成熟度以及当前的发展形势, 碳基电子技术有望在3年内应用在传感领域, 5年左右应用在射频, 柔性智能以及显示驱动等特殊领域, 10年后实现有实际价值的达到先进技术节点的碳基集成电路 (图13).

图 13 碳基电子技术发展路线图[19,101] (网络版彩图)

文章来源:知网

扫码,了解详情~

联系方式

Bella

手机号码:+86 137 3842 2830

邮箱: Chanel@polydt.com

Luna

手机号码: +86 18657495805

邮箱: luna@polydt.com

Mable

手机号码:18989362825

邮箱:liushuang@polydt.com