数字阵列雷达可实现发射波形产生与接收信号处理的全数字化处理,在发射时由数字波束形成器给出发射波束扫描所需的幅度和相位控制字,在波形产生时预置相位和幅度,经上变频与放大后由辐射单元发射出去,信号在空间进行功率合成。

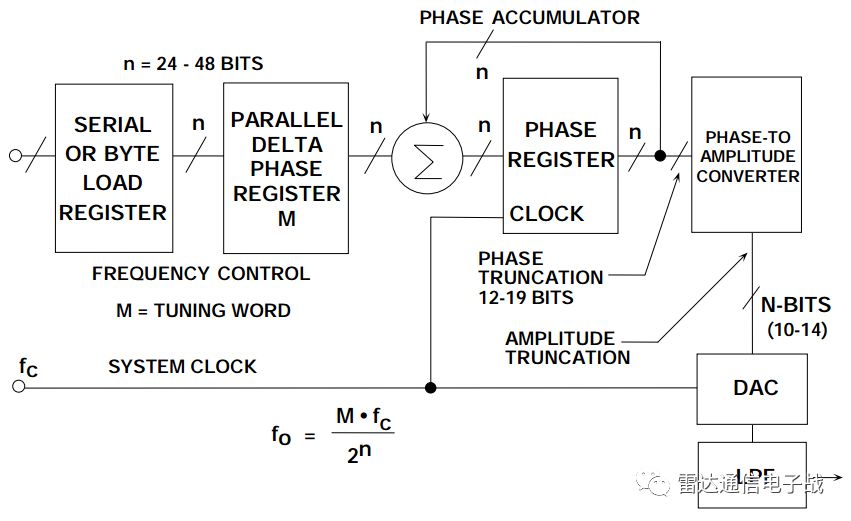

数字阵列雷达在发射端用直接数字频率合成技术(DDS)在数字域形成发射波形,在接收端用模/数转换器(A/D)将接收的模拟信号变为数字信号,进行后续处理。

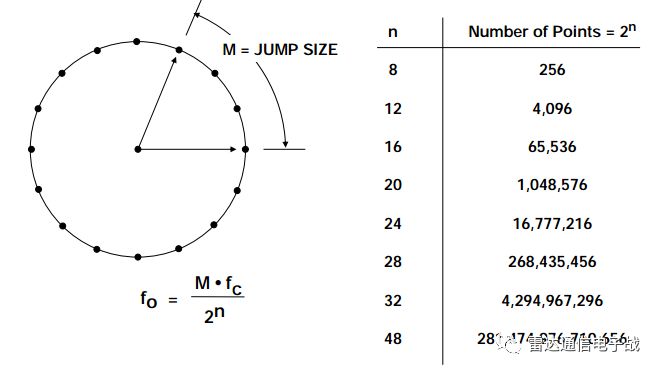

数字阵列雷达的发射系统也是一个多通道系统,每个天线单元对于一路数字T/R通道,通过改变每个通道DDS产生波形的初始相位来控制阵列相位,达到控制波束指向的目的。每个通道的信号参数(例如频率、带宽、时宽和调频形式等)都独立可控,因此波束形成的灵活性很好。DDS已广泛应用于信号产生器、电子战、数据数字传输等场合。其关键部件包括:数模转换器、相位累加器、存储器等。DDS的优点有:频率转换速度快、频率步长精确、相位连续、输出平衡无瞬变过程,同时它还具有结构简单、体积小、重量轻和成本低等优点。DDS系统的核心是相位累加器,其内容会在每个时钟周期更新,存储在相位寄存器中的数字M就会累加至相位寄存器中,相位累加器的截断输出用作正弦(或余弦)查找表的地址,每个地址对应正弦波从0~360度的一个相位点,相位信息通过查找表映射至数字幅度字,进而驱动DAC。

对于n位的相位累加器,存在2的n次方个可能的相位点,如果时钟频率为fc,则输出正弦波的频率计算公式如上图中所示。

在实际DDS系统中,通常相位输出会被截断,这样可以大大减小查找表的大小,并且不会影响频率分辨率,但是会最终输出会增加相位噪声。当改变M的值,频率可以立即改变,不会出现相位不连续,加载频率字到缓存寄存器所需的时钟周期数决定了输出频率的最大改变速率。

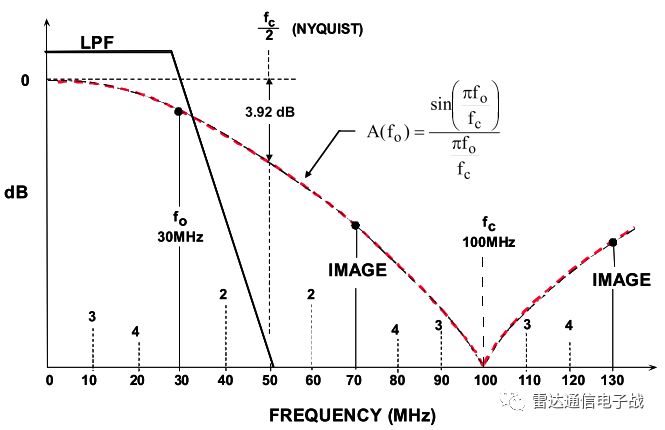

由奈奎斯特采样准则可知,时钟频率(采样频率)必须为输出频率的两倍以上,实际最高输出频率限制在1/3时钟频率范围内。如图假设输出频率为30MHz,时钟频率100MHz,在重构DAC后需要加一个抗混叠滤波器(LPF),用以滤除混叠的频率(100-30=70MHz)。但是,DDS的输出频率的高阶谐波也会因混叠折回带内,无法通过抗混叠滤波器去除,例如第三个谐波90MHz折叠的10MHz和第四个谐波120MHz折叠的20MHz。

发射数字波束形成将传统相控阵发射波束所需要的幅度加权和移相从射频部分移到了数字,波束扫描更快更灵活,通道的幅相校正易实现;由于幅度和相位的控制精度更高,容易实现低副瓣发射波束;另外,对于大阵列和长脉冲信号,波形产生时可通过内插产生任意数字时延,克服孔径渡越的问题。

免责声明:本公众号目前所载内容为本公众号原创、网络转载或根据非密公开性信息资料编辑整理,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系。我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。本公众号拥有对此声明的最终解释权。

↓ 戳阅读原文 ,加入知识星球,精彩继续,你若喜欢,分享/点赞/在看!