点击蓝字 关注我们

差不多4个月没更新了,除了懒是一方面,还有就是2021年以来各种新势力造车的第二轮崛起,看得我眼花缭乱,变得有点迷茫了。

随着域控时代的来临,BMS硬件本身越来越像一个传感器,然而小小的传感器也有大大的能量。这次继续来写BMS相关方面的内容,简单一点就是关于BMS的最基本功能,电池的采样误差来源。

一

●

电池单体电压误差要求

首先来介绍一下单体电池电压的采集,在我刚开始接触BMS的时候,那时候的单体电池采样芯片的采样误差普遍是在5~10mV,只有凌特(现在被ADI吃掉了)的LTC系列的采样芯片误差能够做到5mV以内,这时候我们的系统工程师给我提的需求是要求单体电池采样误差在5mV以内,这么提要求其实就是告诉我,芯片不用选了,就用凌特的LTC。

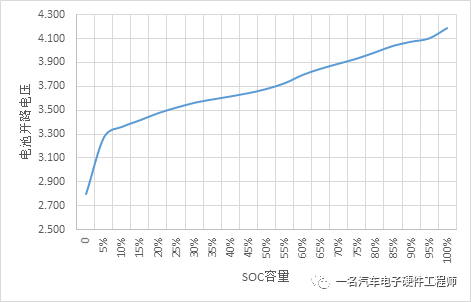

基于这个系统需求的前提下,我了解到当时SOC的系统目标是SOC的误差要求在1%以内,那么就反推一下,如果需要保障电池单体的SOC误差在1%以内,于是我在网上随便找了一组电池的OCV数据,做成曲线大概就是下面这个样子。在45%的SOC到50%的SOC这一段,电压相差仅35mV,相当于平均每1%的SOC对应的电压值变化时7mV,这样看来提出5mV的单体电压采样误差似乎并不过分,只是我找不到当年那个电池的OCV曲线了。

二

●

电池单体电压的采集

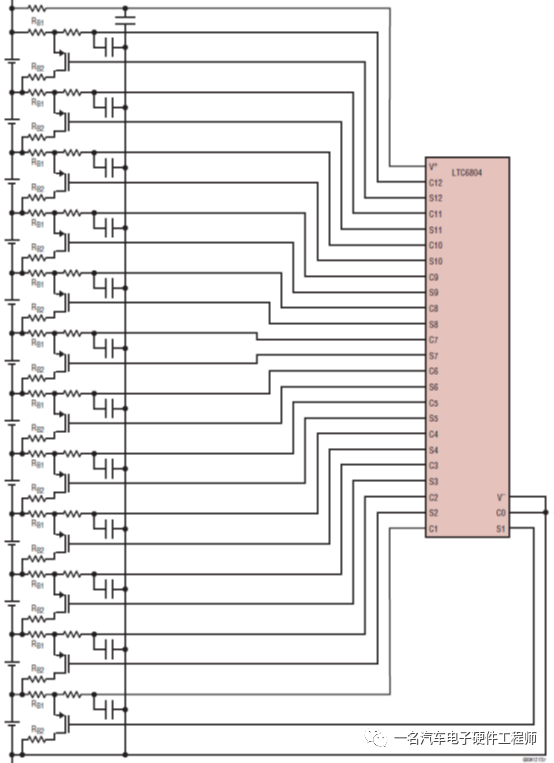

电池单体通过串联的方式依次叠加,采样芯片的采样通道也按照次第的顺序往上叠加,对于电池单体采样通道上的滤波电路,基本上目前所有的采样芯片都是100Ω的串阻,然后加上一个滤波电容,通过经典的RC滤波电路来实现。

三

●

电池单体电压采样的误差来源

BMS的误差来源主要分为3个方面,1是芯片自身的误差,包括ADC偏移,增益误差等,2是来自于采样线束上的压降,3是来自于软件开发时可能存在的ADC位数误差。

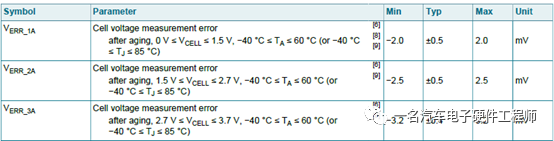

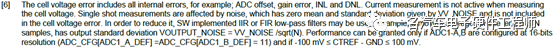

第一点:芯片自身的误差一般在芯片的规格书上有体现,一般就是芯片手册中写误差的那一个章节,会标注芯片最大的采样误差是多少。而这个采样误差就是基于芯片自己内部的硬件设计决定的,包括芯片的采样速率,芯片内部的ADC类型,以及芯片的漏电流等,在实际使用的时候,芯片自己的误差基本上都会少于它所标注的误差,毕竟为了避免部分较真的人,写上去的参数肯定是最差的那个值,然而绝大多数芯片都是远远优于这个参数的。

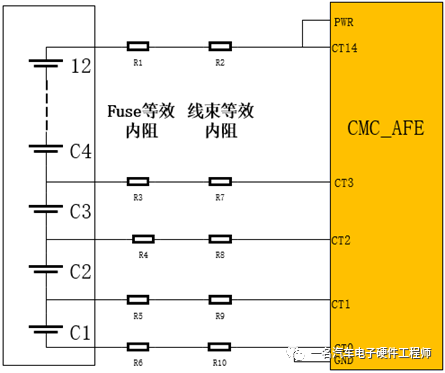

第二点:采样线束上的压降,采样线束其实分为两个部分,对于目前市面上绝大多数方块电池,电池的采样线先是从芯片的极柱通过FPC连接到电池模组的接插件,然后线束再通过这个接插件连接到BMS上去。大概就是下面这个样子的(图片是百度来的)。

所以实际上从电池连接到AFE采样芯片是经过了两段线束,一段就是FPC上的走线,另外一段就是连接到BMS上的线束。

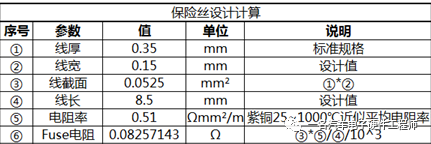

FPC上的阻抗大概就是0.08Ω,另外假设采样线束长度1.5m,线材为24AWG,那线束的阻抗大概是0.091Ω/m * 1.5m=0.14Ω。这样对于一段采样线束,采样路径上的阻抗大概就是0.22Ω,四舍五入取个0.2Ω。

对于一般的采样通道,在非均衡的情况下,最大漏电流不超过100nA。这样的话在线束上的压降就是0.2Ω*100nA=20nV?这个电压太小了,我不知道公众号怎么打出来指数,看一下这个单位,就知道是可以忽略的。

但是对于芯片的最高节采样通道,通常是与芯片的供电共用一根采样线束的,这个通道上流过的电流一般在10mA左右,所以对于最高节的电压采样通道,在线束上的压降就比较可观了。能够达到0.2Ω*10mA=2mV。

所以从上面来看,线束上的压降对最高节电池的电压采样影响比较大,当然针对第一节电池,有地线上的压降也会影响第一节电池的采样。因此线束上阻抗的影响对第一节和最高节电池的采样是有一定的影响的。

第三点:软件开发时省略掉的ADC采样分辨率。一般的采样范围是0~5V。对于12位的ADC,每一位大概对应的电压是1.22mV。如果AFE提供的是16位的ADC,而软件开发中由于其他资源的限制,只使用了前12位ADC的值,那么在采样的时候,最大可能由于舍弃掉后4位ADC值带来的误差就是1.22mV,再加上DBC中定义的分辨率,可能只能显示以1mV为单位的电压,那又会因此带来一定的误差。

●

总结

往期推荐

UDS的基本概念-从入门开始

UDS的那些服务—DID、DTC都是怎么来的?

UDS的那些服务-$10诊断会话

BMS系列(2)——SHUNT、HALL、磁通门

觉得有用点击右下角在看↓