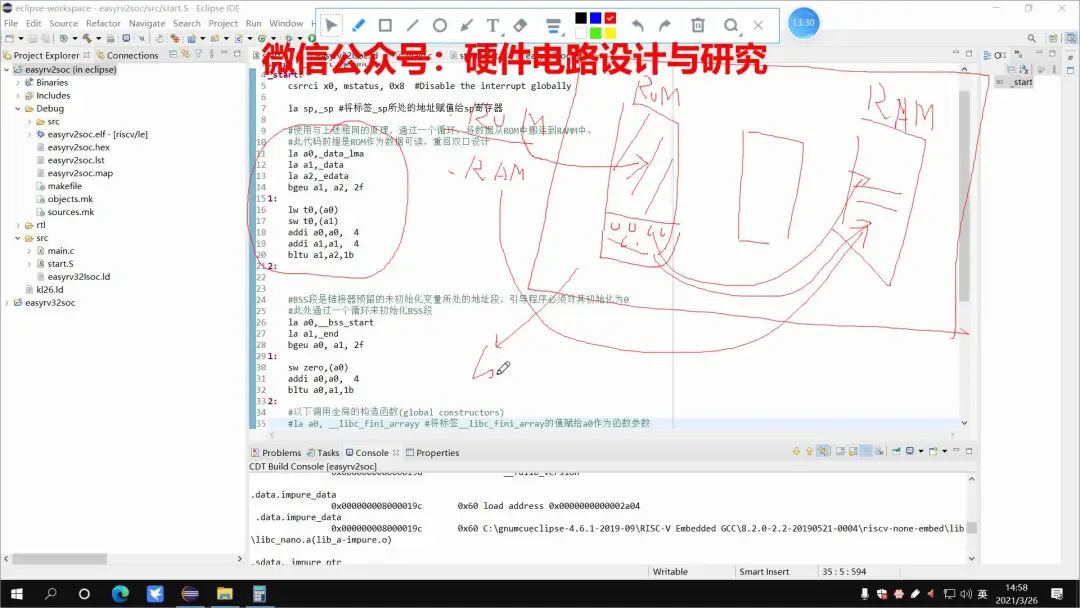

本次集创竞赛中,我们使用了自己写的两级流水线的RISCV处理器,具有性能适中,资源占用很小,准备把主要的FPGA资源留为图像处理加速。我们可以在eclipse编程时自动生成所需的rom/ram初始化文件,具体原因参见以前的培讲视频,本次推文主要讲讲如何设置eclipse以实现自动分离输出ROM_RAM文件,主要使用命令如下:

#!/bin/bash

riscv-none-embed-objcopy -O binary easyrv2soc.elf easyrv2soc.text --only-section .text*

hexdump -ve '1/4 "%08x\n"' easyrv2soc.text > easyrv2soc.rom

rm easyrv2soc.text

riscv-none-embed-objcopy -O binary easyrv2soc.elf easyrv2soc.data --only-section .*data*

hexdump -ve '1/4 "%08x\n"' easyrv2soc.data > easyrv2soc.ram

rm easyrv2soc.data

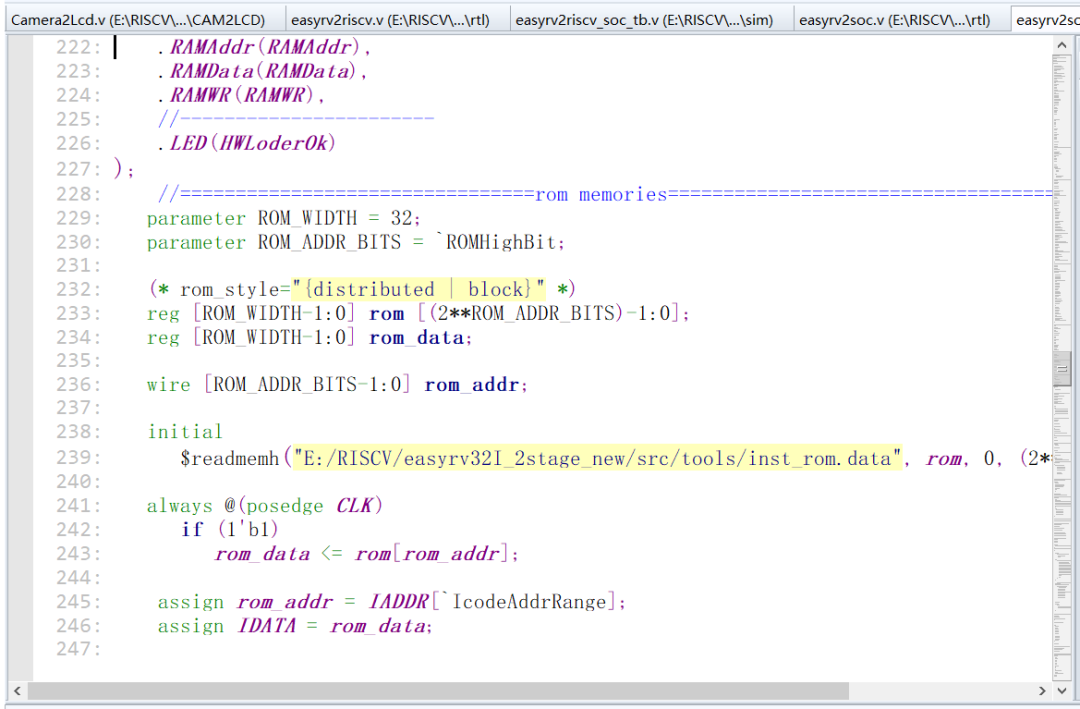

以上编译命令生成easyrv2soc.rom ,用于初始化verilog的ROM文件:

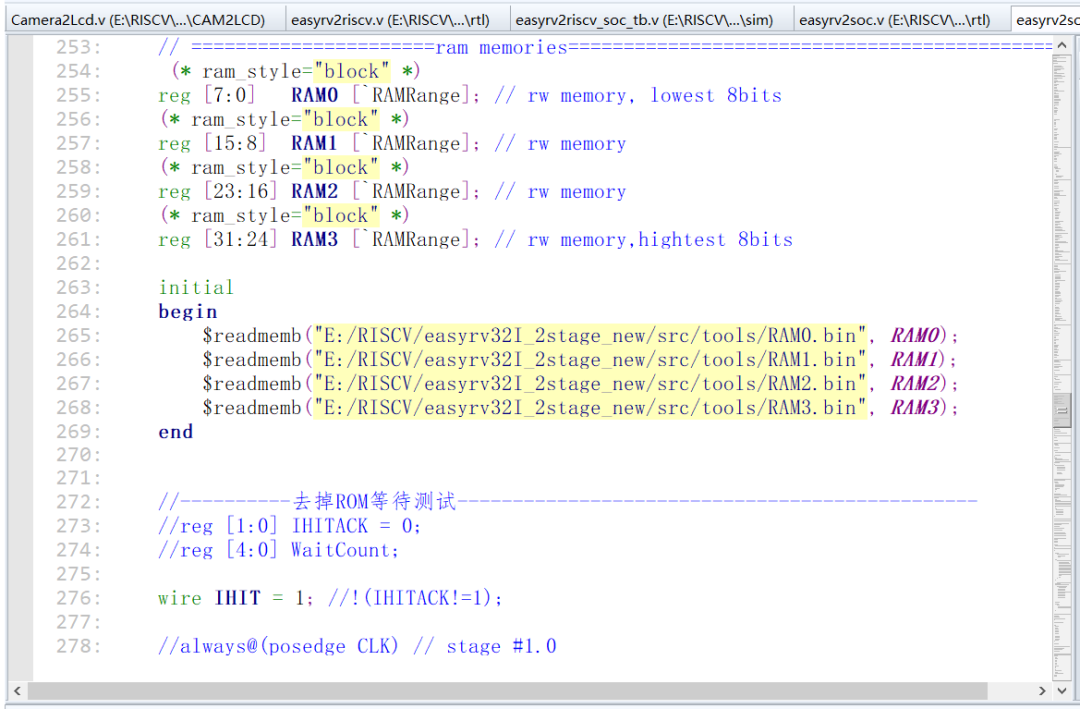

以上编译命令生成easyrv2soc.ram后 ,再使用python脚本,把32位的easyrv2soc.ram文件输出4个8位数据的RAM文件,用于初始化verilog的4个8位宽的RAM文件;

注意文件名可以任意选取与上面不同,但是必须与你自己的设计对应一致。

系统下载运行后,如果仅是修改了C语言的程序(是riscv的运行程序,非硬件加速的HLS的c程序),则无需重新编译vivado工程生成bitsteam文件,可以直接用USB2SPI端口,通过easyrv2soc的HW_Loader功能把以上生成的rom/ram文件直接下载到easyrv2soc的rom/ram中,此部分功能虽然已经verilog实现,还需要集创赛的同学们尽快仿真测试哈。

视频讲解:

其他东东:

eclipse设置的讲解

集成竞赛准备6_公开

爽呀,拿着手机玩python