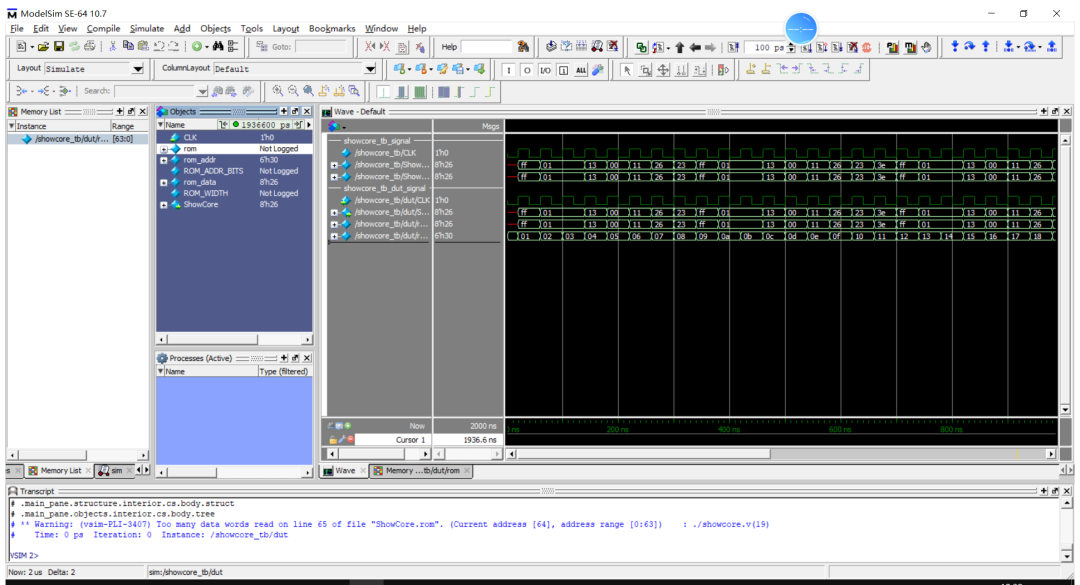

easyrv2soc中的各个模块,需要大家做仿真验证,仿真验证分为前仿(功能仿真)和后仿(时序仿真),后仿是带NET时延的仿真,需要加载器件模型库文件,比前仿更精确,基本步骤和前仿类似,由于系统工作频率不高,大家先对easyrv2soc中的各个模块做前仿即可,后仿以后视情况再说。这次用modelsim脚本自动仿真验证,详细脚本注释说明随后发群里。

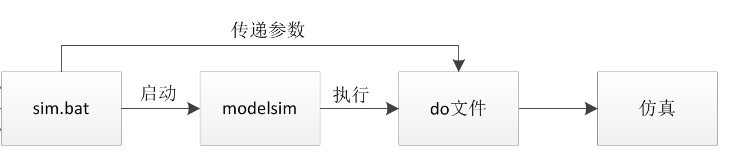

通常情况下,用硬件描述语言(HDL)设计完逻辑电路之后,我们接着要做的一件非常重要的事情就是对逻辑电路的功能进行仿真。那用什么软件对其进行仿真呢?用得比较多的是Mentor公司的modelsim或开源的iverilog,modelsim是业界最优秀的HDL仿真软件。而大多数人习惯基于它的图形界面操作来对逻辑电路进行仿真。这些操作看似简单方便,但是图形界面仿真会消耗很多时间做各种设置,不如do脚本仿真快捷。通过批处理和脚本文件之间的调用、传递参数来启动仿真的,如下图:

Modelsim 常用脚本命令

1)vlib 创建library,如创建名为work的library的指令为,vlib work

2)vmap 逻辑库名(如work)与指定目录之间定义一个映射。

vmap <logical_name>[<path>] 把逻辑库映射到指定的物理库上,若不定义<path>,此命令返回现有映射。

3)vopt 编译后进行全局优化

4)vlog 编译.v文件

5)vsim 调用VSIM仿真器

6)add wave 添加波形

add wave -divider <divider_name> 在波形列表中添加分割线类别

add wave –radix <type> 定义显示进制形式,<type>有binary, ascii, decimal, octal, hex, symbolic, time, and default

7)virtual type 在图形界面中将信号值显示为字符串

8)virtual function 在图形界面中建立新的信号,方便将需要的信号放在一个波形窗口查看

视频讲解: