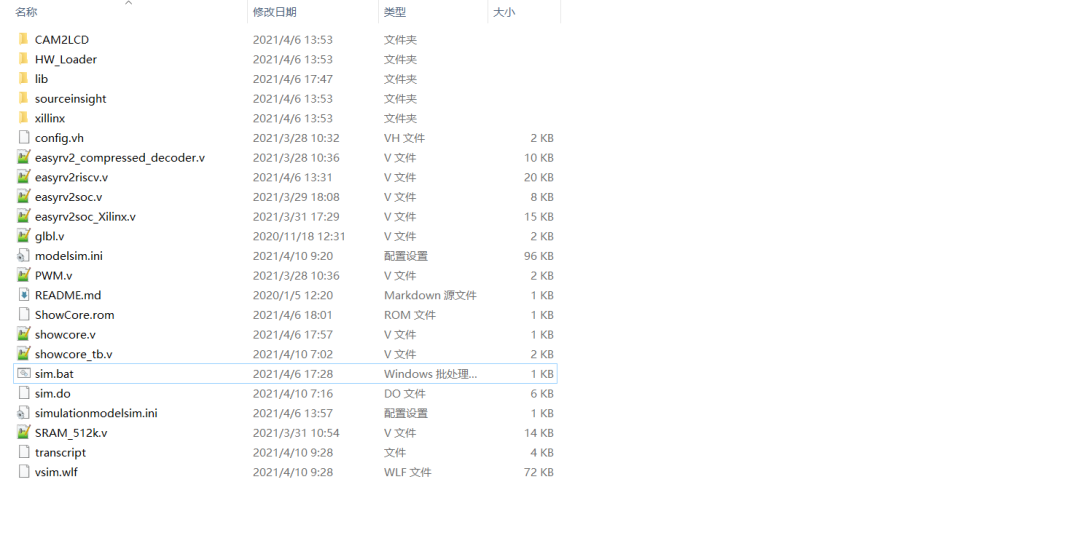

要求:对顶层module easyrv2soc_Xilinx(....)实列化进行仿真验证,由于其中有多个模块功能集成,需要针对不同功能时对easyrv2soc_Xilinx加载不同的控制信号,甚至easyrv2soc_Xilinx中的riscvc处理器加载不同的ROM程序、RAM加载不同的初始化数据,用modelsim对功能和riscv程序运行情况进行全面真实的仿真(目前还需要大家自己写和加载一个512k*8bits的SRAM的verilog模型)。本次推文主要小结、介绍如何对带vivado的ip核的verilog设计进行仿真。

脚本文件与以前的脚本有几点不同:

1)增加了xxx_sim_netlist.v文件的编译,这是所用的IP核,在自己示例化的IP核文件夹里找,例如:

vlog -work work "E:/RISCV/easyrv32I_2stage_new/rtl/xillinx/easyrv32I_2stage/easyrv32I_2stage.gen/sources_1/ip/clk_mmcm/clk_mmcm_sim_netlist.v"

有多数IP就有加多数xxx_sim_netlist.v,目前设计只用了三个vivado自带的ip,这里只演示了其中一个

2)增加glbl 模块编译,这是xilinx 自带的有关全局复位的模块

3)vsim仿真里增加了 -L选项,如何加?见“视频三:modelsim后仿第三步:时序与ip核仿真”

4)“视频三:modelsim后仿第三步:时序与ip核仿真”介绍了如何学习和查找modelsim的命令参数

视频一:modelsim后仿第一步:编译xilinx的仿真库

视频二:modelsim后仿第二步:配置xilinx的仿真库

视频三:modelsim后仿第三步:时序与ip核仿真

光电赛的童鞋们关注以下三本书籍,相关方案以后密谋哈