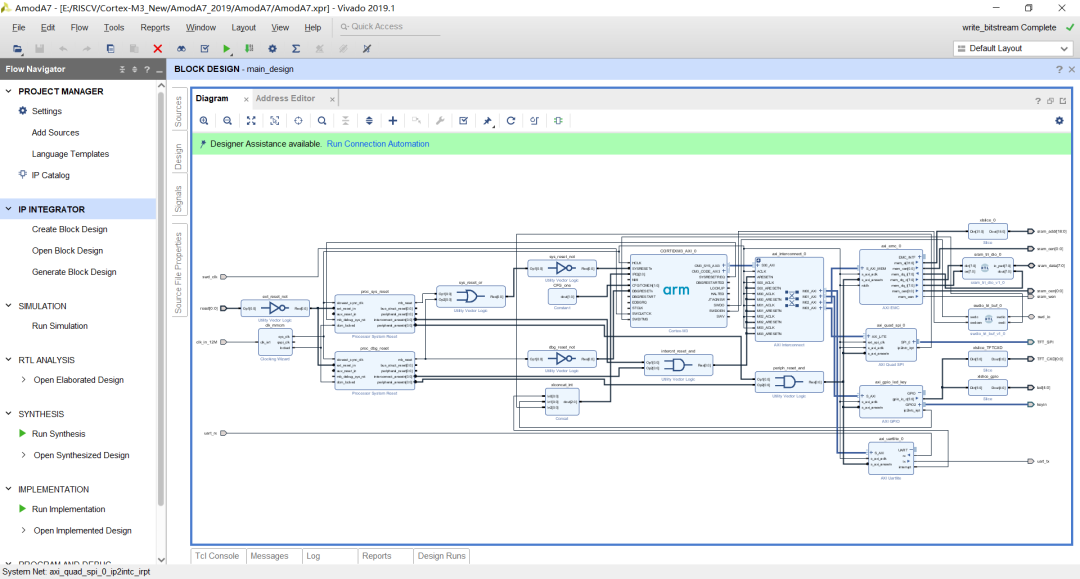

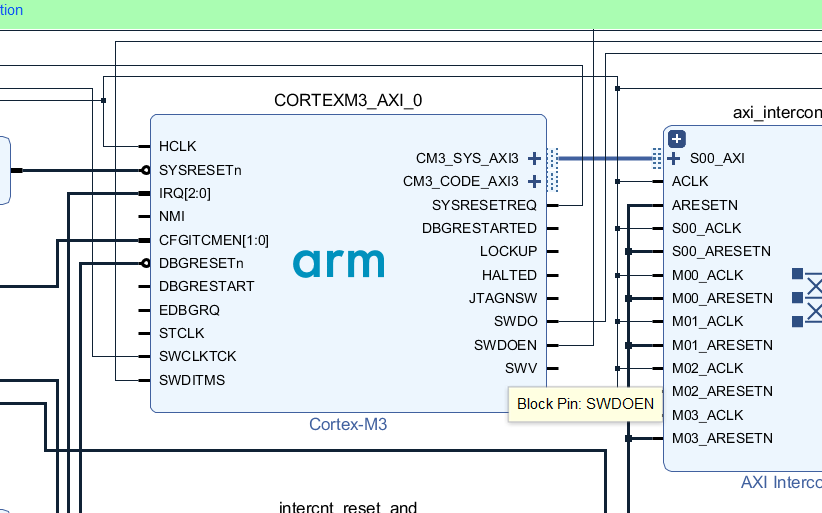

我们用cortex M3软核在xilinx的artix7a35T FPGA上实现一个简单的SOC系统后,如何进行程序的调试?这里使用keil MDK软件开发环境,首先要把你的st link v2调试器的GND、swdio、swclk三个引脚与fpga的对应引脚连接,而fpga的swdio、swclk两个引脚,是你在构建cortexM3系统时自己定义的,例如下图:

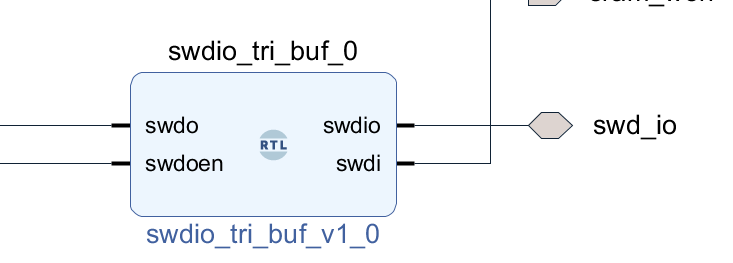

由于swdio是双向端口,所以在arm内核的引出脚swdo和swdi上要加一个简单的三态门控制,控制端为arm内核的引出脚swdoen,模块与实现代码如下:

module swdio_tri_buf(

inout swdio,

input swdo,

input swdoen,

output swdi

);

// assign swdi = swdio;

// assign swdio = (swdoen) ? swdo : 1'bz;

IOBUF swd_iobuf_inst(

.O(swdi),

.I(swdo),

.IO(swdio),

.T(~swdoen) // 3-state enable input, high=input, low=output

);

endmodule

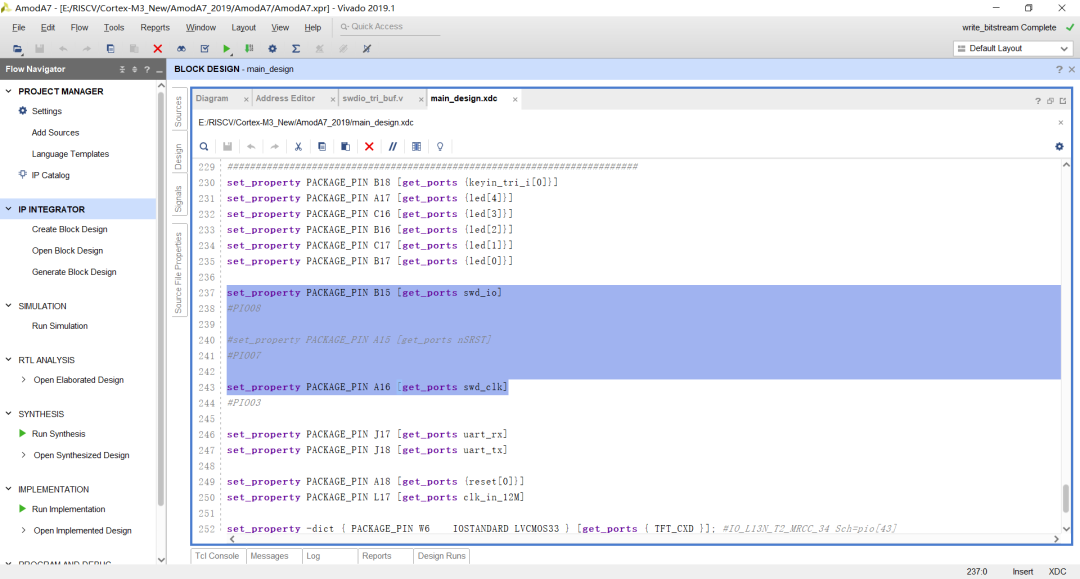

在此示例中我们可以通过io引脚约束文件,把swdio、swclk两个引脚定义到你认为合适的任意IO端口上:

swdio、swclk两个引脚定义位置不同,可能会略微影响时序,但是swd是几M的慢速系统,影响不大,如果影响明显也可在fpga布局布线时加入时序约束。

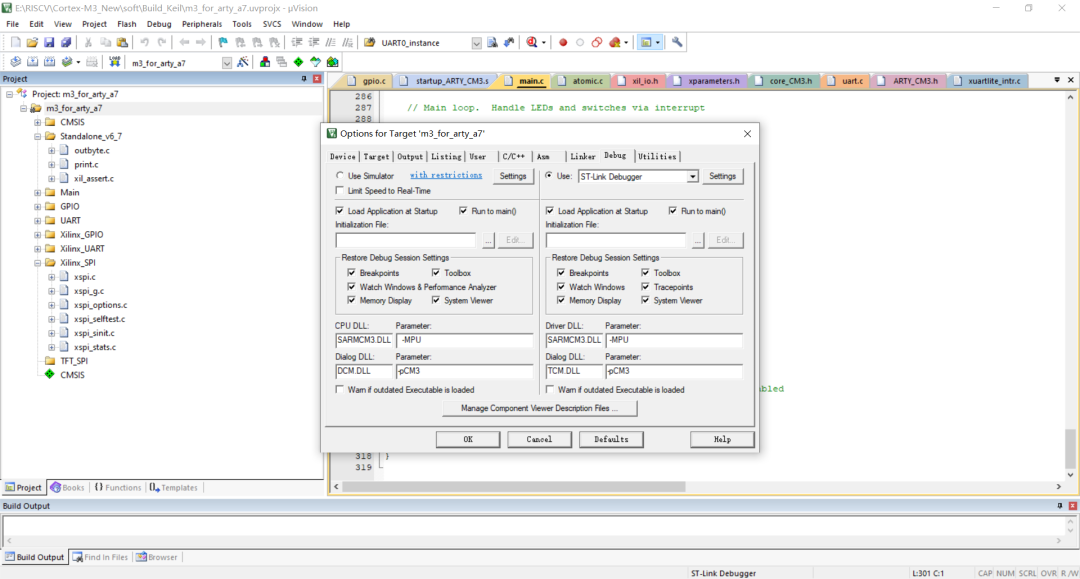

在项目的option中选择debug,如下图所示,选择stlink degguger:

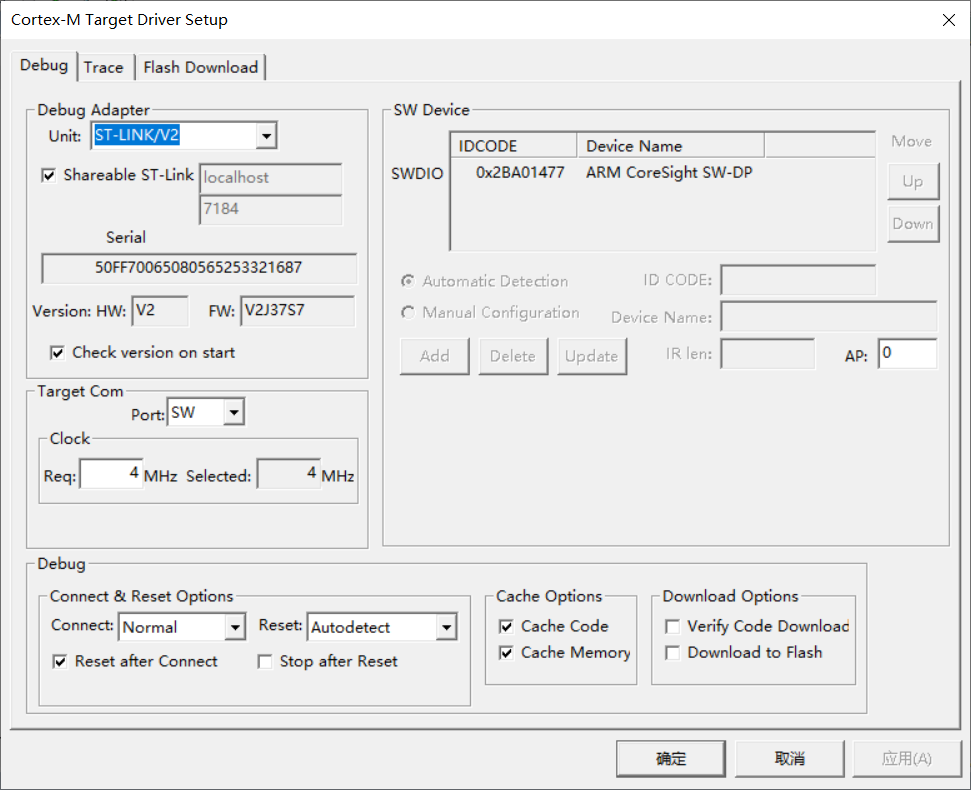

再进入setting,如果连接和设计无误,keil会自动找到调试器,显示如下图所示,注意我们这里显示的stlink固件版本号为V2J37S7,如果是太老的版本是无法进行后续的调试的,一般此处系统会提示你是否更新固件版本号,应该选择更新:

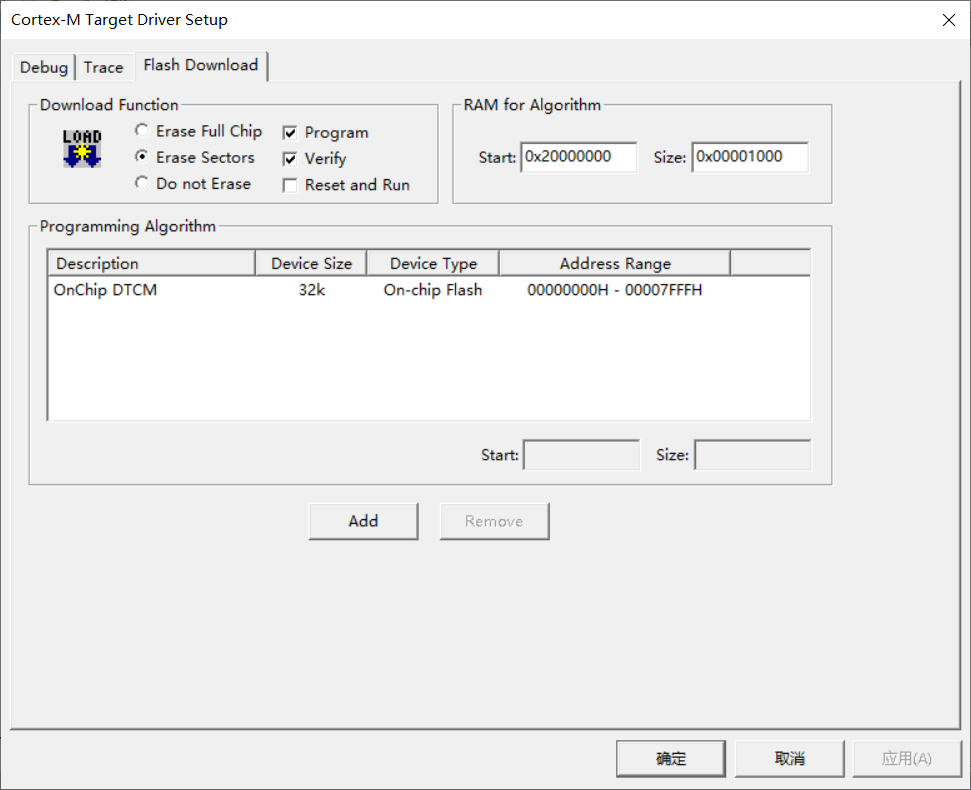

在此还需要配置flash download选项,如下图所示,点击add加入后面我们自己编译修改生成的FLM:

关于FLM需要输入较多文字,在此自己看后续视频讲解:

1.FlashDev.c文件修改

struct FlashDevice const FlashDevice = {

FLASH_DRV_VERS, // Driver Version, do not modify!

"OnChip DTCM", // Device Name

ONCHIP, // Device Type

0x00000000, // Device Start Address

0x00008000, // Device Size in Bytes (256kB)

1024, // Programming Page Size

0, // Reserved, must be 0

0xFF, // Initial Content of Erased Memory

100, // Program Page Timeout 100 mSec

3000, // Erase Sector Timeout 3000 mSec

// Specify Size and Address of Sectors

0x008000, 0x000000, // Sector Size 8kB (8 Sectors)

SECTOR_END

};

2.FlashPrg.c文件修改

int EraseChip (void) {

/* Add your Code */

memset((unsigned char*)0,0,0x8000);

return (0); // Finished without Errors

}

。。。。。。。。。。。。。。。。

int EraseSector (unsigned long adr) {

/* Add your Code */

memset((unsigned char*) adr,0,1024);

return (0); // Finished without Errors

}

。。。。。。。。。。。。。。。。。。

int ProgramPage (unsigned long adr, unsigned long sz, unsigned char *buf) {

/* Add your Code */

memcpy((unsigned char*) adr,buf,sz);

return (0); // Finished without Errors

}

视频讲解:

关注微信公众号:电路与电测