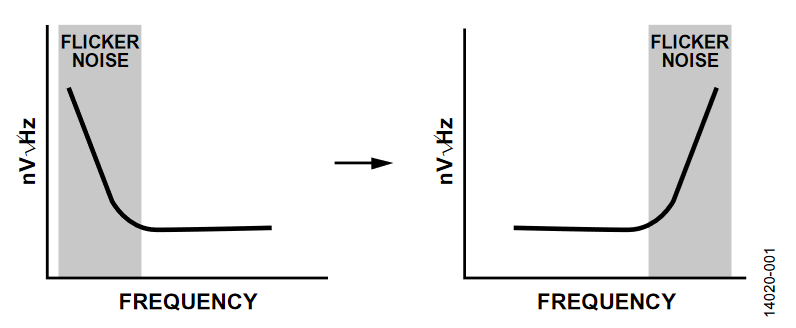

典型DPD应用模数转换器(ADC)中集成的缓冲器和放大器通常是斩波型。有关这种斩波实现的例子,可参见AD7124-8 和AD7779数据手册。需要这种斩波技术来最大程度地降低放大器的失调和闪烁噪声(1/f ),因为与其他工艺(如双极性工艺)相比,CMOS晶体管噪声高,难以匹配。通过斩波,放大器的1/f和失调转换到较高频率,如图1所示。

图1. 闪烁噪声(1/f )与斩波

在斩波转换过程中,开关的电荷注入会引起电流尖峰,进而使施加于ADC输入端的电压产生方向不定(流入和/或流出)的下降或尖峰。压降与连接到ADC输入段的传感器的输出阻抗成比例。

一般而言,数据手册不会提供电流峰值,因为它难以测量,而且不会增加任何有意义的信息。该信息之所以无意义,是因为缓冲器的斩波频率高于ADC的输入信号带宽。因此,输入引脚上添加的低通滤波器(用来消除高于奈奎斯特频率的频率或信号音,或用来降低耦合噪声)会对峰值电流进行平均,如图2所示。

图2. 输入电流与时间的关系

用电流表测量输入电流,一端连接到VDD/2,另一端连接到ADC的模拟输入引脚。

如果电流表连接到其中一个电压轨,由于输入电压裕量的关系,测得的电流可能高于数据手册中的规格值。

输入阻抗规格对精确计算直流误差没有帮助,因为与ADC内部输入阻抗引起的负载效应相比,输入偏置电流是最主要的贡献因素。

有两个规格与输入偏置电流相关:绝对电流和差分电流。绝对值(IABSOLUTE)是在任意模拟输入引脚测得的输入电流。差分输入电流(IDIFFERENTIAL)是在模拟输入引脚对之间测得的电流差。这仅适用于差分输入ADC。

输入电流产生一个失调电压(VOFFSET),后者与连接到输入引脚的阻抗直接相关。

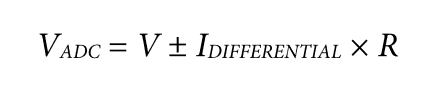

如图3所示,产生的失调电压一般为:

图3. 漏电流引起的压降

如果用运算放大器等低阻抗源驱动模拟输入引脚,误差将不很明显。

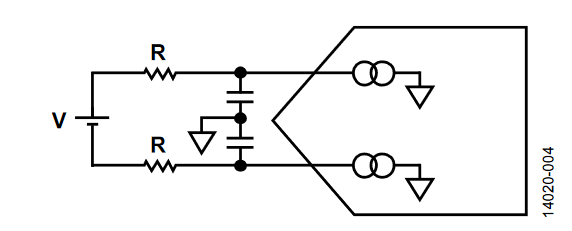

ADC测得的误差取决于施加的输入信号类型,例如是真差分输入信号还是伪差分/单端输入信号。

对于真差分输入信号,假设输入电阻(R)完全匹配,那么ADC测得的误差将是由模拟输入引脚对之间的差分输入电流引起,如下式所示:

其中,VADC为ADC输入电压。

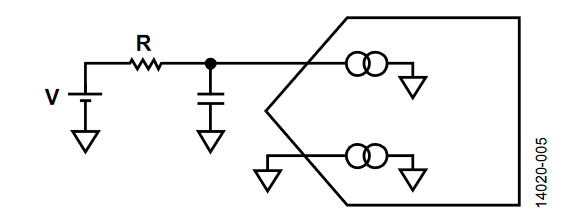

图4. 差分输入ADC

如果电阻不是完全匹配,则在差分输入电流贡献之外,电阻不匹配也会产生一个误差。

一般而言,假设电阻容差为1%,那么最差情况下的失调电压定义如下:

对于伪差分/单端输入信号,有两种情况:

一个模拟输入连接到低阻抗源(参见图5)。误差定义为:

图5. 伪差分/单端ADC

两个输入均连接到高阻抗源(参见图6)。误差与使用真差分信号的情况相同。

图6. 伪差分ADC

交流分量与输入阻抗规格直接相关。输入阻抗可以是阻性或容性。若输入阻抗为容性,则给定频率下的阻抗计算如下:

其中:

Zc为输入阻抗。

CIN为数据手册给出的输入电容。

fIN为输入频率。

举个例子,假设有8 pF电容和1 kHz输入带宽,则最小输入阻抗约为20 MΩ。

为使低通滤波器中电阻不匹配引起的误差最小,最好使用小电阻和大电容,因为电阻产生的失调和约翰逊噪声较低。

原文转自亚德诺半导体

立即扫码购买 ↑ ↑ ↑

关于世健 亚太区领先的元器件授权代理商

世健(Excelpoint)是完整解决方案的供应商,为亚洲电子厂商包括原设备生产商(OEM)、原设计生产商(ODM)和电子制造服务提供商(EMS)提供优质的元器件、工程设计及供应链管理服务。

世健是新加坡主板上市公司,拥有超过30年历史。世健中国区总部设于香港,目前在中国拥有十多家分公司和办事处,遍及中国主要大中型城市。凭借专业的研发团队、顶尖的现场应用支持以及丰富的市场经验,世健在中国业内享有领先地位。