备战电赛的同学们,北航学长的2019电赛回忆录下篇准时登场,是否给这身处闷热夏季的你带来一丝清凉?

顺便给大家预告一下,学长即将在硬禾学堂开设电赛系列直播课程。大纲这里看!

直播大纲

1.信号调理电路

a.阻抗匹配

b.信号放大/衰减

c.信号隔离

d.信号滤波/移相

e.测量转换电路

2.数字信号处理

a.采样定律

b.FFT分析

C.FIR/IIR滤波器

d.数字检波/鉴相

e.自适应滤波器

回归正文,紧接着上篇的内容继续……

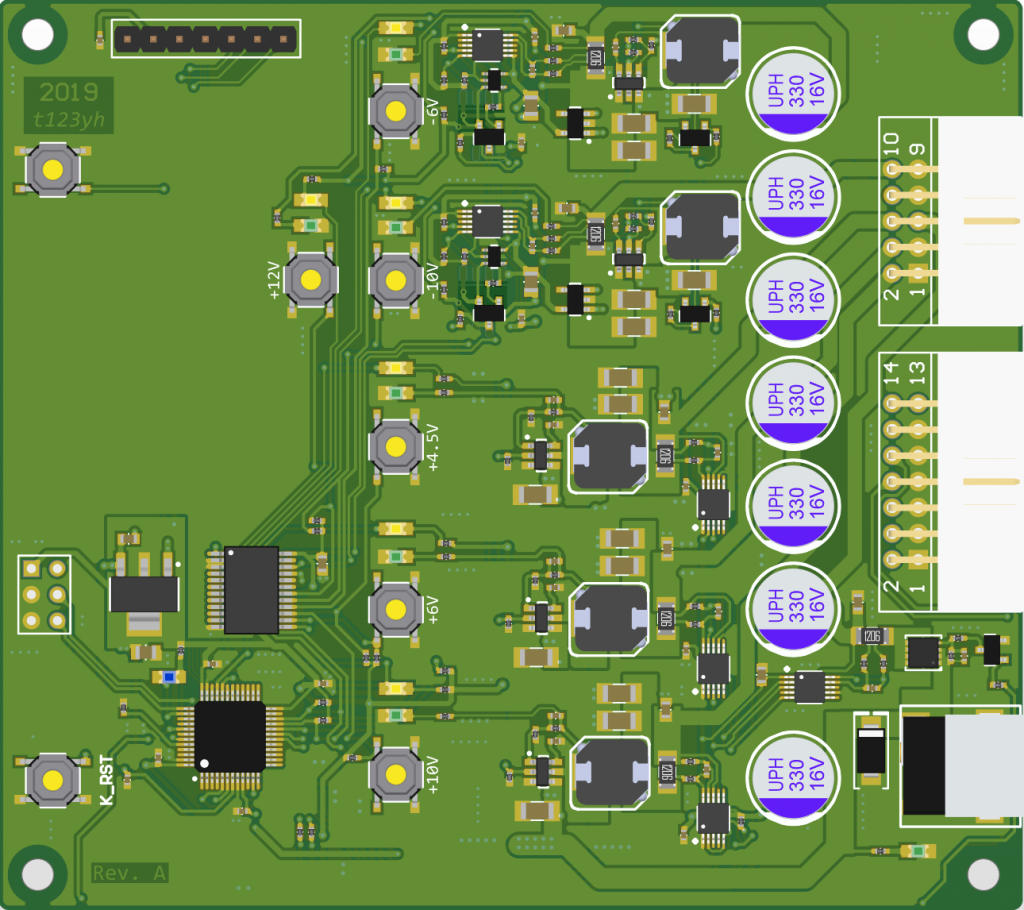

电源模块

电源模块输入单电源5V,输出+4.3V,+6V,±9V和±12V总共5组电源。前两组主要用于数字芯片供电,后两组原本设计给运放之类的芯片使用(但最终几乎没有使用)

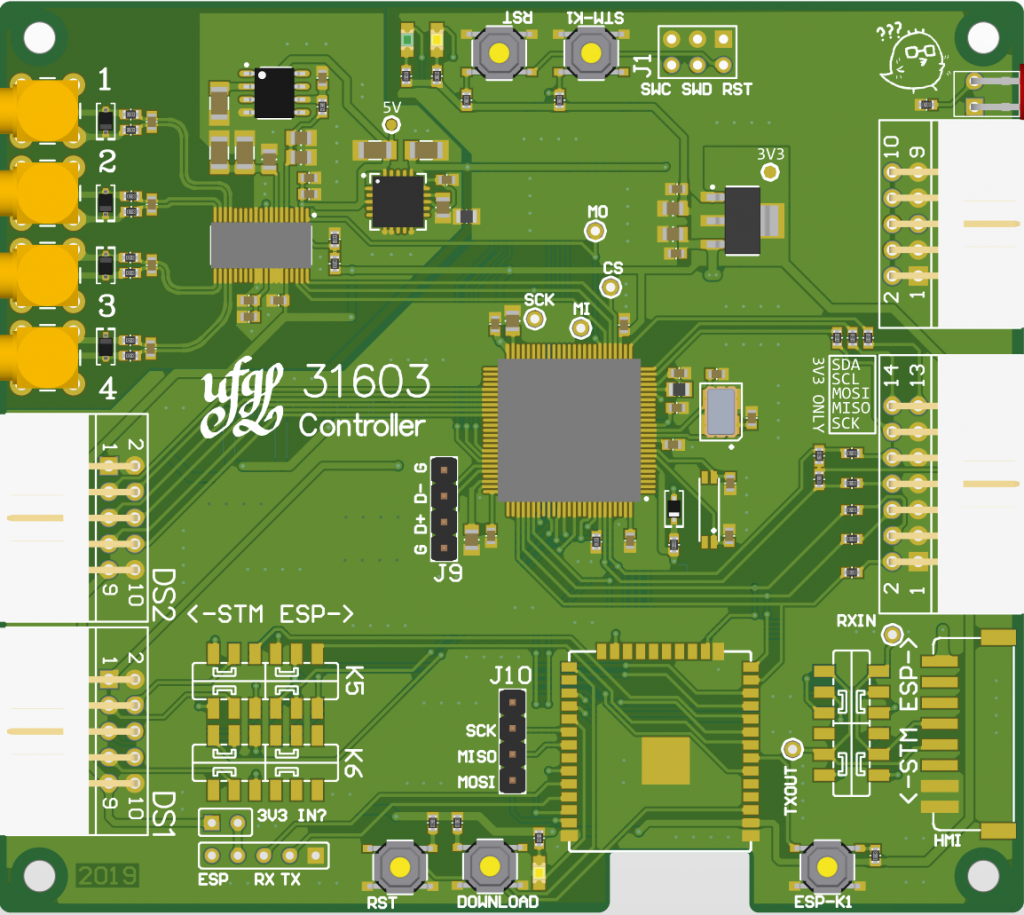

控制与采样模块(UFGL31603)

控制与采样模块中,使用STM32F4作为主处理器,同时使用ESP32作为Wi-Fi和BLE的接口,这是考虑到2017年曾经出现过物联网的题目。在显示方案中使用的是串口屏,因为其界面可以在PC上面用交互式的方式画好,然后MCU就可以用串口命令的方式与它交互,节约了许多开发UI的精力。

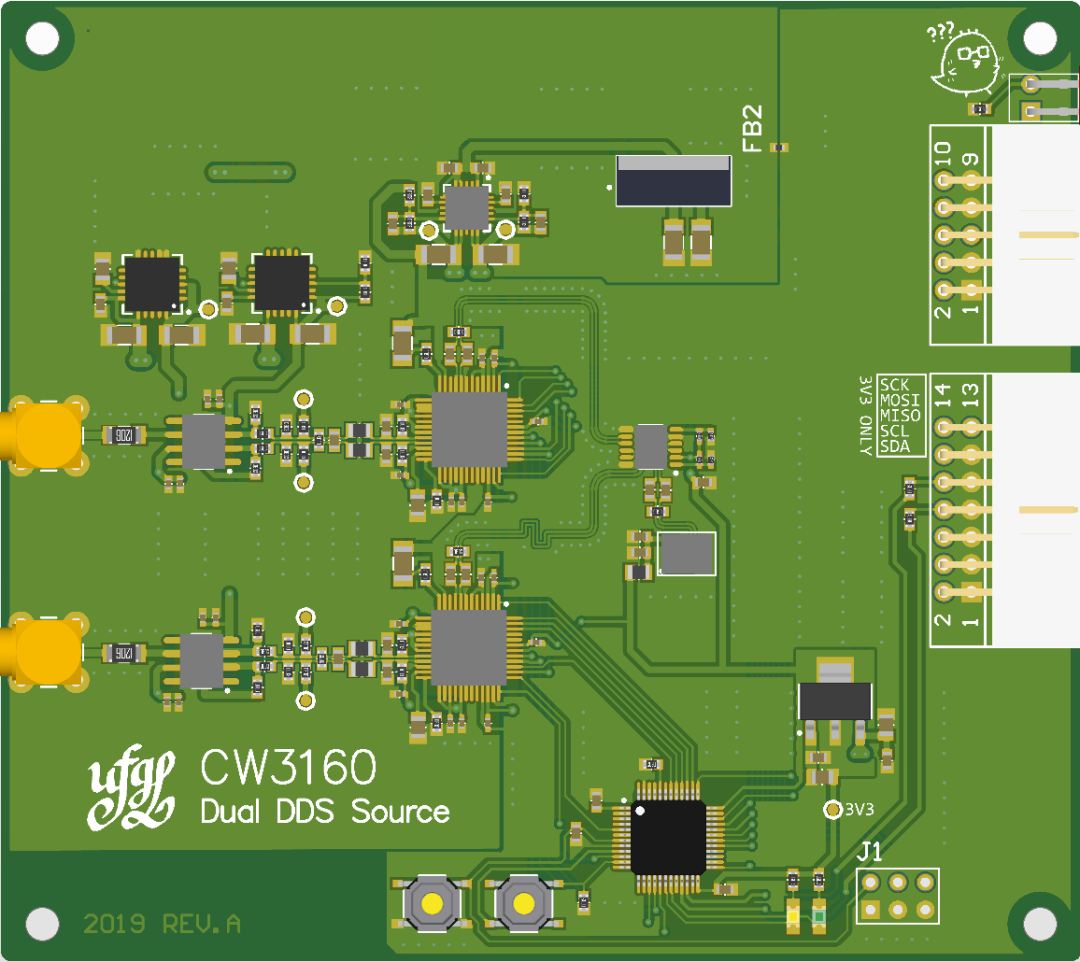

数字直接合成模块(UFGL CW3160)

数字直接合成(DDS)模块的作用就相当于信号源,我们选中了AD9954这款DDS芯片,其采样率为400MSPS,具有多片同步功能,可以输出0-160MHz的两路正交正弦信号,并具有亚赫兹级别的步进。但AD9954这款芯片特别贵又特别脆,在研发这个模块的时候就坏掉了6个,PCB重画了两套,比赛完后使用过程中又坏了一块。

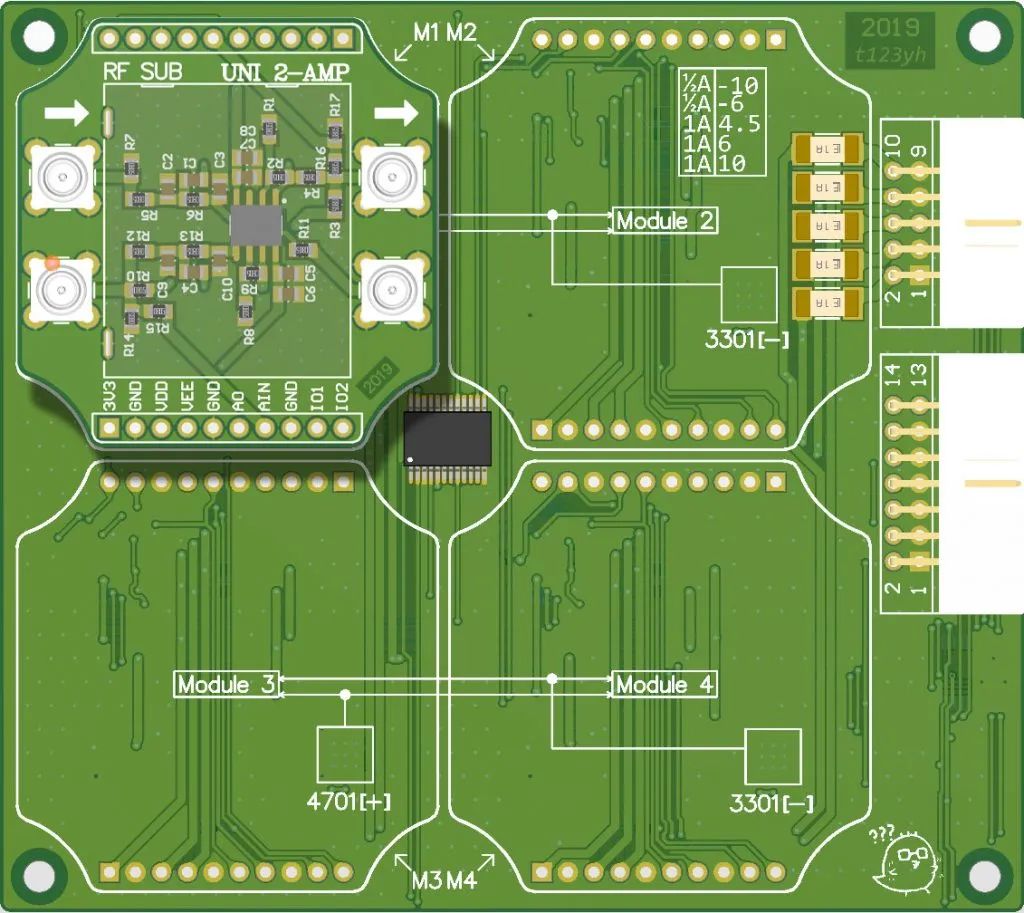

信号调理模块底板(RF底板)

信号调理模块底板,我们称作RF底板。底板为子模块提供低噪声的电源、两路逻辑IO和两路模拟IO,其中IO使用I2C进行控制。逻辑IO的设计方便了可控衰减器和继电器模块的动作,模拟IO的设计方便了检波器数据的读出和可控增益放大器的增益控制。通过预先组装调试,形成了一个固定模块,避免了许多手动的连线,提高了整体的可靠性。

我们总共设计了以下几种子模块

▫ 单/双运放通用板

▫ 比较器

▫ 乘法器

▫ 无源滤波器

▫ 继电器

▫ LNA

▫ 程控衰减器

▫ 检波器

其他没有完工的模块

在最初的设计中,每一个XSTK模块均具有一个模块化仪器的作用,能够自主调理、采集和处理信号或能够实现比较复杂的信号调理一板解决(设计了一个通用程控滤波器“Filter Pro”),模块之间使用通用的仪器总线连接。但这样也必将削弱XSTK模块的通用性,在t123yh设计了RF底板后,我们也妥协改为设计子模块。

▫ 本振模块(UFGL LO31250)(未测试),原计划为数字下变频模块

▫ 可控滤波器“Filter Pro”模块(未开始),最初设计为开关电容滤波器,后改为使用DSP算法实现

▫ FPGA模块(未测试),使用ZYNQ7010核心板配合高速14bit Dual AD/DA,这个结构参照了虚拟仪器的常见通用结构,相似项目:RedPitaya

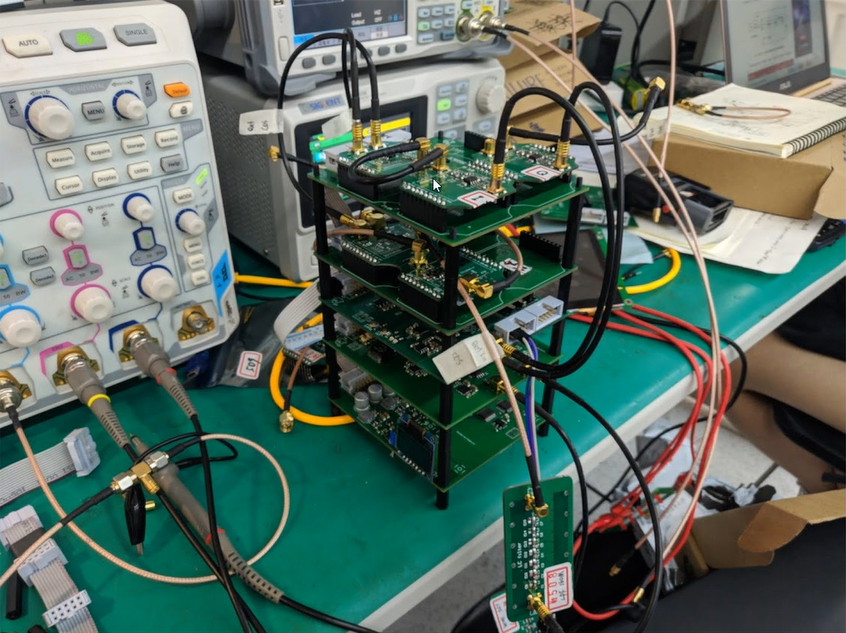

XSTK系统组成幅频特性测试仪

从上至下:RF底板(混频)、RF底板(滤波)、控制与采样、DDS、电源

总的来说基于“XSTK”的设计有这样几个特点:

▫ 使用堆叠结构大大提高作品的稳定性和美观度

▫ 统一的规范有利于方案的迭代、团队合作分工

▫ 高灵活性,XSTK的最终发展目标为模块化仪器,比赛时相当于是用仪器在做题

来自工业界的帮助

如果说实验课是通向工业界阶梯,那么电赛一定是通向工业界的电梯。

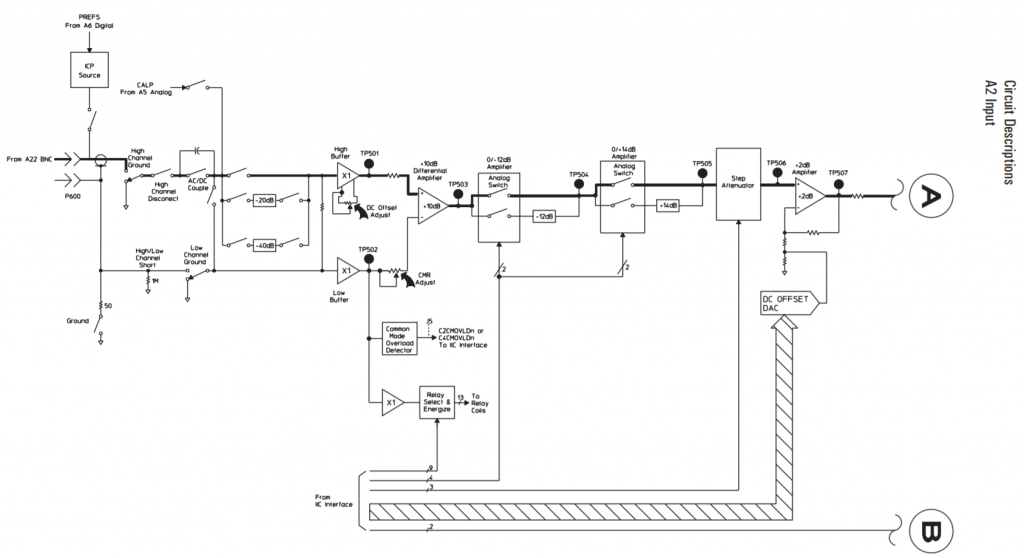

在比赛集训阶段,出于准备高频题目的需求,我联系了一位工业界的学长,这位学长主要自研频谱仪等仪器(当然后来也没有做高频,但学校的相关的仪器也莫名其妙地到位了)。第一次去拜访他,他以Agilent 35670A动态信号分析仪为例,将高精度模拟信号链的工程实现方法娓娓道来。这台仪器被研发的时候还没有16-bit的ADC集成电路,它是使用一片8-bit ADC + 8-bit DAC做成了一个类似现在的Pipeline结构的ADC。最有意思的是这台仪器有许多换挡和耦合,这些链路上的模块均能够自校准和自诊断,这是一种仪器“自治”的设计理念,是一种优美的设计。

Agilent/HP 35670A 模拟前端

仪器是人类认识世界的工具,是工程师“眼睛“,需要史无前例的通用性、客观性和可靠性,只有借助最先进的电子学技术才有可能解决一台高指标仪器研发中遇到的问题。说实话,也就是从这时开始,我慢慢感受到所谓的“仪器之美”:它有一种构建视角的能力,就像是矢量网络分析仪把来去无踪的电磁波用荧光画在史密斯图上一样,这也更加坚定了我选择仪器方向的决心。

然后我们谈到了一些具体的设计中,比如说ADC/DAC的IC的选型,使用Pin2Pin Compatible的器件是比较方便的(这些IC往往都是晶圆相同,QC分级,和CPU类似),所以理论上也是可以超频的;还有学长提醒到最好不要使用新的IC,因为IC推出初期性能可能不稳定或多次迭代的问题,你可能都不知道自己买到的什么Rev的;总的来说,一次简短的谈话让我明白了单板硬件设计非常考验信息获取能力,对于个人开发者而言,厂商给的只有一张Datasheet,这些IC的坑或香只有通过那些扎根于工业界多年的人才能了如指掌。

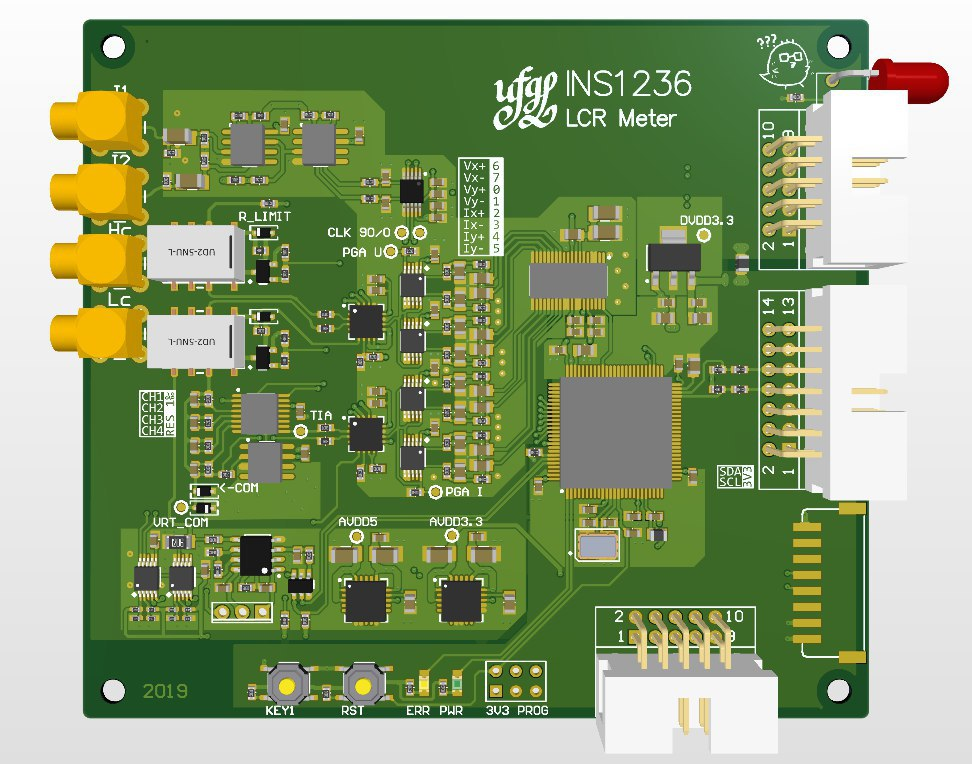

在后来的集训过程中,我们在学长的指导下开发了一块单板LCR,在IC的选型方面学长给予了非常多的帮助(都是在他的产品中检验过的IC),在LCR的结构方面,学长指出数字化RMS比幅度检波器精度高且可以使用长周期、器件的精度不必太高因为获取的是比值信息、外置比较器鉴相后期改为数字鉴相确保项目先通后期提升精度。

这些经验都是教科书上没有的,或者没有明说的。从设计要点找出理论依据是容易的,但是要从众多的理论推出设计要点却不那么容易,往往需要花费很大的精力从问题中看出来。这也就是工业界对于我们最大的帮助——宝贵的经验,在接纳这些经验的同时,我们也对这个行业有了进一步的发展,甚至不自觉已然走上了工业界的道路。

一生仅此一次

加油!!

2019.8.9 晚

走过两个月的集训,是时候检验付出的回报了。在题目发布的前一天晚上,北京下了一整夜的倾盆大雨,和队友提着鞋子从实验室光着脚在其中奔跑的感觉,让我似乎觉得走入了《肖申克的救赎》的片场,像是在雨里迎接“救赎”。最最开始准备电赛差不多过去了一年,有些场景还历历在目,成为人生漫长的马尔科夫链上的一个个节点。

比赛时间线

硬件开发主线:第一天上午选题,下午选方案,晚上熬夜画板,同时已经利用现有硬件解决了低电阻测量问题;第二天9点PCB 12小时加急下单,白天使用洞洞板搭建相同结构的原型,程序同步开发。第三天白天利用洞洞板基本实现电桥功能,发现了TIA自激的问题,晚上PCB到货焊接,通宵调试:首先调试电桥功能,然后是校准,初测精度达到4%(这里犯了很大的错误,那就是激励幅度太小,不然可以一次做到1%以内),PGA和TIA换挡算法,通过并联电容修复TIA的自激,通过5个频点的复阻抗测量,估算阻抗拓扑,这个功能是在最后加上去的,比赛时居然只识别错了一个。(甘特图 TBD)

总时间线

▫ 2018.10.12——电赛成功组队(队长:ghx,队友:fjq)

▫ 2018.11——进入电子实验室S7-701

▫ 2018.11.11——完成第一次选拔题:滤波器

▫ 2019.1.17——完成第二次选拔题:宽带放大器

▫ 2019.4.5——队伍正式命名为UnFraGiLe!

▫ 2019.4.6——完成第三轮选拔题:自适应滤波器

▫ 2019.5.25——完成第四轮选拔题:100MHz数字频率计

▫ 2019.6.30——进入电子实验室

▫ 2019.7-8——留校集训

集训期间的锁屏

▫ 2019.8.7-10——比赛

▫ 2019.8.13——封闭评测(两组排名1、3)

▫ 2019.8.14——没有资格进入综合测评

▫ 2019.8.15——收拾东西回家

▫ 2019.8.19——使用相同方案的组成功通过综合测评

▫ 2019.8.30——其参加全国电赛并获得一等奖

参赛作品的核心模块:

UFGL INS1236 单臂自平衡LCR电桥与低电阻计

可能也没有必要(也没有这么多时间)来展开谈心路历程,每个人的历程都是不可复制的,我只想说的是,这场比赛是我大学生活的转折点,它把我从一个四处游山玩水的人,约束成一个更加有事业心和动手能力的人,当然这一切在一开始的时候自然是看不出来的,但应该是所有在电赛奋斗过的人所共有的感受。专注、专注、再专注!任何情况下,如果能够用自己擅长的去解决需要解决的问题,higly recommended。

一生只有一次,对于大多数在大二暑假参加电赛的人来说一点也没错,因为电赛两年一届,而在大四的暑假就已经毕业了。尽管如此,但凡打过电赛的高手们,总会以其他的方式参与到后来若干届的电赛中来并奉献一些光和热。(就像学长一样,他曾是电赛选手)经过一次电赛,也能认识到电赛的荣誉更是一个团队和个人动手能力的“合格证”。但凡有比赛能够提供一个这样的参考基准,那也能算上是一流的比赛。

还没有加入电赛交流群的同学,可以扫描左侧二维码添加小助手微信,备注“电赛”,将你拉入微信交流群。

也可以直接扫描右侧二维码,加入硬禾电赛QQ交流群。

END

硬禾学堂

硬禾团队一直致力于给电子工程师和相关专业的同学,带来规范的核心技能课程,帮助大家在学习和工作的各个阶段,都能有效地提升自己的职业能力。

硬禾学堂

我们一起在电子领域探索前进

关注硬禾服务号,随时直达课堂

点击阅读原文查看更多