作者:锐杰微科技集团总裁 刘海川

数据时代对计算提出新需求

在过去的一年半中,全球经历了新冠疫情的肆虐。虽然已经有多种疫苗开始实施接种,但是新冠疫情在未来相当长的一段时间里对我们的生活依旧持续带来影响。我们很多人已经习惯了通过电子设备在家办公、上网课、开会甚至举办线上大型会议。2020年,全球市值最大的10家公司中前8家公司都是基于互联网和大数据开展业务,另外值得关注的是半导体制造商台积电(TSMC)位列第9位。21世纪将会是数据的世纪,数据已经成为类似石油的新型资源。大数据、图像分析、机器学习已经非常普遍,从数据中心、移动设备到物联网设备都会成为数据处理的主要节点。高性能计算机前所未有地成为我们生活中的必需品,并且极大推动了对高算力计算芯片的庞大需求。

传统集成技术下的摩尔定律已经不再有效

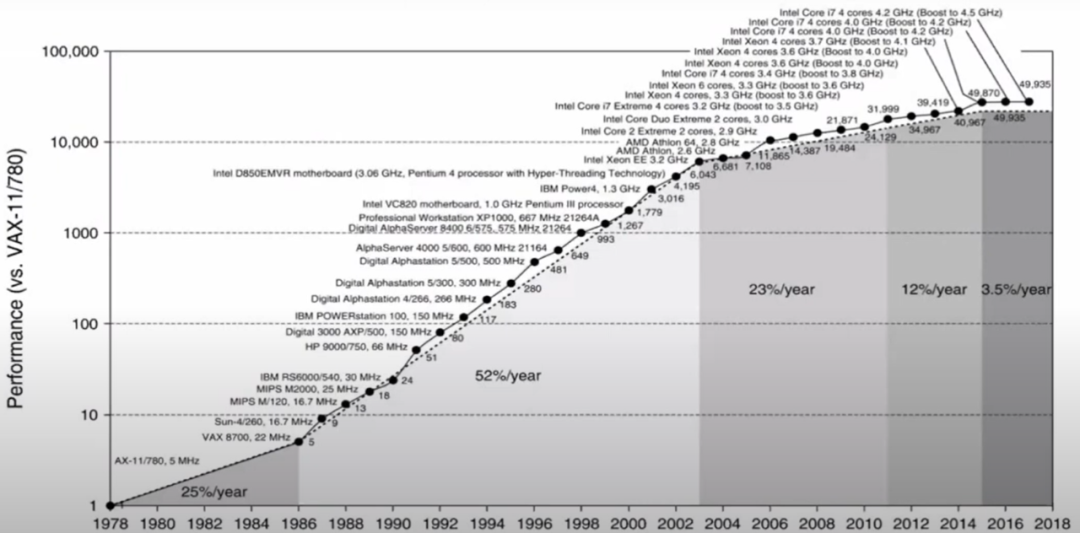

在1965年Gordon Moore提出摩尔定律到今天的近56年中,摩尔定律的效率已经逐步衰退到接近失效。Alphabet的董事长John Hennessy于2018年在美国国防高级研究计划局电子复兴计划会议(DARPA ERI)上的演讲中展示了一张图片,是过去40年来计算机性能的增长趋势。可以看到,在1978年到1986年,计算机性能的平均每年长率是25%,随后的1986年到2003年的17年中,年平均增长率增加到52%。接下来的10年,计算机性能的年平均增长率开始下降到23%,随后的几年,进一步下降到12%,直到近5年,已经下降到了3.5%。

近40年来,计算机性能增长的趋势

(图片来源:Alphabet董事长在美国国防高级研究计划局电子复兴计划2018年会议上的演讲)

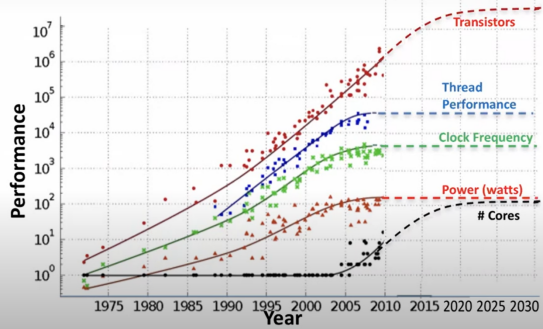

John Shalf在2019国际超级计算机会议上的演讲中展示了一张图片,在过去近50年中,计算机系统在晶体管数量、单线程性能、时钟频率、功耗以及内核数量这5个指标上的发展趋势。可以看到,在2021年,这些指标都有可能趋于饱和。今天,我们正在面临摩尔定律的终结,需要寻找一种新的路径继续提高电子产品的性能。

计算机技术发展趋势在2021年趋于饱和

(图片来源:John Shalf在2019国际超级计算机会议上的演讲)

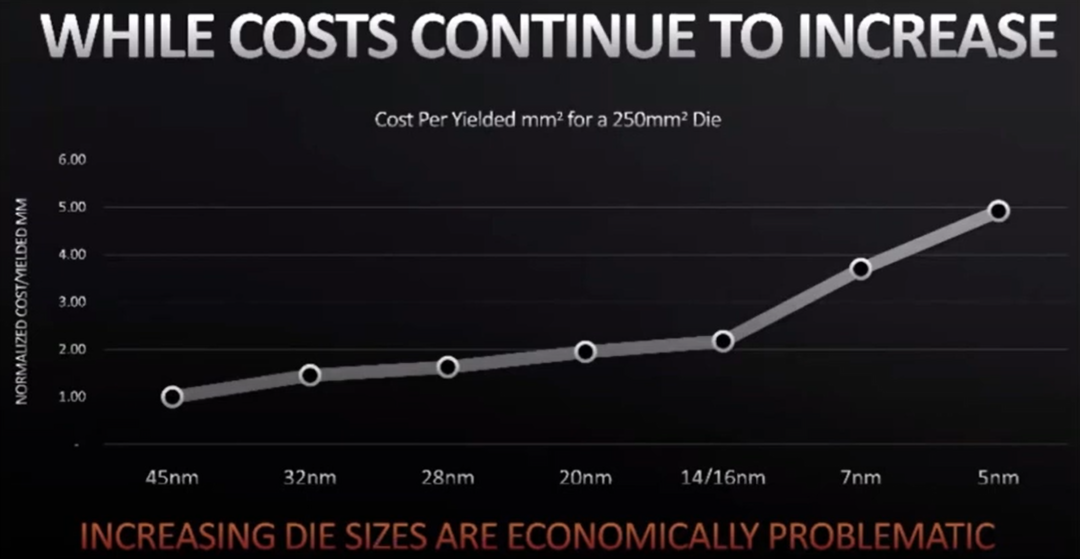

国际半导体技术蓝图(ITRS)自从1991年诞生到2016年7月发布了最后的版本,指出半导体体积到2021年将不再缩小。报告认为,半导体厂商将面积缩小、放下更多晶体管的做法在经济上已经不划算。此后,半导体厂商将更多关注3D芯片等其他技术增强计算性能。AMD的CEO Lisa Su在2019年的DARPA ERI会议上也展示了随着工艺节点从45nm逐步过渡到5nm,单位芯片面积的成本增加到了最初的5倍。

摩尔定律的经济效应遇到瓶颈

(图片来源:AMD CEO Lisa Su在美国国防高级研究计划局电子复兴计划2019年会议上的演讲)

异构集成将推动摩尔定律趋势继续有效

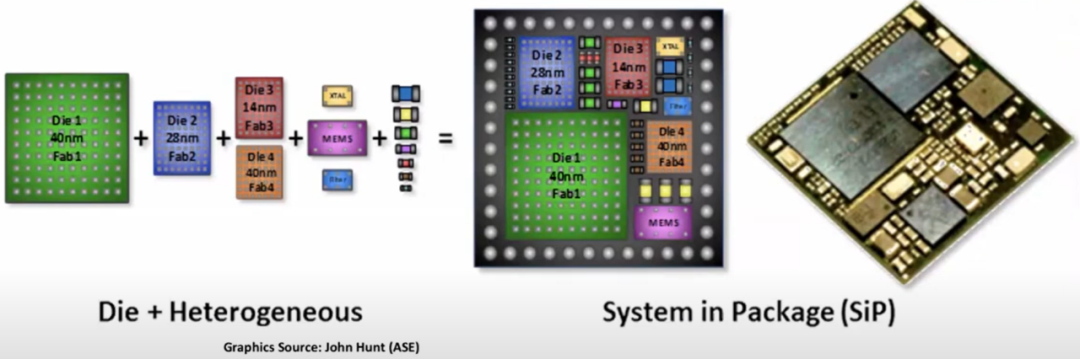

2015年,ITRS的异构集成(Heterogeneous Integration)研究团队与电气电子工程师学会(IEEE)的元器件、封装、制造技术学会(CPMT)签署了一份谅解备忘录,宣告异构集成蓝图(HIR)成立并开始完全代替ITRS。HIR 由IEEE的3个学会(电子封装学会EPS、电子器件学会EDS、光电学会PS)和半导体设备和材料国际组织(SEMI) 与美国机械工程师学会的电子与光子封装事业部 (ASME EPPD)共同组成。目的是为了维护把不同工艺制造的元器件集成在一起的先进封装技术的进步步伐,以便使当今和未来的电子系统得到更增强的功能和操作体验。

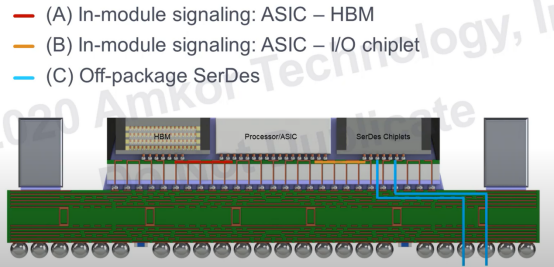

图片来源:John Hunt (ASE)

图片来源:Amkor

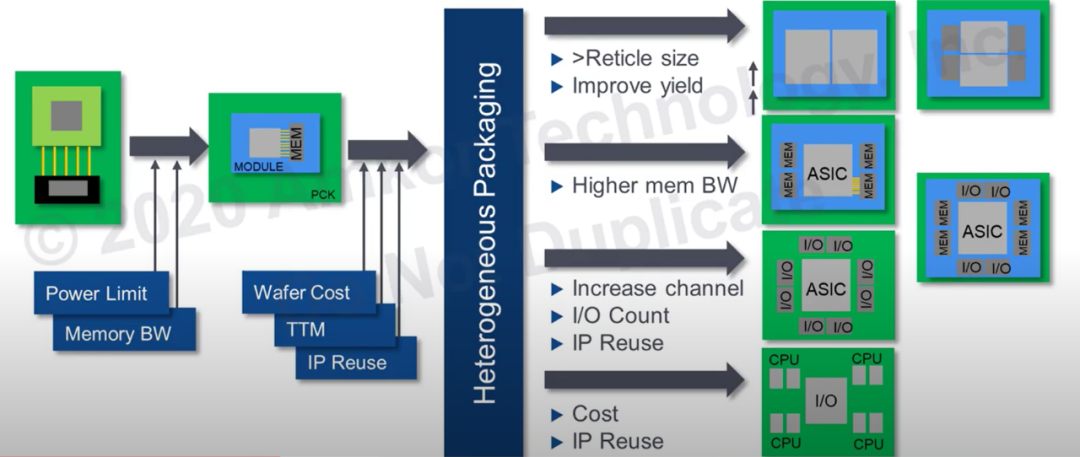

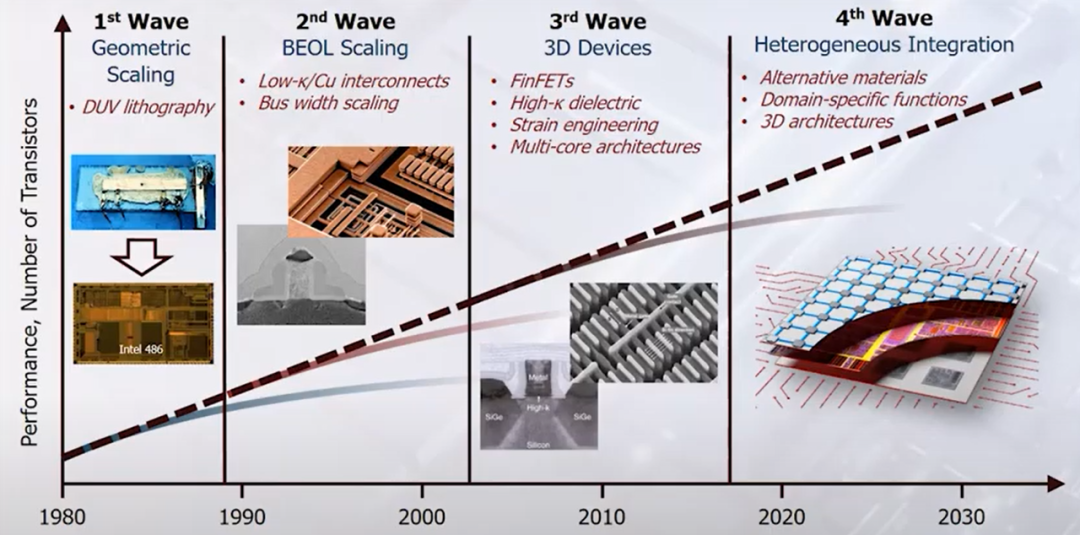

异构集成通过工艺技术的多样性、功能多样性和材料的多样性进行系统级的集成或3D封装,将进一步推动半导体工业第四波技术浪潮以便维持摩尔定律趋势继续有效。技术多样性需要将不同工艺节点的芯片集成在一起,不同于传统SoC技术手段去统一追求更先进的工艺节点,对于某些性能优异的工作稳定的IP或称为小芯片(Chiplet)可以更长时间停留在较早的工艺节点上。对于功能多样性体现在把数字、模拟、模数混合、光电子、微机械等等不同类别的芯片做集成,这在传统SoC技术路径上是很难做到的。材料多样性是异构集成最重要的特性,不局限于传统CMOS工艺,采用多种工艺结合的方式,比如采用光学系统的I/O。

异构集成是延长摩尔定律的第4波浪潮

(图片来源:ERI summit 2020)

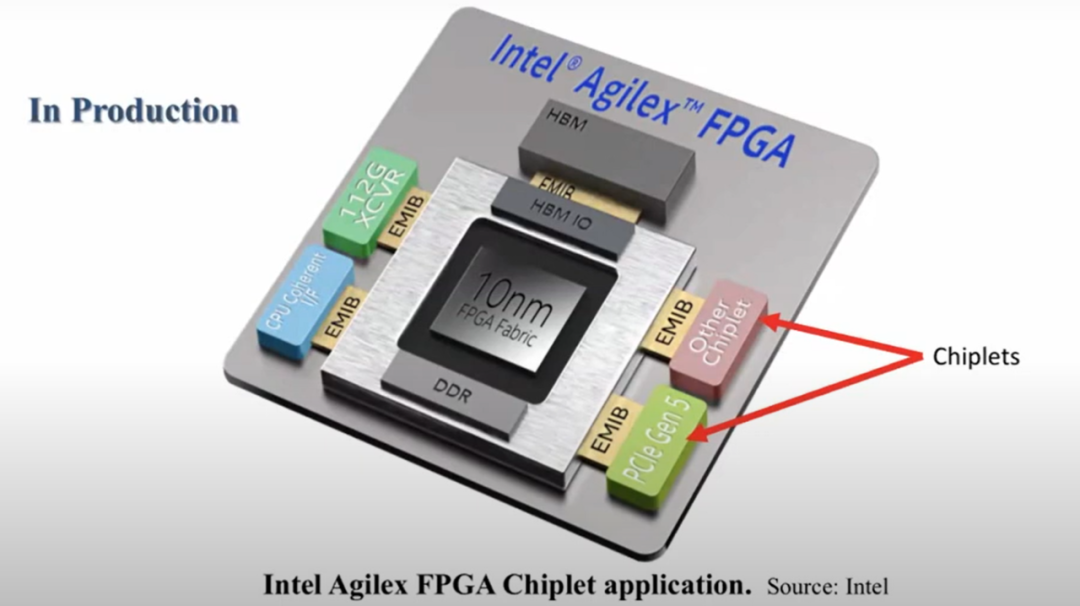

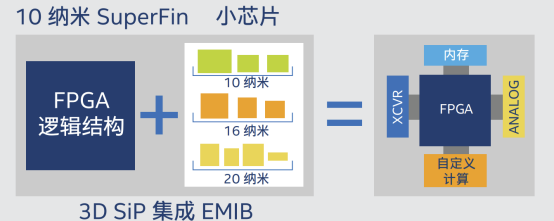

Intel的 Agilex系列FPGA是非常典型的异构集成成功案例,它既包含了传统FPGA灵活的可编程性,又结合了现代FPGA基于异构架构的敏捷性。通过Intel定义的EMIB总线将不同工艺节点的小芯片连接起来。

(图片来源:Intel)

(图片来源:Intel)

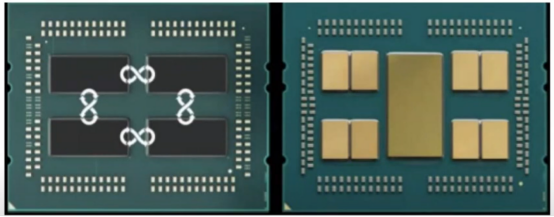

AMD的EPYC处理器是另一个异构集成的案例。在第一代EPYC中,处理器由4个14nm工艺的小芯片组合而成。而到第二代EPYC时,处理器由4组共八个7nm小芯片和一个14nm的I/O芯片组合而成。

图片来源:AMD Lisa Su DARPA ERI 2019

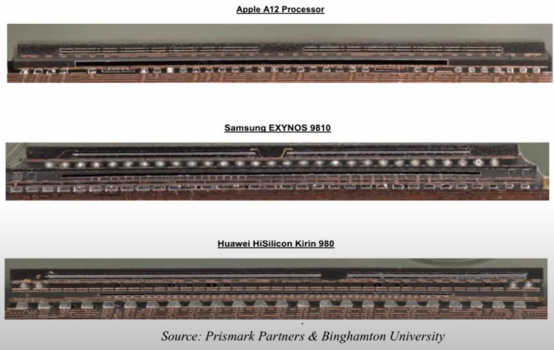

以下是几款主流手机处理器芯片的切面图,可以看到,Apple A12采用了WLP Fan-out工艺封装集成,而三星 EXYNOS9810和华为Kirin980都是采用了先进PoP工艺封装集成。

图片来源:宾汉姆顿大学

异构集成不仅仅是封装加工

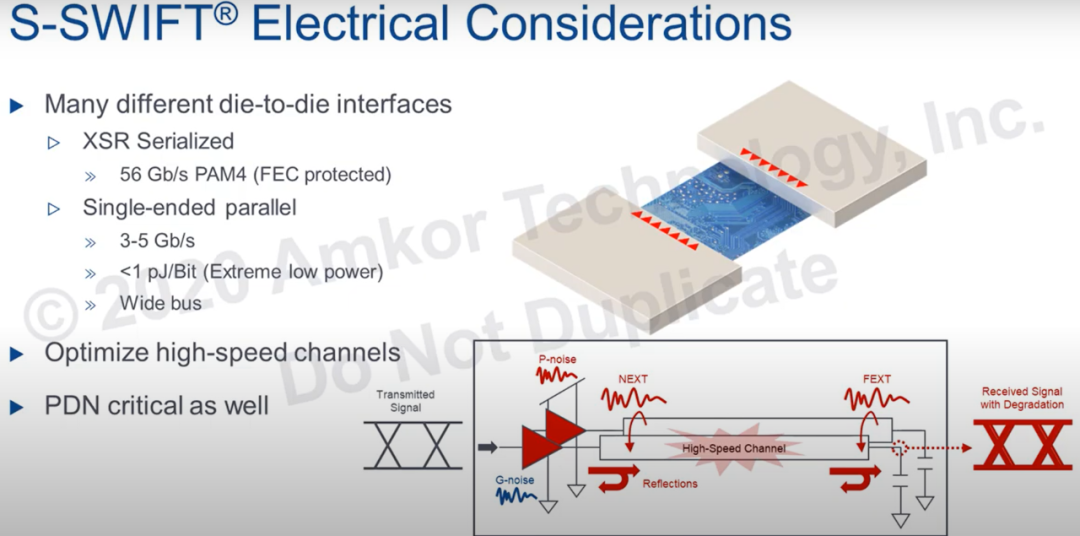

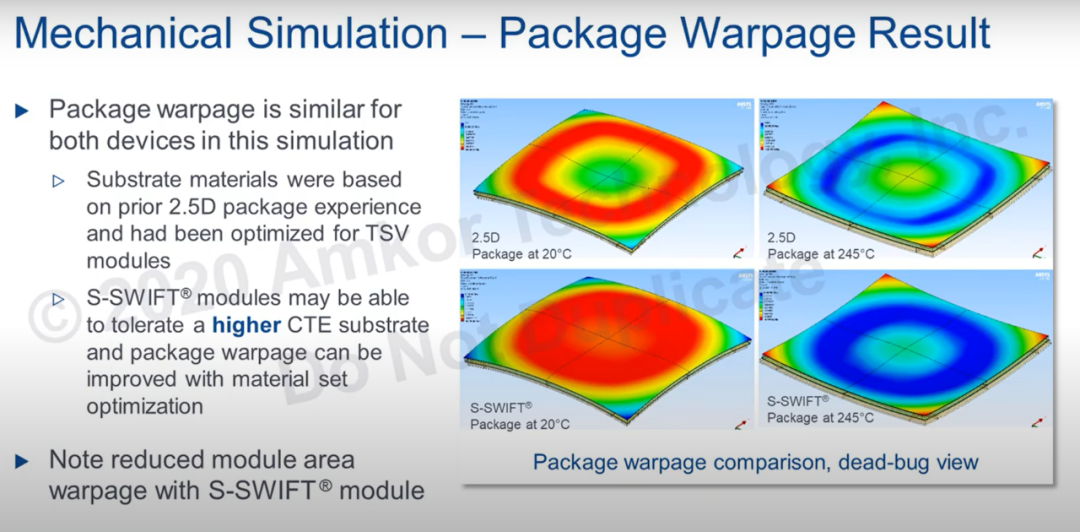

异构集成对传统的封装测试厂商(OSAT)提出了更高要求,无论是从系统设计还是EMI/PI/SI协同优化仿真,热性能优化和结构优化仿真都与传统封装厂的工艺技术有较大区别。未来,承担异构集成设计的厂商绝不能仅仅是一家封装代工厂,而是需要能够提供完整的先进封装设计与制造解决方案的厂商。在众多厂商中,ASE、Amkor具备了优秀和完整的整体解决方案。国内厂商中,通富AMD和长电收购的星科金朋也有比较强的整体方案能力。

图片来源:Amkor

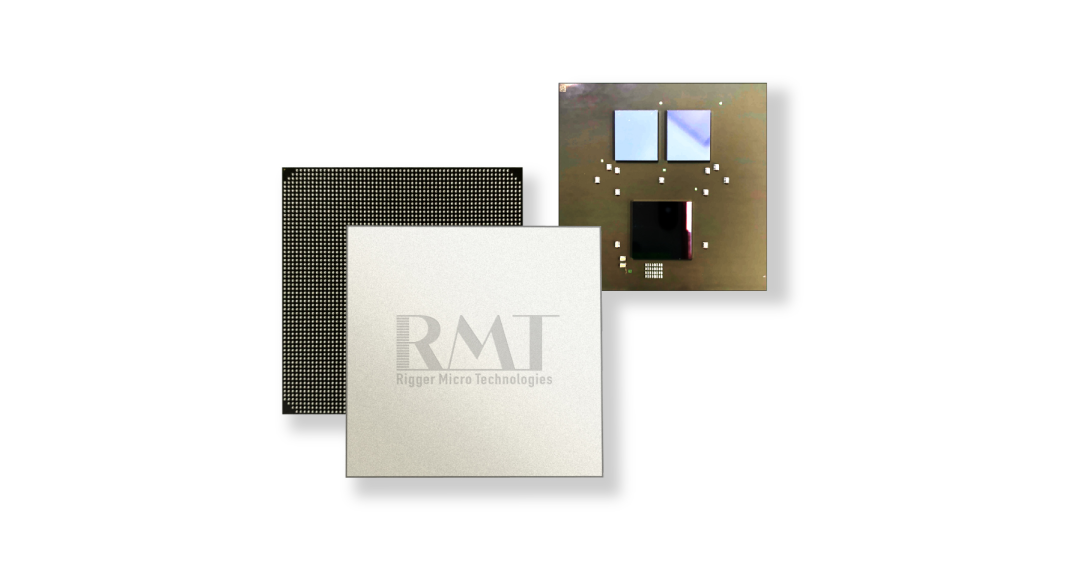

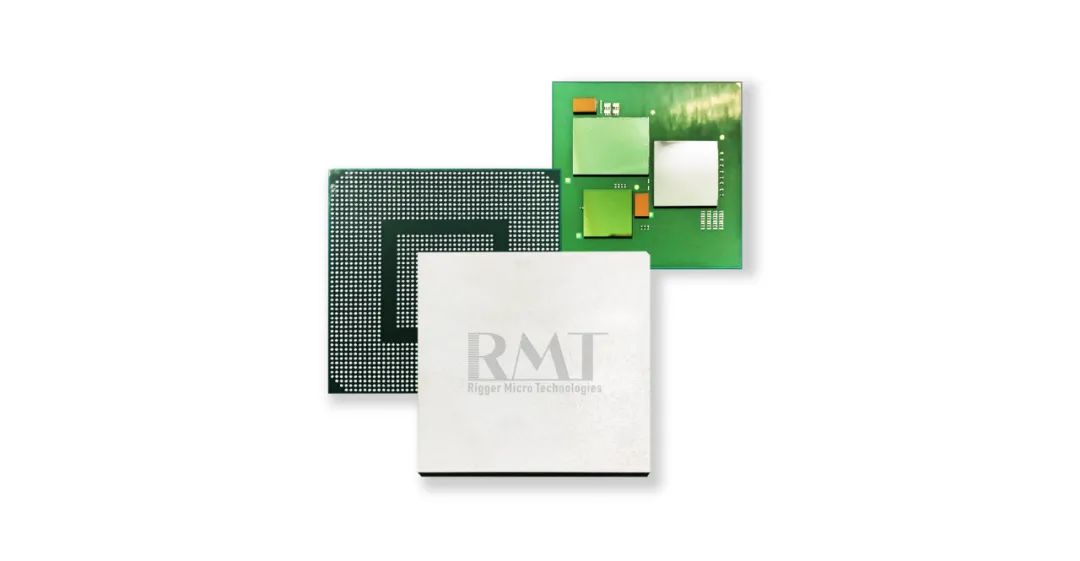

锐杰微科技在异构集成方面拥有多年积累

锐杰微在芯片封装设计,电性能仿真、分析、优化,热性能分析优化,机械应力分析优化方面经过大量的高端系统化芯片产品的项目经验,构建了一套独特的方案设计、仿真、优化思路,帮助国内百余家中高端科研、商业客户完成大量业内首创产品,涵盖国产CPU、GPU、FPGA、DSP以及ADC、手机处理器、AI、车载控制芯片领域,下面是锐杰微的经典案例中比较突出产品:

CPU+FPGA SiP(网络处理芯片)

多芯片球阵列网络处理器芯片,包含 DDR3(1600Mbps),PCIE2.0(5Gbps)、XAUI(6.25Gbps)等高速信号,该项在有限的空间内部封装有大量的高速信号互联,并且实现互抗干扰达标。61mm x 61mm的大尺寸封装同时也对设计和加工带来极大挑战

封装形式:HFCBGA(Flip Chip Ball Grid Array with Heat Spread)

封装尺寸:61mm x 61mm

Ball数量:3576

基板:10 层有机基板

CPU+FPGA+Flash SiP

该产品同样属于大尺寸封装,50mm x 50mm,高速率、多信号,含 PCIE x 16 3.0,DDR3 x 72,USB 2.0 等高速接口,内部集成多芯片,并且结合 Solder Ball 和 Copper Pillar 两种倒装工艺形式,基板的设计和表面处理工艺满足两种 Bump 加工工艺的设计与加工参数

封装形式:HFCBGA(Flip Chip Ball Grid Array with Heat Spread)

封装尺寸:50mm x 50mm

Ball数量:2089

基板:10 层有机基板

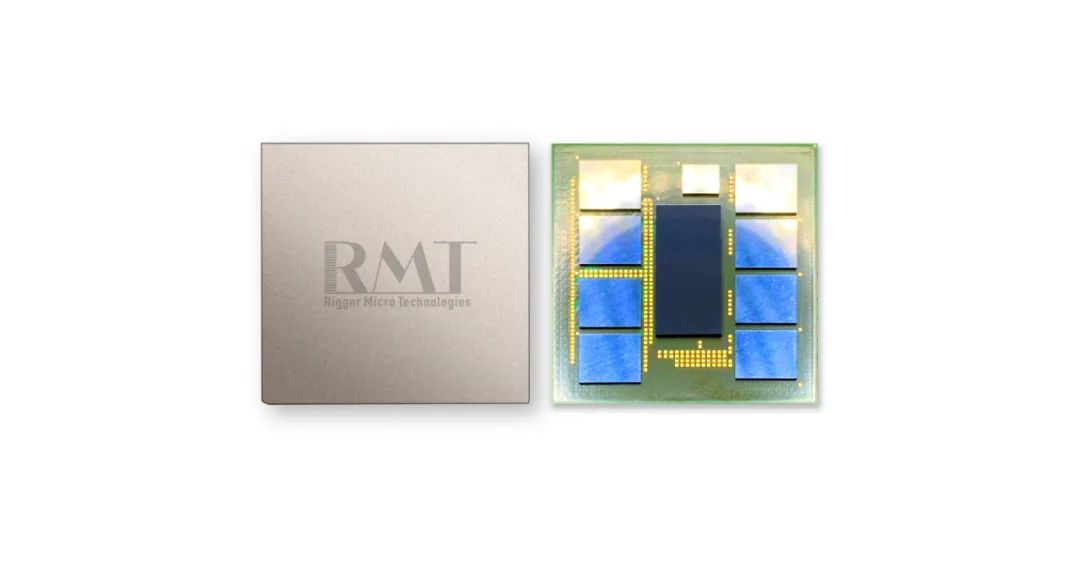

DSP SiP(处理芯片)

大规模的 HFCBGA 封装芯片,集高性能、高密度一体化数字处理模块,高速串并行信号(PCIE 3.0;Serdes 10.125 Gbps;TDP 60W;内部集成 8 颗 4Gb DDR3 4 x 72bit 1600Mbps )和一颗 Flash 外回一颗 DSP 芯片。DDR 芯片原始设计为 WB 工艺,锐杰微对该芯片进行了 RDL 二次设计,使 DDR 芯片改为倒装工艺,在基板的设计过程中对 DDR 拓朴的排布,封装一次加工就达到了项目要求。9 颗大功耗的芯片集成在一个封装内,特别是主芯片电流达到 30A,在如此小的封装内部很好的满足了大电流低电压的电源完整性和散热问题

封装形式:HFCBGA(Flip Chip Ball Grid Array with Heat Spread)

封装尺寸:35mm x 35mm

Ball数量:1024

基板:10 层有机基板

锐杰微同时在先进封装领域也积累了2.5D高密度和复杂TSV 的设计及应用项目经验,具备完整的设计、仿真、产品评估能力,下面是一款从设计到仿真(信号完整性、电源完整性、结构应力)、加工工艺、组装工艺、表面处理工艺到产品的陶封TSV正反双腔体、FC和WB混合工艺的SiP封装产品:

CPGA(陶封)SiP

陶瓷正反双腔体、TSV 2.5D 封装结构、21 颗裸芯,正面 WB,反面 FC 混合工艺,包含 DDR3 、FPGA 、DSP 、AD 、Flash 及部分高速差分和模拟信号,大型陶瓷封装,应用在高可靠性领域,封装采用了先进的 2.5D 工艺,封装内部集成了红外光感芯片,DSP \ FPGA \ 5片DDR \ AD芯片,集成度高,功能复杂。DDR 难度较大,在有限的空间内及针对陶瓷基板很好的匹配有限的工艺能力同时实现大功耗,高频率的信号连接

封装形式:CPGA (Ceramic Pin Grid Array)

封装尺寸:40mm x 40mm

Ball数量:316

基板:23层陶瓷基板

锐杰微科技是一家高度重视知识产权的科技企业,建有一套完整的知识产权管理体系,不断激励创新。在公司发展的过程中,不断地获得政府和产业的高度认可。

在美国对华科技打压的大背景下,异构集成是实现弯道追赶的最佳路径

1947年,美国贝尔实验室发明了世界上第一个晶体管。直到1956年,中国才成功制成第一根硅单晶棒。1958年,当时在TI工作的Jack Kilby做出的世界上首个集成电路。1968年,国防科工委决定在永川建立一个专业从事集成电路及相关技术研究的综合性研究所——“中国人民解放军一四二四研究所”,这也是我国第一个集成电路专业研究所。1972年6月成功研制出了我国第一块PMOS型大规模集成电路——120位静态移位寄存器(集成了1084个元件/片)。中国的集成电路行业,从起步就已经落后美国十几年。这个行业一直是中国在追赶美国的步伐。

美国对中国在集成电路方面的打压并不是近几年才有的事情,对于最先进的工艺技术,很多年前就已经保持着对华封锁的态势,这也使得中国在工艺代差上始终落后美国至少2~3代。这种代差对于数字集成电路如CPU的性能影响尤其比较大。在摩尔定律最稳定的那段时间,工艺节点决定了芯片的性能。不过随着摩尔定律的逐渐退化,近几年来,用以提升处理器性能的方式已经不仅仅是采用先进工艺制程等,同时代差的影响已经没有过去那么大了。

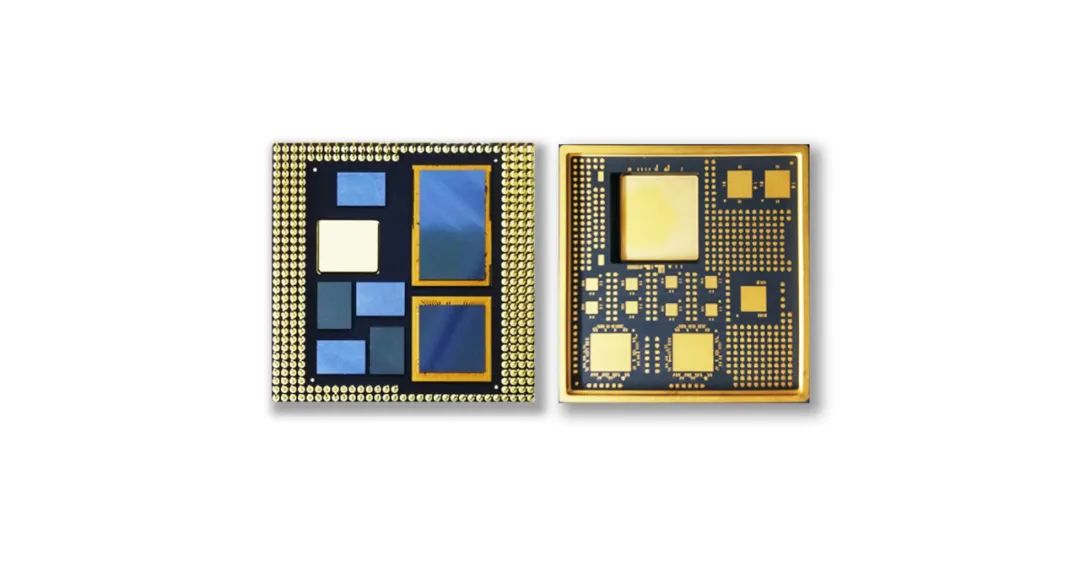

随着多核架构、高吞吐存储等方式的运用,采用10nm制程的多芯片异构集成方式处理器性能未必会逊色于采用7nm SoC单芯片方式的性能。Intel的Agilex FPGA就是个成功案例。这也给目前中国面临的巨大国产替代压力下的集成电路行业提供了一个新思路。通过已有的工艺能力加工出小芯片(chiplet),用异构集成的方式进行性能和功能的扩展集成,同样可以实现小型化、高性能的芯片方案。而且随着工艺节点的继续升级,这种改善比单纯依赖提高工艺水平的性价比高很多。

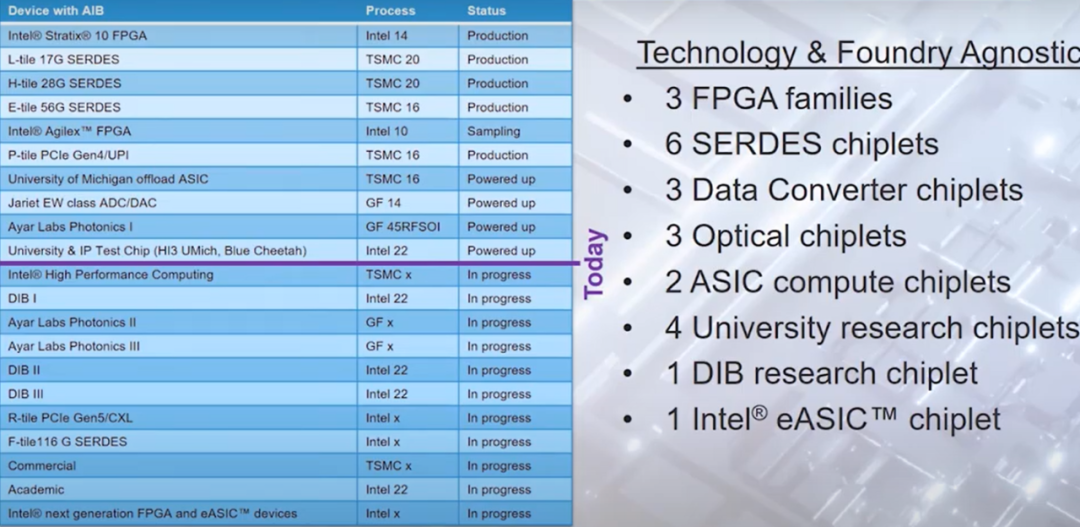

美国Intel成立了一个名为HI3(Heterogeneous Integration Incorporating Intel)的合作标准组织,发展Chiplet生态环境。目前已经有包括Intel、TSMC、GF等多个工艺节点的数十个Chiplet量产。

(图片来源:ERI summit 2020)

锐杰微科技也已在几年前就致力于发展中国自有的chiplet标准,早在2019年就加入了中国软件定义互连技术与产业创新联盟(SDI),于2020年加入了中国计算机互连技术联盟(CCITA)。在异构集成方面,中国完全不必按照美国的路径追赶。通过建立自己的芯片互联标准,完全可以在上一波摩尔定律退化失效而第4波浪潮还未起来的时候弯道赶上。在中美科技对抗的大环境下,这样做也是必要的。

作者简介

刘海川先生

刘海川先生1997年本科毕业于复旦⼤学电⼦⼯程系,⼯程硕⼠学位,复旦⼤学创新创业学院导师、复旦校友创新创业俱乐部常务理事、IC咖啡产业俱乐部发起⼈。超过20年集成电路、电⼦信息⾏业研发、市场运营管理经验, 先后服务于⼠兰微、IDT、澜起科技、Cadence等半导体公司。2010、2013和2018年先后创⽴博聪信息,磐纹科技,矽典微电⼦三家科技企业,主持发明超过40项国内、国际专利。

近期,原锐杰微科技集团董事刘海川先生出任集团总裁职务,将更加快速地推动锐杰微科技集团在IC先进封测领域突破性发展。

高端微信群介绍 | |

创业投资群 | AI、IOT、芯片创始人、投资人、分析师、券商 |

闪存群 | 覆盖5000多位全球华人闪存、存储芯片精英 |

云计算群 | 全闪存、软件定义存储SDS、超融合等公有云和私有云讨论 |

AI芯片群 | 讨论AI芯片和GPU、FPGA、CPU异构计算 |

5G群 | 物联网、5G芯片讨论 |

第三代半导体群 | 氮化镓、碳化硅等化合物半导体讨论 |

存储芯片群 | DRAM、NAND、3D XPoint等各类存储介质和主控讨论 |

汽车电子群 | MCU、电源、传感器等汽车电子讨论 |

光电器件群 | 光通信、激光器、ToF、AR、VCSEL等光电器件讨论 |

渠道群 | 存储和芯片产品报价、行情、渠道、供应链 |

< 长按识别二维码添加好友 >

加入上述群聊

带你走进万物存储、万物智能、

万物互联信息革命新时代