unsigned char key_sCAN(void){if(key == 0) //检测到被按下{delay(5); //延时5ms,消抖if(key != 0)retrurn 0; //是抖动,返回退出while(!key1); // 确认被按下,等下释放delay(5); //延时5ms,消抖while(!key1); //确认被释放return 1; //返回按下信号}return 0; //没信号}

a. 是,则开始等待释放

b. 否,则返回0,退出

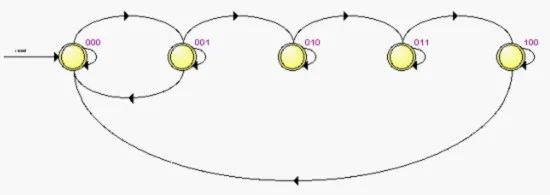

/*************************************************Module Name : key_scan_jitter.vEngineer : Crazy BingoTarget Device : EP2C8Q208C8Tool versions : Quartus II 11.0Create Date : 2011-6-26Revision : v1.0Description :**************************************************/module key_scan_jitter#(parameter KEY_WIDTH = 2)(input clk,input rst_n,input [KEY_WIDTH-1:0] key_data,output key_flag,output reg [KEY_WIDTH-1:0] key_value);reg [19:0] cnt; //delay_5ms(249999)reg [2:0] state;//-----------------------------------always @(posedge clk or negedge rst_n)beginif(!rst_n)cnt <= 20'd0;elsebegincnt <= cnt + 1'b1;== 20'd249999)cnt <= 20'd0;endend//-----------------------------------reg key_flag_r;reg [KEY_WIDTH-1:0] key_data_r;clk or negedge rst_n)beginif(!rst_n)beginkey_flag_r <= 1'b0;key_value <= {KEY_WIDTH{1'b0}};endelse if(cnt == 20'd249999) //Delay_5msbegincase(state)0:begin!= {KEY_WIDTH{1'b1}})state <= 1;elsestate <= 0;end1:begin!= {KEY_WIDTH{1'b1}})state <= 2;elsestate <= 0;end2:beginkey_flag_r <= 1'b1;key_value <= key_data; //lock the key_valuestate <= 3;end3:beginkey_flag_r <= 1'b0; //read the key_value== {KEY_WIDTH{1'b1}})state <= 4;elsestate <= 3;end4:begin== {KEY_WIDTH{1'b1}})state <= 0;elsestate <= 4;endendcaseendend//---------------------------------------the falling endge of the key_flagreg key_flag_r0,key_flag_r1;clk or negedge rst_n)beginif(!rst_n)beginkey_flag_r0 <= 0;key_flag_r1 <= 0;endelsebeginkey_flag_r0 <= key_flag_r;key_flag_r1 <= key_flag_r0;endendassign key_flag = key_flag_r1 & ~key_flag_r0;endmodule

二是,循环n次计数消抖动。同样,此模块也是Bingo无数次修改测试最后成型的代码,利用了更少的资源,更适用于并行高速FPGA的性能要求。具体代码实现过程请有需要的自行分析,本模块通过相关时钟的适配,n次计数来确认按键信号,Verilog代码如下所示:

/************************************************** Module Name : key_scan.v* Engineer : Crazy Bingo* Target Device : EP2C8Q208C8* Tool versions : Quartus II 11.0* Create Date : 2011-6-25* Revision : v1.0* Description :**************************************************/module key_scan#(parameter KEY_WIDTH = 2)(input clk, //50MHzinput rst_n,input [KEY_WIDTH-1:0] key_data,output key_flag,output reg [KEY_WIDTH-1:0] key_value);//---------------------------------//escape the jittersreg [19:0] key_cnt; //scan counterreg [KEY_WIDTH-1:0] key_data_r;always @(posedge clk or negedge rst_n)beginif(!rst_n)beginkey_data_r <= {KEY_WIDTH{1'b1}};key_cnt <= 0;endelsebeginkey_data_r <= key_data; //lock the key valueif((key_data == key_data_r) && (key_data != {KEY_WIDTH{1'b1}})) //20ms escape jitterbeginif(key_cnt < 20'hfffff)key_cnt <= key_cnt + 1'b1;endelse key_cnt <= 0;endendwire cnt_flag = (key_cnt == 20'hffffe) ? 1'b1 : 1'b0;//!!//-----------------------------------//sure the key is pressedreg key_flag_r;always@(posedge clk or negedge rst_n)beginif(!rst_n)beginkey_flag_r <= 0;key_value <= 0;endelse if(cnt_flag)beginkey_flag_r <= 1;key_value <= key_data; //locked the dataendelse //let go your handkey_flag_r <= 0; //lock the key_valueend//---------------------------------------//Capture the rising endge of the key_flagreg key_flag_r0,key_flag_r1;always@(posedge clk or negedge rst_n)beginif(!rst_n)beginkey_flag_r0 <= 0;key_flag_r1 <= 0;endelsebeginkey_flag_r0 <= key_flag_r;key_flag_r1 <= key_flag_r0;endendassign key_flag = ~key_flag_r1 & key_flag_r0;endmodule