作者:付汉杰,hankf@xilinx.com,文章转载自:赛灵思中文社区论坛

Xilinx提供超低延时编解码方案,在ZCU106单板上可以验证。文档MPSoC VCU TRD 2020.2 Low Latency XV20 提供了详细命令。

缺省情况下,编码使用的是PS DDR。如果PS DDR已经被其它应用占用,也可以让编码使用的PL DDR。在VCU TRD 2020.2的例子zcu106_llp2_xv20基础上,做如下更改,可以实现使用PL DDR编码。

和编码访问的DDR相关的硬件连接有下列AXI Master端口。

1. HDMI_in axi_m port 0

2. HDMI_in axi_m port 1

3. HDMI_in axi_m port 2

4. HDMI_in axi_m port 3

5. Sync IP axi_m port 0

6. Sync IP axi_m port 1

7. vcu mcu axi_m port

8. vcu enc axi_m port 0

9. vcu enc axi_m port 1

其中vcu enc axi_m port 0和vcu enc axi_m port 1连接到了Sync IP;vcu mcu axi_m port已经连接到了PS DDR和PL DDR。

对于剩下的axi_m port,都要连接到PL DDR。

下面是经过验证的修改。实际验证表明,它支持PL DDR编码。其中,蓝色的连接,是做了修改的;红色的连接,是新增的。

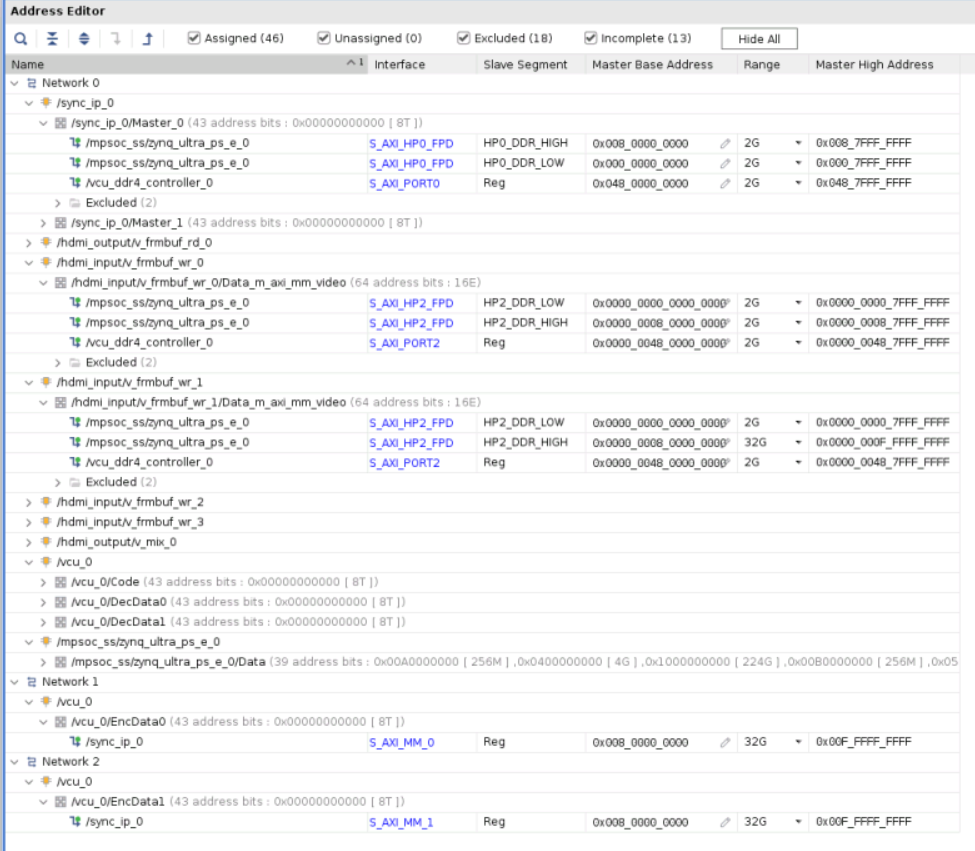

修改连接后,要检查各个AXI Master的地址分配。

在devicetree中,要保留内存,并分配给VCU编码模块、HDMI输入模块使用。

/ {

reserved-memory {

#address-cells = <0x2>;

#size-cells = <0x2>;

ranges;

plmem_multimedia: pl_dma_mem_region {

compatible = "shared-dma-pool";

no-map;

reg = <0x48 0x0 0x0 0x70000000>;

};

};

};

&encoder {

memory-region = <&plmem_multimedia>;

};

&amba_pl {

vcap_hdmi {

compatible = "xlnx,video";

dma-names = "port0";

dmas = <&hdmi_input_v_frmbuf_wr_0 0>;

memory-region = <&plmem_multimedia>;

vcap_hdmi_ports: ports {

#address-cells = <1>;

#size-cells = <0>;

vcap_hdmi_port: port@0 {

direction = "input";

reg = <0>;

vcap_hdmi_in: endpoint {

remote-endpoint = <&vpss_scaler_out>;

};

};

};

};

};

&vcap_hdmi2 {

memory-region = <&plmem_multimedia>;

};

&vcap_hdmi3 {

memory-region = <&plmem_multimedia>;

};

&vcap_hdmi4 {

memory-region = <&plmem_multimedia>;

};