地线也是有阻抗的,电流流过地线时,会产生电压,此为噪声电压,而噪声电压则是影响系统稳定的干扰源之一,不可取。所以,要降低地线噪声的前提是降低地线的阻抗。

众所周知,地线是电流返回源的通路。随着大规模集成电路和高频电路的广泛应用,低阻抗的地线设计在电路中显得尤为重要。这里就简单列举几种常用的接地方法:

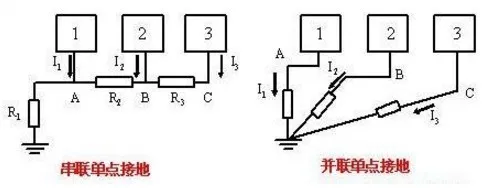

单点接地,顾名思义,就是把电路中所有回路都接到一个单一的,相同的参考电位点上。如下图所示。

单点接地可以分为“串联接地”和“并联接地”两种方式。串联单点接地的方式简单,但是存在共同地线的原因,导致存在公共地线阻抗,如果此时串联在一起的是功率相差很大的电路,那么互相干扰就非常严重。并联单点接地的方式可以避免公共地线耦合的因素,但是每部分电路都需要引地线到接地点上,需要的地线就过多,不实用。

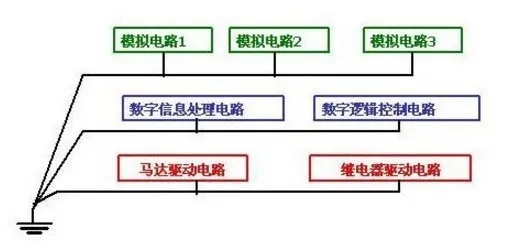

所以,在实际应用时,可以采用串联和并联混合的单点接地方式。在画PCB板时,把互相不易干扰的电路放一层,把互相容易发生干扰的电路放不同层,再把不同层的地并联接地。如下图所示。

单点接地在高频电路里面,因为地线长,地线的阻抗是永远避免不了的因素,所以并不适用,那怎么办呢?下面再介绍“多点接地”。

当电路工作频率较高时,想象一下高频信号在沿着地线传播时,所到之处影响周边电路会有多么严重,因此所有电路就要就近接到地上,地线要求最短,多点接地就产生了。

多点接地,其目的是为了降低地线的阻抗,在高频(f 一定的条件下)电路中,要降低阻抗,主要从两个方面去考虑,一是减小地线电阻,二是减小地线感抗。

1,减小地线导体电阻,从电阻与横截面的关系公式中我们知道,要增加地线导通的横截面积。但是在高频环境中,存在一种高频电流的趋肤效应(也叫集肤效应),高频电流会在导体表面通过,所以单纯增大地线导体的横截面积往往作用不大。可以考虑在导体表面镀银,因为银的导电性较其他导电物质优秀,故而会降低导体电阻。

2,减小地线的感抗,最好的方法就是增大地线的面积。在实际应用时,地线短,地面积大,抗干扰的效果就会更好。写到这里时,可能有人会问,如何才算是高频电路?参考杨继深教授的书籍《电磁兼容EMC技术》有提到“通常1MHZ以下算低频电路,可以采用单点接地,10MHZ以上算高频电路,可以采用多点接地的方式”,1MHZ和10MHZ时,如果最长地线不超过波长的1/20,可以单点接地,否则多点接地。

假如电路中既有高频信号,又有低频信号,怎么办?混合接地会是个好选择!

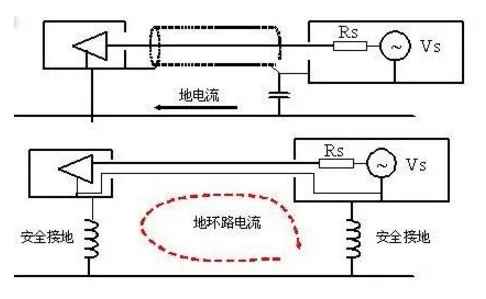

如图所示:

通过图来分析。

上图中的第一种结构,假定工作在低频电路中,根据容抗Zc = 1/2πfc可知,容抗在低频环境下很大,而高频环境下很小。那么地线在低频时是断开的,在受到高频干扰时接近导通。如此接法可以有效避开地线环路的干扰影响。

上图中的第二种结构,假定工作在高频电路中,根据感抗Zl = 2πfl可知,感抗在低频环境下很小,而高频环境下很大。那么地线在低频时是类似导通的,在受到高频干扰时是断开。如此接法可以有效避开地环路电流的影响。

综述,在实际应用中,电路根据工作环境采用合适的接地方式可以有效避开干扰信号,达到电路的最优效果。

免责声明:本文为网络转载文章,转载此文目的在于传播相关技术知识,版权归原作者所有,如涉及侵权,请联系小编删除(联系邮箱:service@eetrend.com )。