技术基础

由客户开发的超高

收敛度设计流程正式面世

通过统一的物理综合

来提高逻辑和物理一致性

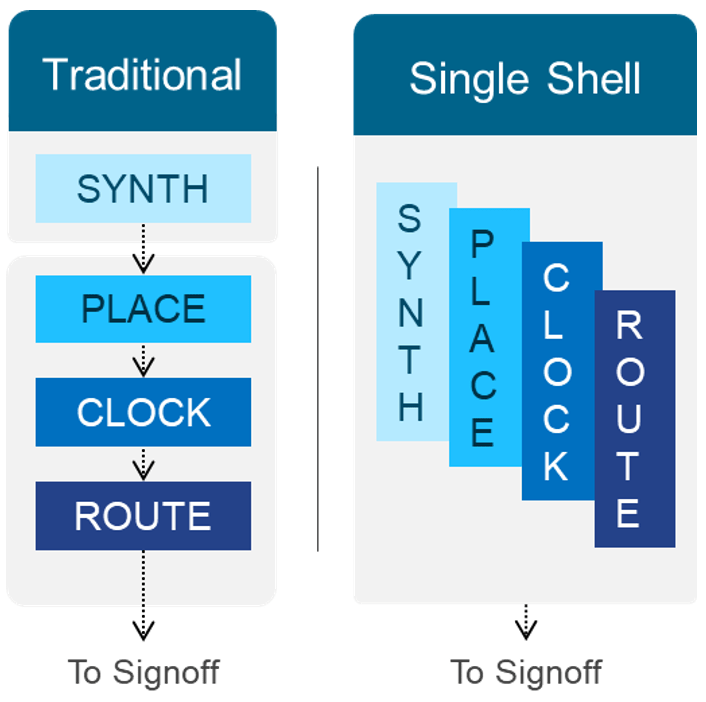

一家移动通信领域的半导体公司希望统一逻辑综合和布局流程,如自动版图设计。该公司使用Fusion Compiler统一界面创建了统一的物理综合流程,以实现以下目标:

● 更好的PPA

● 更快的运行时间

● 更好的逻辑和物理一致性

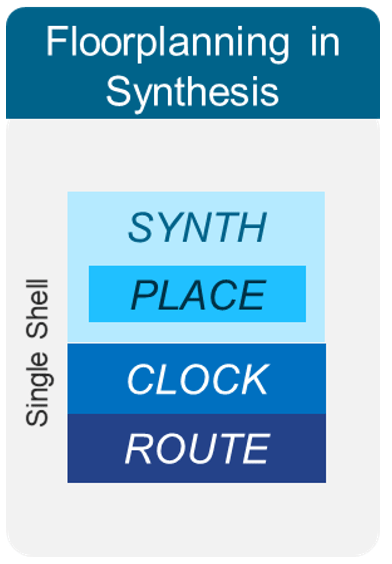

下图总结了该客户在Arm Cortex-A73上取得的设计结果,各方面指标都得到了全面的改进。

综合前进行设计规划

提高收敛能力

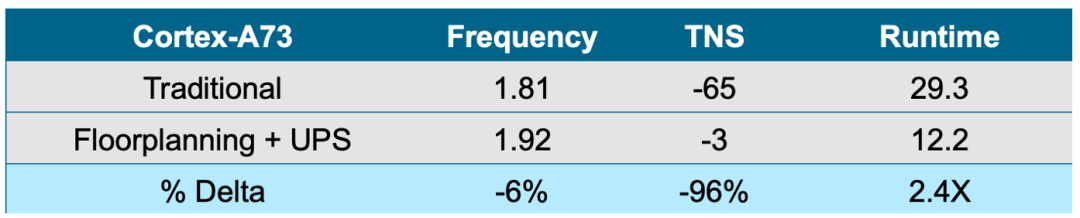

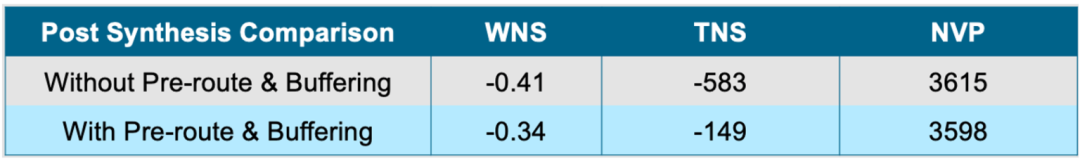

一家高性能计算公司希望在预综合阶段对通过RAM的关键信号线进行预布线和缓冲器(buffer)插入,这样做的目标是:

● 提高时序并改善关键信号线的拥塞

● 无需调用多个工具/界面

同样,该流程采用Fusion Compiler统一界面进行开发,开发结果总结如下表所示。这也是通过方法学的创新实现巨大收益的成功案例。

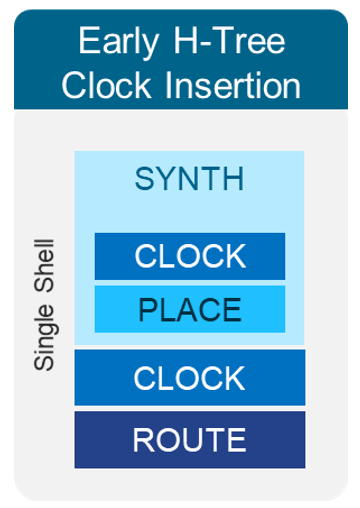

通过布局前的时钟综合

来改善时序一致性

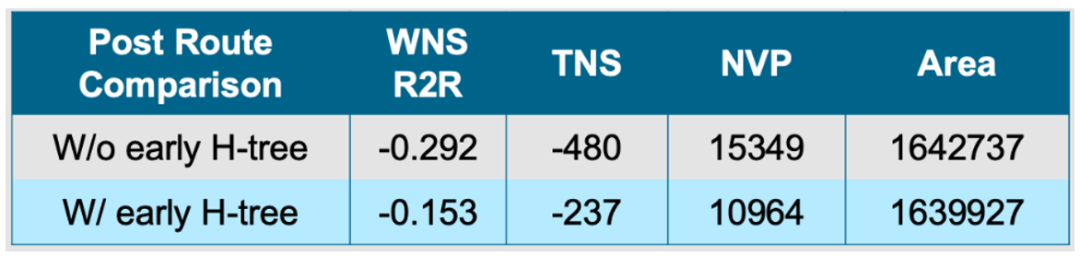

一家数据中心网络公司希望在布局之前创建早期的H树时钟主干线,以实现以下目标:

● 更好的PPA

● 改善时序收敛能力

下图总结了使用Fusion Compiler统一界面的结果。在这一案例中,总负余量 (TNS) 成功改善了50%。

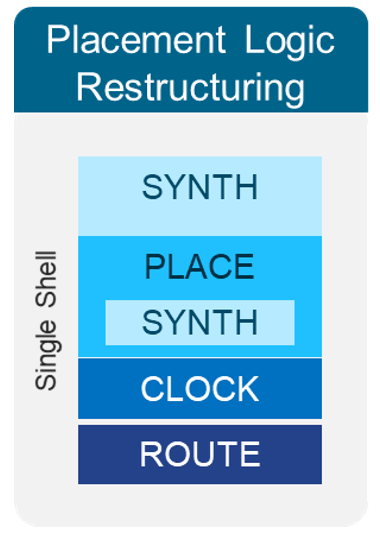

通过基于布局的

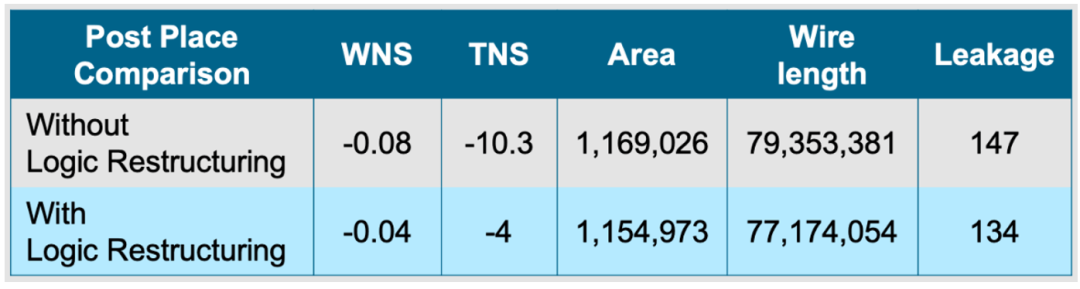

逻辑优化来提高PPA

一家数据中心网络公司希望在布局之前创建早期的H树时钟主干线,以实现以下目标:

● 提高结果质量,加快运行时间

● 提高时钟树综合的设计输入

实现结果如下表所示,该公司同样实现了全面的改进,达成了所有的目标。

未来展望

机器学习和预测可为芯片设计流程带来巨大益处。例如,Fusion Compiler采用机器预测来加快实现理想的优化解决方案,并防止DRC/时序在下游出现意外。机器学习的有效性直接取决于训练数据的质量。除了在之前的设计迭代阶段或项目中积累的大数据外,我们还有机会在流程的初期、在同一个运行过程中、或针对当前的设计版本来强化训练数据,这对于下游操作非常重要。

我们对上述客户取得的成效深感欣慰。我们已做好充足准备,协助更多客户打开自定义开发超高收敛度设计流程的新世界大门。目前,所有客户都能自由地对设计流程进行创新。

关注新思科技视频号

了解更多芯片科普小视频