行业效率标准和效率技术需求的双重作用,催生了对于构建更高效、更紧凑的电源解决方案的半导体产品的巨大需求。宽带隙(WBG)技术器件应运而生, 如 SiC MOSFET(碳化硅场效应管)能够提供更低的寄生参数,满足开关电源(SMPS)的设计要求。而650V 碳化硅场效应管器件推出之后,为1200V 碳化硅场效应器件提供补充,进一步拓宽应用范围。碳化硅 MOSFET 越来越多地被用于千瓦级功率水平的应用,包括通信电源、服务器电源、快速增长的电动汽车电池充电器市场等。

碳化硅 MOSFET 之所以有如此大的吸引力,在于它们具有比硅器件更出色的可靠性,在持续使用内部体二极管的连续导通模式(CCM)功率因数校正(PFC)设计, 例如图腾功率因数校正器的硬开关拓扑中,碳化硅 MOSFET 可以得到充分利用。此外,碳化硅 MOSFET 也可应用于更高的开关频率,从而实现体积更小、更加紧凑的电源转换器设计。

“世界上没有免费的午餐”,尽管在内部体二极管和寄生参数方面,碳化硅 MOSFET比硅 MOSFET 具有更多的优势,但在某些方面参数其性能比较差,这就要求设计人员花时间充分了解碳化硅 MOSFET 的特性和功能,并考虑如何向新拓扑架构过渡。

划重点

1.碳化硅 MOSFET 并不是简单地替换硅 MOSFET。如果这样使用碳化硅 MOSFET ,可能会导致效率下降。例如,碳化硅 CoolSiC™ 器件的体二极管正向电压(VF)是硅 CoolMOS™器件的四倍。但如果不对电路进行相应调整,谐振 LLC 转换器上在轻负载时效率可能下降多达 0.5%。

2.设计人员还应注意,如果要在 CCM 图腾 PFC 设计中获得最高的峰值效率,则必须通过打开碳化硅 MOSFET 沟道而不是只通过体二极管进行升压。

3.另一个要考虑的因素是器件结壳热阻,这方面 CoolMOS™稍有优势。由于 CoolSiC™芯片尺寸较小,在相同封装情况下,CoolSiC™热阻为 1.0K/W,而 CoolMOS™ 则为 0.8K/W,但实验证明这些热阻的差异在实际设计中可以忽略。

以下,是更进一步的技术探讨:

在工作温度范围内导通电阻

与硅器件比较

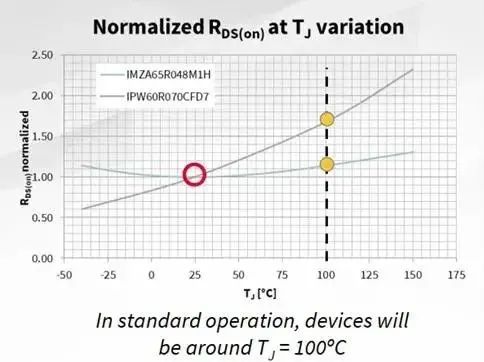

器件参数导通电阻 RDS(on)可以体现出碳化硅 MOSFET 的优势之一。在芯片温度为 100°C 时,CoolSiC™有较低的倍增系数(multiplication factor,K),约为 1.13,而 CoolMOS™则为 1.67,这意味着在芯片温度 100°C 时的工作温度下,一个 84mΩ的 CoolSiC™器件具有与 57mΩ CoolMOS™器件相同的 RDS(on)。这也表明,仅仅比较数据手册中硅 MOSFET 和碳化硅 MOSFET 的 RDS(on)并不能反映实际导通损耗的问题。

在芯片温度低范围,CoolSiC™由于其较低的斜率倍增系数和对温度的低依赖性,具有更高的击穿电压 V(BR)DSS,因此比硅器件具有更大优势,这对于那些位于室外或需要在低温环境中启动的设备非常有帮助。

图 1:在芯片温度 25°C 工作温度两种器件导通电阻基本相当, 温度对 CoolSiC™RDS(on)的影响比 CoolMOS™要小

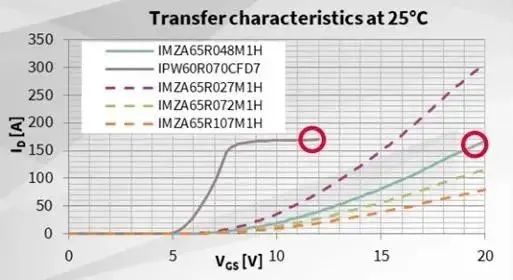

与CoolMOS™驱动设计相同,CoolSiC™ MOSFET 也可以使用 EiceDRIVER™驱动集成电路。但是应注意的是,由于传输特性的差异(ID 与 VGS),CoolSiC™器件的栅极电压(VGS)应以 18V 驱动,而不是 CoolMOS™使用的典型值 12V。这样才可提供 CoolSiC™数据表中定义的 RDS(on),如驱动 CoolSiC™电压限制为 15V 时它的导通电阻值高出 18%。如果设计 CoolSiC™电路时允许选择新的驱动集成电路器,则值得考虑具有较高欠压锁定(约 13V)的驱动集成电路,以确保 CoolSiC™ 和系统可以在任何异常工作条件下安全运行。

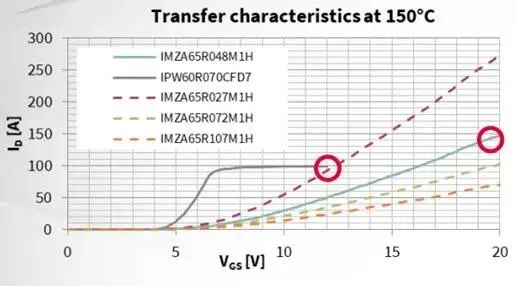

碳化硅 MOSFET 的另一个优点,是在 25°C 至 150°C 温度之间,传输特性的改变明显小于硅MOSFET。

图 2:在 25°C(上)和 150°C(下)的传输特性曲线表明,碳化硅 MOSFET 受到的影响明显小于硅 MOSFET

避免负栅极电压

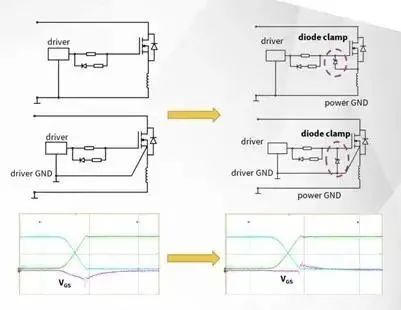

需要注意的一个问题,是要确保不允许栅极 - 源极关断电压(VGS)变得负值过大。理想情况下,不应施加负的关断电压,所以在实际设计电路时,设计工程师应在原型制作时进行检查,将电路电压振荡降低,不要让振荡电压影响栅极 - 源极关断电压变成负值。当 VGS 低于 -2V,且持续时间超过 15ns,可能出现栅极阈值电压(VGS(th))漂移,导致 RDS(on)增大,以及整个应用生命周期内系统效率降低。

负 VGS 出现的一个原因是由关断时驱动集成电路和碳化硅 MOSFET 之间电路板寄生电感制造的栅源极电压振荡,这振荡是由于碳化硅 MOSFET 关断时电路板寄生电感有高速关断电流(di/dt)通过所致。第二个常见原因是导通时由电容驱动的栅极 - 源极电压,其源于半桥配置中第二个碳化硅 MOSFET 的高 dv/dt 开关。

硅 MOSFET 设计中在此类问题一般可以通过栅极驱动器和硅 MOSFET 栅极之间插入一个高阻值电阻,或找到一种减慢 di/dt 和 dv/dt 的方式来解决。不幸的是,这些方法会导致开关损耗增加和系统效率降低。而在使用碳化硅 MOSFET 时,只需在栅极和源极之间增加一个二极管电压钳位即可解决这一难题。

在碳化硅 MOSFET 的设计中,如果该振荡问题是纯电感性,降低振荡的方法是将碳化硅 MOSFET 源极分为电源极和驱动器源极,钳位二极管连接碳化硅 MOSFET 栅极和驱动器源极之间。当然首选使用开尔文源极(Kelvin source)封装的碳化硅 MOSFET,特别在大电流应用中。例如,在 3.3kW 连续导通模式(CCM)图腾 PFC 中,关断电流可以达到 25A 至 30A。相比不使用开尔文源极封装的相同 RDS(on)的 TO-247 封装碳化硅 MOSFET ,CoolSiC™ IMZA65R048M1H 的开通损耗 EON能够降低三倍。

图 3:为避免碳化硅 MOSFET 的栅极电压变为负值,应考虑使用二极管钳位、或独立的端和开尔文源极

实现超过 99%的效率

在漏极 - 源极电压 VDS 高于 50V 时,CoolSiC™ MOSFET 输出电容 COSS 也比相对应的 CoolMOS™ MOSFET 更高,CoolSiC™ MOSFET 相对较大输出电容 COSS ,实际上可以降低关闭期间的过冲水平。对于这两种器件技术,峰值 VDS, max 设置为数据表极限的 80%。CoolMOS™需要一个高栅极电阻来满足要求,这种方法导致上面已经提到的效率降低,而 CoolSiC™设计则可以不使用这种电阻方案,从而进一步简化了设计和布局以及它们的应用场景。这种好处取决于设计人员能否实现降低电路板的寄生参数。

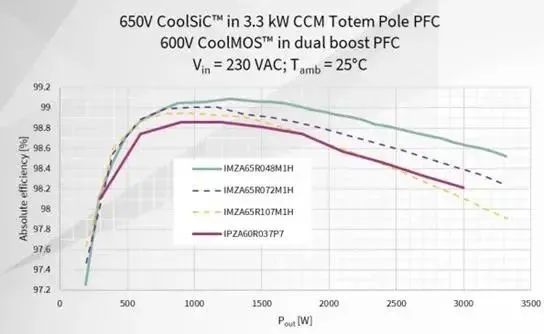

碳化硅 MOSFET 的 QOSS 特性也有利于硬开关和谐振开关拓扑架构。与硅 MOSFET 相比,碳化硅 MOSFET 的电荷 QOSS 降低了 75%,因此所需的放电时间更少,降低 CCM 图腾柱 PFC 的 Eon 损耗。虽然 CoolMOS™CFD/CFD7 系列的 Qrr 比上一代 CoolMOS™ CFD 改进了十倍,但 CoolSiC™的 Qrr 参数再比 CoolMOS™ CFD/CFD7 的 Qrr 又降低了五到十倍。这意味着,通过使用 48mΩCoolSiC™器件, 3.3kW CCM 图腾 PFC可以实现 99%以上的效率,而在 Dual Boost PFC 设计中使用 CoolMOS™的最佳效率只能达到 98.85%的峰值。

尽管碳化硅 MOSFET 的成本较高,但如果比较两种设计方法的物料清单(BOM),碳化硅 MOSFETSiC 解决方案的物料清单更少,可提供更具成本竞争力且效率高达 99%的解决方案。

图 4:即便是 107mΩ的 CoolSiC™ CCM 图腾 PFC 其效率也接近99%,多数情况下性能都可超过最佳的 CoolMOS™ Dual Boost PFC 方案

总结

多年来,尽管硅 MOSFET 的技术进步使其在寄生参数方面取得了显著改善,但硅的基本物理学特性仍然在阻碍着其性能的进一步提高,限制了创新且又简单的拓扑结构应用,也阻碍了可持续、绿色、高效率的拓扑发展。

碳化硅 MOSFET 技术在应用中同样也存在挑战,并非碳化硅 MOSFET 的所有寄生特性都优于硅 MOSFET 。但是这种技术确实能够提供多种优势,加上其在硬开关应用中的牢固性,可支持更高效的电源转换应用。650V CoolSiC™系列的推出进一步强化上述优势,使碳化硅 MOSFET 技术进一步提高功率转换效率的同时,在经济方面也更加切实可行。

关于英飞凌

英飞凌设计、开发、制造并销售各种半导体和系统解决方案。其业务重点包括汽车电子、工业电子、射频应用、移动终端和基于硬件的安全解决方案等。

英飞凌将业务成功与社会责任结合在一起,致力于让人们的生活更加便利、安全和环保。半导体虽几乎看不到,但它已经成为了我们日常生活中不可或缺的一部分。不论在电力生产、传输还是利用等方面,英飞凌芯片始终发挥着至关重要的作用。此外,它们在保护数据通信,提高道路交通安全性,降低车辆的二氧化碳排放等领域同样功不可没。

点击“阅读原文”,了解更多.