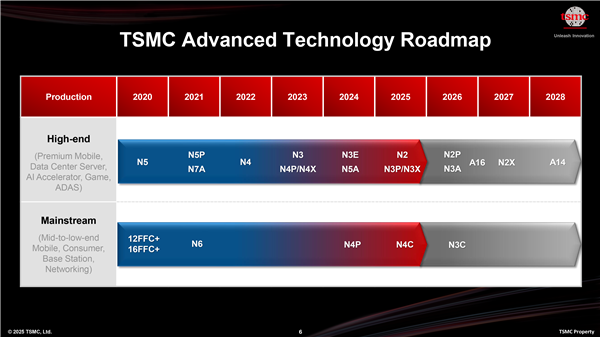

台积电在美国举办的北美技术论坛2025上,正式公布了全新的14A 1.4nm级工艺,预计2028年上半年量产,从命名到技术直接对标Intel 14A,后者同样号称1.4nm级工艺。

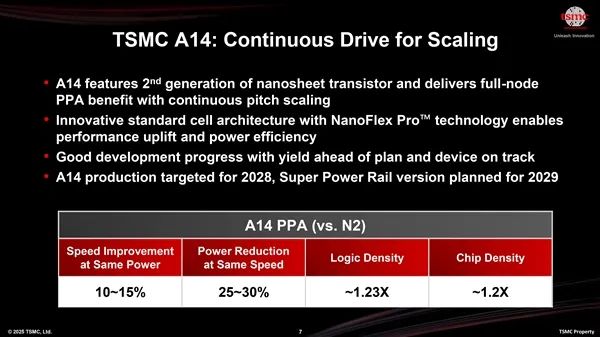

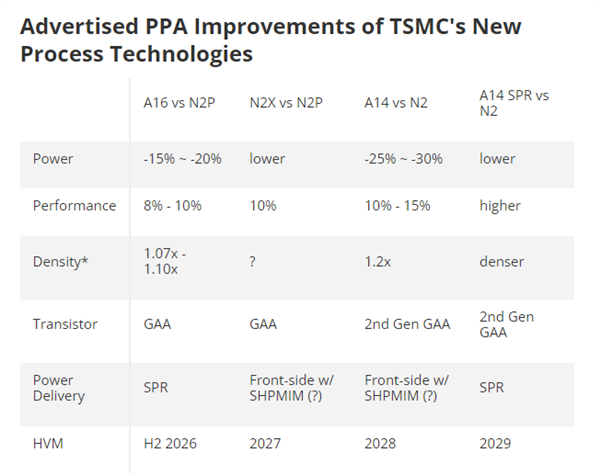

台积电称,A14是全新升级的一代工艺节点(非过渡型),对比N2 2nm级工艺,同等功耗下性能可提升10-15%,同等性能下功耗可降低25-30%,逻辑晶体管密度提升最多约23%,芯片密度提升最多约20%。

技术方面,台积电A14升级第二代GAAFET全环绕纳米片晶体管,以及新的标准单元架构NanoFlex Pro,后者可以在设计芯片的时候,针对特定的应用或负载,精细调整晶体管配置,以达成更优的性能、功耗和面积(PPA)。

台积电A14同时还有新的IP、优化、EDA设计软件,这些和N2P 2nm、A16 1.6nm是不兼容的。

遗憾的是,台积电A14首发的时候没有Super Power Rail(SPR)背部供电网络(BSPDN),这一点和自家的A16、Intel A18/A14截然不同,倒是和自己的N2、N2P一样。

不过,台积电承诺会在2029年推出A14工艺的升级版,加入背部供电,性能更好,但成本也会有所增加。

升级版A14暂时没有名字,可能会叫做A14P。

后期还有可能会演化出更高性能的A14X、更低成本的A14C。

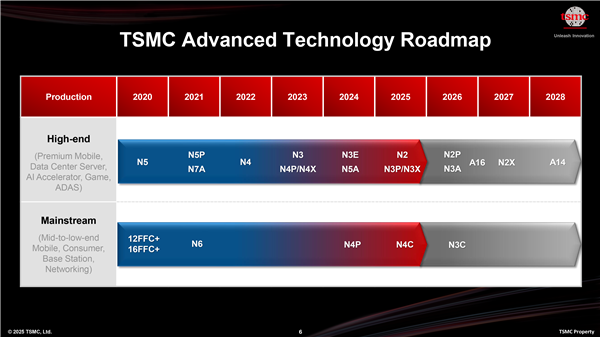

哦对了,台积电的A16、N2P工艺预计2026年下半年量产。

Intel代工在去年2月份成立的时候,宣布了自己的A14 1.4nm级工艺,业界首次采用全新的High NA EUV光刻机,预计2026年左右推出,届时又是棋逢对手。

透露个小秘密,Intel代工将在下周举办新一届大会,公布最新进展,届时我将为大家带来现场一手报道,欢迎关注。

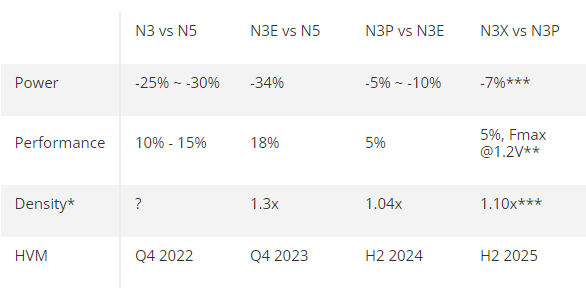

除了发展N2、A16、A14等采用GAAFET全环绕晶体管的全新工艺,台积电还在持续挖掘传统FinFET立体晶体管的极限,最后一代用它的N3系列工艺节点仍在不断演进。

台积电最新宣布,3nm级工艺的第三代N3P已经在2024年第四季度投入量产,第四代N3X则会在今年下半年投产。

N3P就是第二代N3E的升级版,面向需要高性能的客户端、数据中心应用,同时保持IP与设计兼容。

按照官方数据,N3P同等功耗下的性能可再提升约5%,而同等性能下的功耗可再降低5-10%,另外晶体管密度提升4%,尤其是SRAM缩放的提升较为明显。

苹果M3/M4、高通骁龙8至尊版、联发科天玑9400/9400+等都用的N3E工艺,不知道今年的升级换代会不会都上N3P?还是直奔N2?

N3X则是N3P的再次升级版,可继续将同等功耗性能提升5%,同等性能功耗降低7%。

更关键的是,N3X支持最高达1.2V的电压,从而将频率、性能挖掘到极致,但代价就是漏电率骤然增大最多250%,因此芯片设计要非常慎重。

根据路线图,台积电N3明年还会有N3A、N3C两个版本,但未做具体介绍,从定位看N3C是超低成本,定位很低。

PS:台积电N3其实还有个特殊版本N3B,但性能和成本都不算太好,大客户中只有Intel一家在用,就是Lunar Lake、Arrow Lake,妥妥的大冤种。

另有报道称,Intel 18A工艺制程试产顺利,并获得客户点赞。

据中国台湾ASIC企业透露,近期提前收到了去年投片于Intel 18A制程的芯片样本,目前正在进行测试阶段,初步验证结果良好。

此外,英伟达和博通也在积极进行制造测试。

Intel的晶圆代工正在快速追赶,Intel 18A比台积电A16更早引入BSPDN(背面供电)技术,CPU也将以70%的自产率为目标。

供应链消息指出,今年下半年推出的Panther Lake的重要Compute tile将采用内部Intel 18A制程,而Graphic tile及SoC tile则会由台积电进行。

明年的Nova Lake则会扩大对外委托,部分Compute tile交由台积电2纳米制造,但仍有部分型号采用内部制程。

由于台积电的A16制程预计要到明年下半年才推出,因此Intel的领先,加上价格和地缘政治因素,使其成为芯片巨头们的新选择。

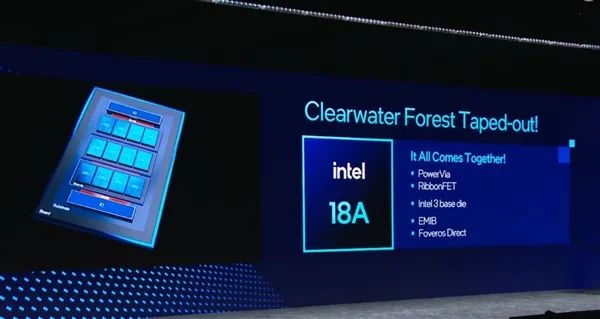

在此前举办的Intel Vision 2025大会上,Intel正式宣布其Intel 18A工艺制程技术已进入风险生产阶段。

Intel代工服务副总裁 Kevin O'Buckley在Intel即将全面完成其“四年五个节点(5N4Y)” 计划之际宣布了这一消息。

该计划最初由前CEO帕特·基辛格(Pat Gelsinger)所规划,是该公司预计从竞争对手台积电手中夺回半导体王位的一部分。

Kevin O'Buckley表示,风险试产虽然听起来很可怕,但实际上是一个产业的标准术语。 风险试产的重要性在于我们已经将技术发展到了可以量产的程度。

他还强调,Intel已经生产了大量Intel 18A测试芯片。 相较之下,风险试产包括将完整的芯片设计晶圆投少量生产,再通过调整其制造流程,并在实际生产运作中验证节点和制程设计套件(PDK)。据悉,Intel将在2025年下半年扩大Intel 18A的产量。

31日举办的Intel Vision开幕活动中,Intel新任CEO陈立武宣布,18A工艺技术仍按计划进行,接近第一批外部流片,预计今年下半年首发该工艺的Panther Lake处理器将进行大批量生产。

据悉,Intel的下一代面向移动端笔记本的Panther Lake将于2025年下半年发布(预计命名为酷睿Ultra 300系列)。

公开资料显示,Intel “四年五个节点” 计划是该公司在2021年7月提出的半导体制造战略,目的是通过四年时间(2021-2025 年)推出五个制程节点,重塑其在先进制程领域的领先地位。

2010年代后期,Intel在10nm/7nm节点遭遇多次延迟,而台积电、三星通过EUV技术快速推进3nm/2nm制程,导致Intel在移动端和服务器市场份额被蚕食。

2021年帕特・基辛格接任CEO后,提出 “集成设备制造商(IDM)2.0” 战略,强调自主制造能力与代工服务并重。“四年五个节点” 计划成为IDM 2.0的核心载体,目标是到2025年通过五个节点实现制程反超。

为更准确反映性能与能效提升,Intel放弃传统的nm命名法,改用Intel 7/4/3/20A/18A的新命名体系。20A工艺等效2nm级,18A则等效于1.8nm级。

2024年9月,Intel宣布,18A工艺进展顺利且超过预期,Arrow Lake高性能处理器原定采用的20A工艺已经取消,改为外部代工制造。

18A工艺在20A的基础上打造,将成为首款同时采用PowerVia背面供电和RibbonFET环绕式栅极(GAA)晶体管技术的芯片。

其中,PowerVia提供优化的电源布线,可提高性能和晶体管密度,而RibbonFET能够精确控制晶体管沟道中的电流,在减少功耗方面发挥着重要作用,同时还能实现芯片组件的进一步小型化。

按照Intel的愿景,18A将是其反超台积电、重夺半导体工艺世界第一的关键节点。