点击蓝字 关注我们

SUBSCRIBE to US

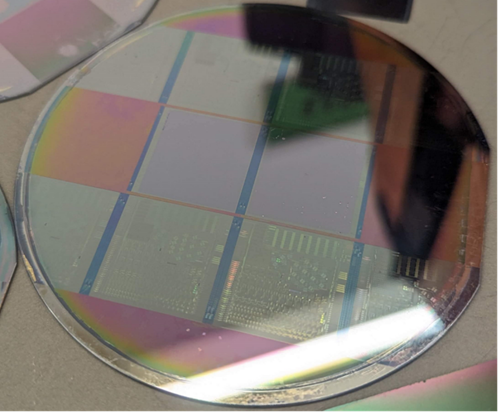

图示: 新型高性能AI加速硬件平台,在硅芯片上集成光子电路

研究人员开发出新型AI加速器硬件平台,能以更低能耗处理大量计算任务。

AI正以惊人的速度改变各行各业,随之而来的是,深度学习技术和海量数据的处理对它的算力也提出了极高的要求。如今,AI训练大多依赖图形处理器(GPU)来完成繁重的计算任务,其庞大的算力需求与巨大的能耗,已成为了AI发展的“隐形负担”。

近期发表在IEEE Journal of Selected Topics in Quantum Electronics上的研究(https://ieeexplore.ieee.org/document/10835188/),提出了一种全新的解决方案:使用光子集成电路(PIC)来打造新型AI加速平台。与传统GPU架构相比,该平台具有更高的可扩展性与能效。该研究由惠普实验室资深研究者Bassem Tossoun博士主导,展示了使用III-V族化合物半导体材料的PIC如何高效执行AI计算任务。该光子AI加速器采用光神经网络(ONN)传输和处理信息,而非电子分布式神经网络(DNN),这就意味着:运行速度更快,能耗更低,几乎没有信号损耗。

Tossoun博士表示: “制造硅光子器件并非难事,但将其应用于复杂的大规模集成电路中仍存在局限。而我们研发的平台可以作为未来光子加速器的核心组件,具备远超现有技术的扩展性与能效表现。”

研究团队采用“异质集成”工艺,把硅光子技术和III-V族半导体材料“拼”在一起,实现了激光器和光放大器的芯片内集成,以此减少光损耗并提升可扩展性。

具体流程如下:以涂有400 nm厚硅层的“绝缘体上硅”(SOI)晶圆为基底,依次进行光刻、干法刻蚀,以及金属氧化物半导体电容器(MOSCAP)与雪崩光电二极管(APD)的掺杂。随后,通过选择性生长硅与锗,形成APD的吸收层、电荷层与增益层。接着,通过“芯粒对晶圆键合” 技术,将III-V族化合物半导体(如InP或GaAs)集成至硅基平台,并添加薄栅氧化层(Al₂O₃或HfO₂)以提高器件效率,最后沉积厚介电层以实现封装并提升热稳定性。

这种独特的光子平台,可以在一块芯片上集成构建光神经网络所需的全部核心器件,实现晶圆级的一体化制造。这些器件包括片上激光器、光放大器、高速光探测器、节能调制器,以及具备记忆功能的相位调控器等。未来,该平台将助力数据中心承载更多AI计算任务,并为多个待优化问题提供解决方案。

这一平台有望解决当前AI芯片在计算能力和能耗方面的难题,为未来打造更高效稳健且可持续的AI加速硬件奠定基础!

参考资料

原文标题:面向节能AI/ML加速器的大规模集成光子器件平台

期刊名称:《IEEE量子电子精选期刊》

DOI:10.1109/JSTQE.2025.3527904,https://ieeexplore.ieee.org/document/10835188

新闻稿来源:IEEE光子学会

媒体联系人:Kristen Amoroso

邮箱:k.amoroso@ieee.org

地址:美国新泽西州

电话:+1(732) 562-6694

微信号|IEEE电气电子工程师学会

新浪微博|IEEE中国

Bilibili | IEEE中国

· IEEE电气电子工程师学会 ·

往

期

推

荐

仿生机器人技术蓬勃发展,但面临技术和成本障碍

无人机助推产业迈向新高度

数字干扰让人抓狂?这些方法或许能解决

世界最小心脏起搏器 —— 比米粒还小,注射植入后能自行溶解