(本文编译自SemiWiki)

在探讨数字信号处理器(DSP)面临的瓶颈时,人们的目光往往聚焦于计算吞吐量 —— 每秒的乘累加运算(MAC)次数、向量单元的宽度,以及时钟运行频率。然而,与专注于全天候语音处理、雷达系统或低功耗视觉应用的嵌入式人工智能工程师深入交流后,你会发现一个常被忽视的关键问题:内存停顿才是真正的 “隐形杀手”。

在当下的边缘人工智能与信号处理工作负载场景中,数字信号处理器需要在极为严苛的功耗与时间预算约束下,完成推理、滤波和数据转换等复杂任务。尽管计算核心不断迭代升级,边缘计算也致力于拉近计算引擎与内存之间的距离,但工具链的进步却未能彻底解决内存领域的困境。内存读写速度依旧难以满足需求,而矛盾的核心并非内存性能本身存在缺陷,而是数据无法在关键节点及时抵达计算单元,成为阻碍系统高效运行的主要障碍 。

为什么数字信号处理器会受延迟问题困扰

相较于通用中央处理器(CPU),嵌入式人工智能领域所采用的数字信号处理器,大多依赖不可缓存的内存区域,诸如本地缓冲区、暂存器,以及具备确定性的紧密耦合内存(TCM)。这一设计考量极具合理性:对于实时系统而言,缓存未命中引发的不确定性,或是非确定性延迟带来的风险,均是难以承受之重。然而,这种架构也存在弊端 —— 每一次内存访问都必须精准匹配确切的加载延迟,稍有偏差,处理器流水线便会陷入停滞。

实际应用中,当处理器处理频谱图解析、卷积窗口运算或波束形成序列时,一旦数据无法按时抵达,整个处理流程将瞬间中断。乘累加单元被迫闲置,任务延迟持续叠加,不仅运算效率大幅降低,功耗也在等待中被白白消耗,严重影响系统整体性能。

引入预测性加载处理

试想,若数字信号处理器能够识别出数据访问模式,精准识别循环体以固定步长读取内存的规律——例如每隔4个地址提取一个数据,并提前启动“深度预取”机制,让数据在实际加载指令下达前便已就位。如此一来,内存停顿与流水线气泡将不复存在,指令执行全程流畅无阻。

这正是传统预取模型或基于步长的流式传输技术所追求的目标。尽管这些技术已被广泛应用且成效显著,但它们并非本文探讨的核心。

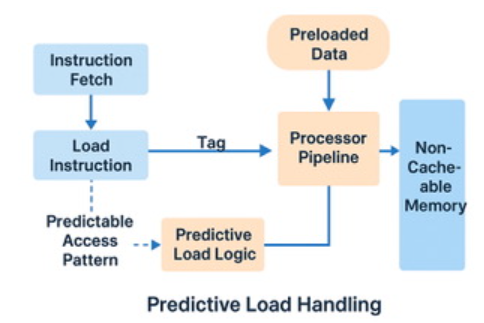

一项突破性的预测性加载处理技术正以全新范式颠覆传统认知。这绝非简单的预取技术升级,而是一场根本性的技术革新。与传统方法致力于预测下一个访问地址不同,预测性加载处理另辟蹊径,将核心焦点锁定在内存访问的时间维度,即精确预估每次数据获取所需的时长。

这项技术通过持续追踪历史加载操作的延迟数据,无论是静态随机存取存储器(SRAM)、缓存旁路操作,还是动态随机存取存储器(DRAM)的访问,精准掌握各个存储区域内存请求的常规响应时长。中央处理器(CPU)无需提前预发加载指令,而是维持常规运行节奏。将延迟预测应用于向量运算方面,依据预测的时间精准调度操作执行,使处理器能够在不改变指令流的情况下适应内存的时间安排。这种机制既非依赖推测性预判,也不存在额外风险,以保守稳健的策略完美契合确定性数字信号处理器(DSP)的流水线架构。特别是在处理存储于动态随机存取存储器(DRAM)的大型人工智能模型,或是频繁读写临时缓冲区时,由于这类场景下延迟虽稳定却相对漫长,该技术的优势得以充分彰显。

这种区别至关重要。我们不仅仅是在进行更智能的预取操作,而是在让处理器具备感知延迟和自适应时间安排的能力,即使在存在或不存在传统缓存或步长模式的情况下也是如此。

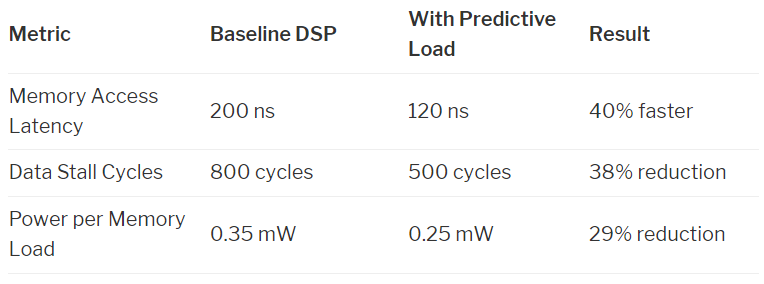

当将预测性加载处理集成到通用数字信号处理器流水线中时,它能立即带来可衡量的性能提升和功耗降低。下表展示了在典型的人工智能/数字信号处理器场景中的表现。这些数据反映了在以下工作负载中的预期效能:

对图像块进行卷积操作

滑动快速傅里叶变换(FFT)窗口操作

对量化输入进行人工智能模型推理

对流式传感器数据进行滤波或解码

最小代价,最大影响

预测性加载处理的一大核心优势在于其非侵入特性。这项技术无需复杂的深度重排序逻辑、缓存控制器,也不依赖繁重的推测机制,能够以灵活方式融入众多数字信号处理器(DSP)。无论是作为专用逻辑模块,还是借助编译器辅助的预取标签,它均可无缝嵌入指令分发或加载解码阶段。尤为重要的是,其确定性运行模式完全契合功能安全标准,包括国际标准化组织(ISO)制定的26262标准,这使其在汽车雷达、医疗诊断和工业控制系统等对安全性要求极高的领域具备独特适配性。

重新审视人工智能数据流水线

预测性加载处理揭示了一个重要趋势:提升运算效率,不仅在于强化数学计算能力,更在于确保数据能及时就绪。随着处理器速度与内存延迟之间的差距 —— 即 “内存墙”—— 持续扩大,未来高效的处理器架构将不再单纯追求更快的核心运算速度。相反,它们将依赖更智能的数据传输路径,实现信息的精准适时供给,从而消除导致高性能中央处理器(CPU)闲置的关键瓶颈。在数字信号处理器日益成为边缘人工智能运算主力的当下,我们坚信预测性加载处理将成为下一代信号处理核心的标志性技术特征。

毕竟,在数据处理领域,有时决定系统性能的关键并非时钟速度,而是数据的响应时延。

END