4月17日,JEDEC固态技术协会已经正式发布了HBM4内存的新标准。新标准的名称为JESD270-4,旨在提升HBM(高带宽内存)技术的性能和应用范围。

据悉,HBM4内存新标准在多个方面进行了显著改进,包括更高的数据传输速率、更大的堆栈容量和更低的功耗。

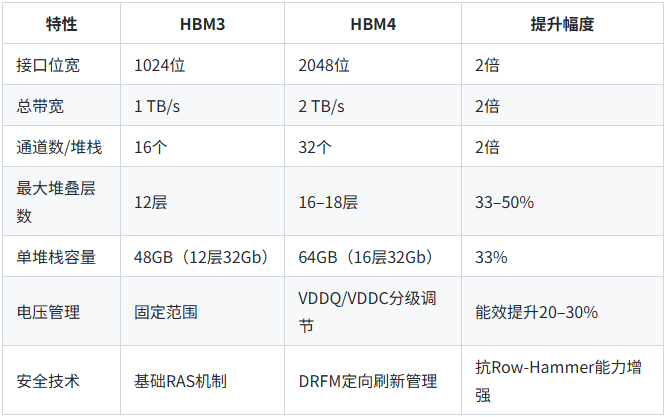

首先,HBM4采用2048位接口,传输速率提升至8 Gb/s,总带宽达到2 TB/s,较HBM3(1 TB/s)实现翻倍增长,显著提升了AI训练、高性能计算等场景的数据吞吐能力。这一突破主要得益于接口宽度的倍增和信号速率的优化。

其次,HBM4还支持4层至18层的TSV(硅通孔)堆叠,芯片密度达到24Gb或32Gb,单堆栈的最大容量可达64GB,这使得其在高性能计算(HPC)、生成式AI和高端服务器等领域具有更大的应用潜力。

另外,独立通道数从HBM3的16个增至32个,提升了多任务并行处理能力。电压管理进一步细化:VDDQ支持0.7–0.9V,VDDC可选1.0V或1.05V,降低功耗的同时提高能效比。

新标准还引入 DRFM(定向刷新管理)技术,有效缓解Row-Hammer攻击,并通过优化刷新周期提升可靠性(RAS)。HBM4保持与HBM3控制器的向后兼容性,允许混合使用两种内存类型。

HBM4与HBM3的关键差异对比

JEDEC HBM小组委员会主席、英伟达技术营销总监Barry Wagner表示:“HPC平台正在迅速发展,需要在内存带宽和容量方面进行创新。技术行业领导者合作开发的HBM4旨在推动AI和其他加速应用的高效、高性能计算的飞跃发展。”

HBM4新标准的发布标志着高带宽内存技术进入新纪元,其2 TB/s带宽、64GB堆栈容量和能效优化将重塑AI与超算硬件生态。随着SK海力士、三星等厂商的量产推进,以及生成式AI需求的爆发,HBM4有望在2025–2026年成为高性能计算的核心标配,同时推动半导体产业链的协同创新。

免责声明

本平台所刊载的所有资料及图表仅供参考使用。刊载这些文档并不构成对任何股份的收购、购买、认购、抛售或持有的邀约或意图。投资者依据本网站提供的信息、资料及图表进行金融、证券等投资项目所造成的盈亏与本网站无关。除原创作品外,本平台所使用的文章、图片、视频及音乐属于原权利人所有,因客观原因,或会存在不当使用的情况,如部分文章或文章部分引用内容未能及时与原作者取得联系,或作者名称及原始出处标注错误等情况,非恶意侵犯原权利人相关权益,敬请相关权利人谅解并与我们联系及时处理,共同维护良好的网络创作环境。

芯通社

- SemiWebs -

专注半导体-手机通信-人工智能

请长按下面二维码关注芯通社

▼

伙伴们

错过也许就是一辈子

还不快关注我们?