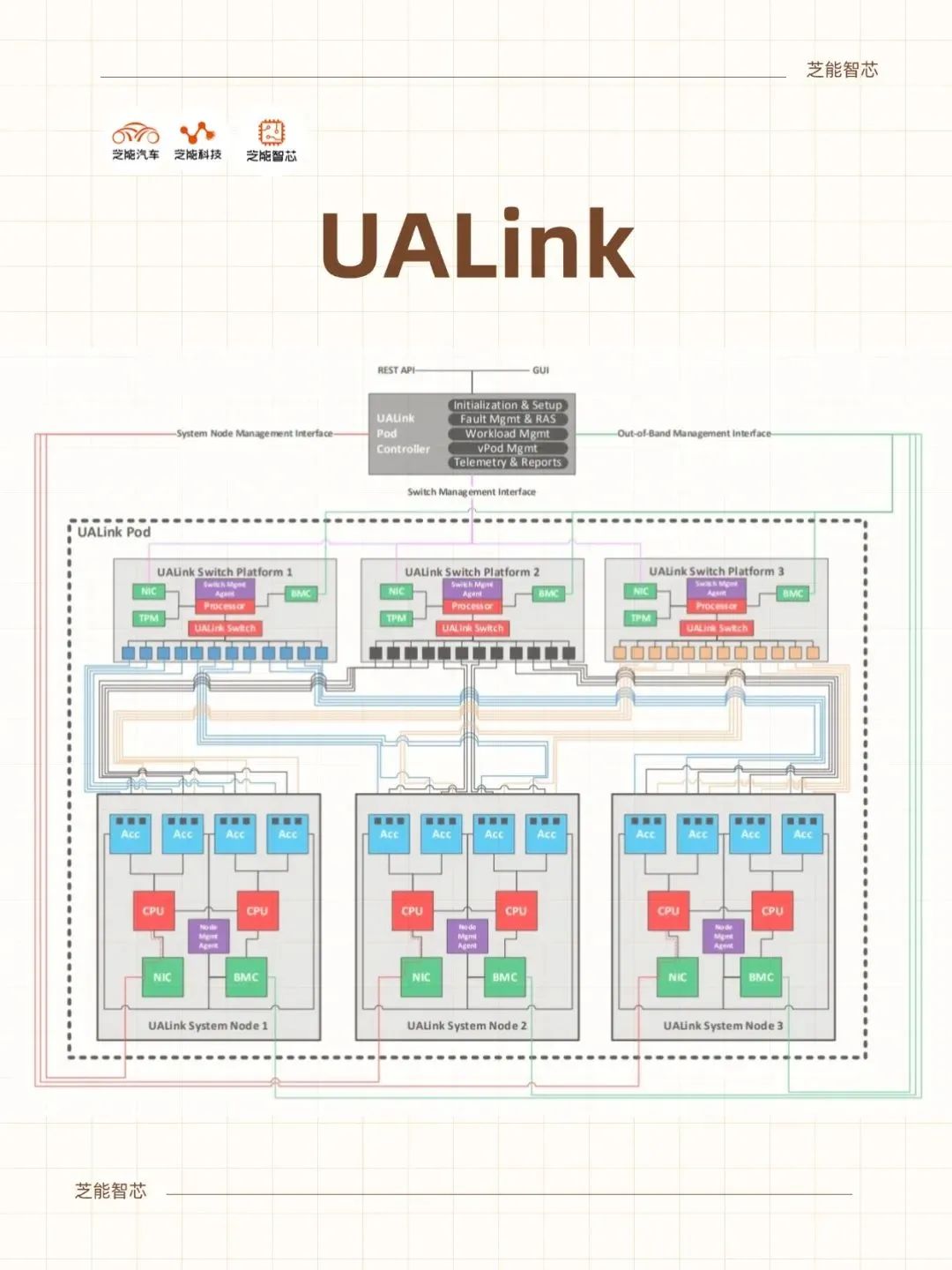

本文来自“UALink高速互联技术合集”,Ultra Accelerator Link(UALink)1.0规范正式发布,人工智能(AI)和高性能计算(HPC)领域开始有新的竞争。

UALink的技术创新与优势

UALink的应运而生,是AMD、Broadcom、Intel等业界领军企业针对英伟达NVLink专有技术所采取的一项集体战略举措。

英伟达凭借NVLink与NVSwitch技术,成功搭建起一套高效的GPU互联体系,在诸如Blackwell NVL72等机架级解决方案中,更是彰显出卓越的性能实力。但不可忽视的是,NVLink的封闭性特质,无形中为其他厂商设置了参与门槛,进而推高了系统集成的成本。

在此背景下,UALink以开放标准为突破口,成功打破了这一技术壁垒。它使得不同厂商的加速器,诸如AMD Instinct GPU、Intel Gaudi等,能够实现无缝协同工作。这一变革,极大地简化了数据中心部署的流程,降低了相关成本。UALink所构建的这一开放生态,不仅为系统集成商和数据中心运营商带来了更为灵活的操作空间,更为众多中小型AI硬件厂商开辟了参与市场竞争的新通道,激发了整个行业的创新活力。

UALink规范发布:挑战英伟达AI统治的开始

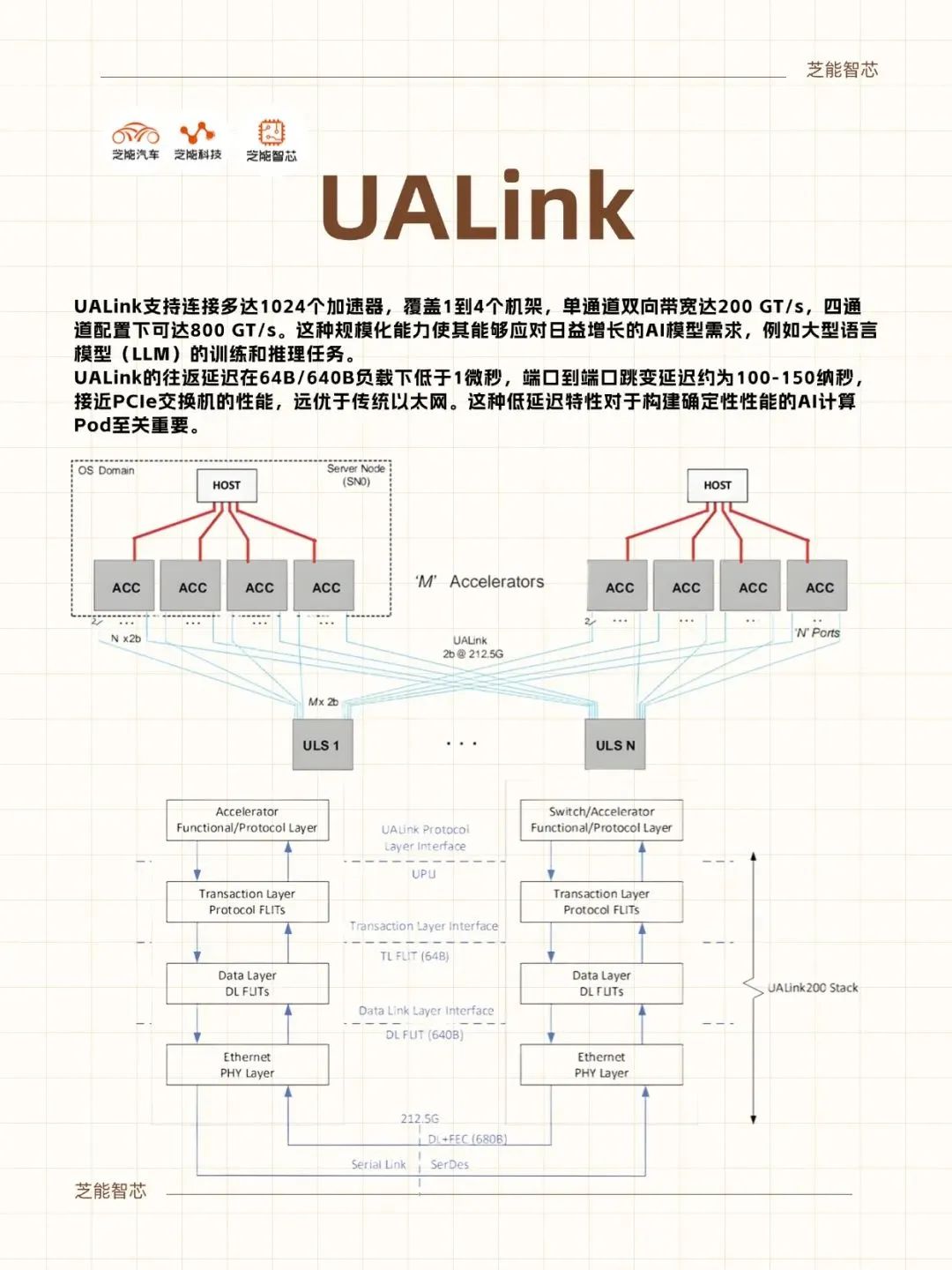

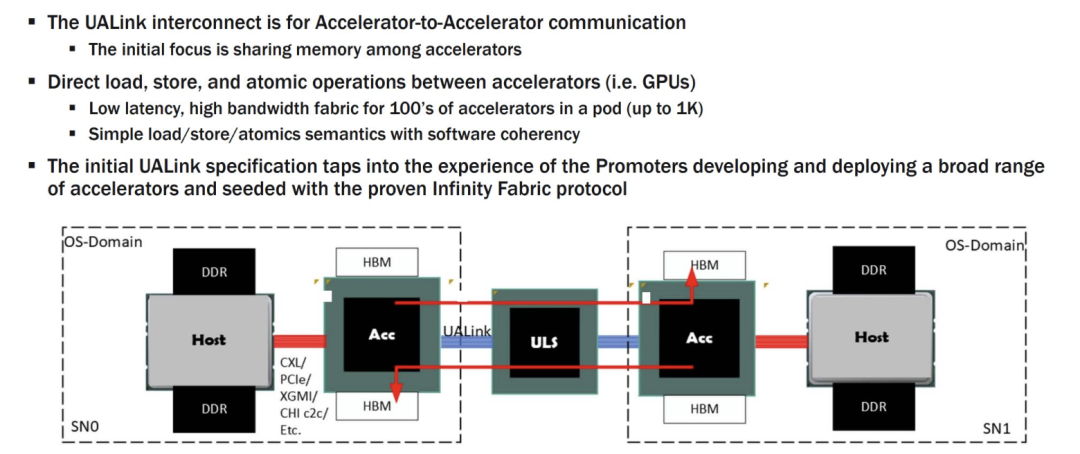

UALink 1.0的协议栈由物理层、数据链路层、事务层和协议层组成,针对AI和HPC负载进行了深度优化。

◎ 物理层:基于标准以太网组件(如200GBASE-KR1/CR1),通过改进前向纠错(FEC)和码字交织技术,显著降低延迟,同时保持与现有以太网生态的兼容性。

◎ 数据链路层:采用64字节到640字节的flit打包机制,结合循环冗余校验(CRC)和可选重试逻辑,确保数据传输的可靠性和高效性。

◎ 事务层:通过压缩寻址和直接内存操作(读、写、原子事务),实现高达95%的协议效率,优化了跨加速器的内存访问,特别适合AI训练和推理中对低延迟的严苛要求。

◎ 协议层:支持UALinkSec硬件级加密和可信执行环境(如AMD SEV、Intel TDX),为多租户数据中心提供安全隔离和机密计算能力。

这种分层架构设计在维持卓越性能的同时,显著降低了协议的复杂程度。与PCI-Express(PCIe)或Compute Express Link(CXL)相比,UALink在带宽和延迟方面展现出更为突出的优势,因而特别适用于大规模AI计算集群的部署。

UALink具备强大的扩展能力,能够支持多达1024个加速器的连接,覆盖范围从单个机架到四个机架,其单通道双向带宽高达200GT/s,在四通道配置下更是可提升至800GT/s。这种规模化的连接能力,使其能够轻松应对AI模型不断增长的计算需求,诸如大型语言模型(LLM)的训练与推理等任务。

此外,UALink在延迟表现上同样令人瞩目。在64B/640B负载条件下,其往返延迟低于1微秒,而端口到端口的跳变延迟大约在100-150纳秒之间,这一性能已接近PCIe交换机的水平,并远优于传统以太网。UALink的这种低延迟特性,对于构建具备确定性性能的AI计算Pod而言,具有至关重要的意义,能够确保AI计算任务的高效与稳定。

UALink的设计注重能效,其交换机的功耗仅为同等以太网ASIC的1/3到1/2,每个加速器可节省150-200瓦的功耗。更小的芯片面积和更低的功耗不仅降低了硬件成本,还减少了数据中心的电力和冷却开支,从而优化了总体拥有成本(TCO)。

这对于超大规模云服务提供商(如Google、Microsoft)尤为重要,他们需要平衡性能与运营成本。

UALink挑战英伟达的生态壁垒

英伟达在AI加速器市场中占据主导地位,这一成就并非仅仅依赖于其性能卓越的GPU硬件,更得益于NVLink、NVSwitch以及CUDA软件生态所形成的强大协同效应。以Blackwell NVL72机架为例,它借助NVLink技术实现了72个GPU的高效连接;而在Pod级扩展方案中,更是能够支持多达576个GPU的协同工作。不仅如此,英伟达即将推出的Vera Rubin平台,还将单机架的GPU数量进一步提升至144个,充分展现了其在硬件扩展能力上的领先地位。

相较之下,UALink 1.0在扩展潜力方面展现出了独特的优势,其理论上能够支持拥有1024个加速器的Pod规模。然而,英伟达所构建的生态壁垒,并不仅仅局限于硬件互连层面。CUDA的广泛应用以及经过深度优化的工具链,使得英伟达在开发者社区中拥有了极为深厚的根基。

面对这样的挑战,UALink联盟若想在市场中与英伟达有效竞争,仅仅在硬件层面发力是远远不够的。他们还需要大力推动软件生态的发展,例如ROCm、oneAPI等,加快这些软件生态的成熟进程。只有这样,才能吸引更多的开发者从英伟达平台迁移过来,从而真正打破英伟达在AI加速器市场的垄断地位,为行业带来更加多元化和富有竞争力的发展格局。

UALink联盟汇聚了来自多个关键领域的成员,包括芯片设计领域的AMD、Intel、Broadcom,云服务领域的Google、Microsoft、Meta,网络设备领域的Cisco,以及系统集成领域的HPE等。这种跨行业的广泛支持,为UALink技术的迅速落地奠定了坚实基础。举例来说,Synopsys已经成功推出了UALink IP控制器和验证IP,而AsteraLabs和Broadcom也计划投入生产UALink交换机,这些进展都彰显了联盟在推动UALink技术发展方面的积极作为。

然而,联盟在推进过程中也面临着不小的挑战,其中利益协调问题尤为突出。以Google和Meta为例,它们更侧重于定制加速器(如TPU)的研发与应用;而AMD和Intel则致力于推广通用GPU。这种成员间优先级的差异,可能会给UALink标准的演进带来复杂性。此外,由于英伟达的缺席,UALink在短期内难以撼动其在市场中的主导地位,特别是在高端AI训练市场这一关键领域。

尽管UALink1.0规范的发布标志着技术开发取得了重大进展,但从规范到商用产品的转化通常需要12-18个月的时间。联盟预计首批UALink设备将在2026年面世,而与此同时,英伟达的NVLink6.0和RubinUltra平台也有可能在2027年进一步提升性能。这意味着UALink需要在有限的时间窗口内,充分展示其性能和成本优势,以在激烈的市场竞争中抢占份额。

市场接受度在很大程度上将取决于UALink在实际部署过程中的具体表现。这其中包括它能否与现有的数据中心基础设施实现无缝集成,以及能否切实有效地降低AI训练和推理的总体成本。对于中小型企业而言,它们对开放标准的接纳程度可能会高于那些深度依赖英伟达生态的大型客户,这无疑为UALink开辟了一条切入市场的可行路径。

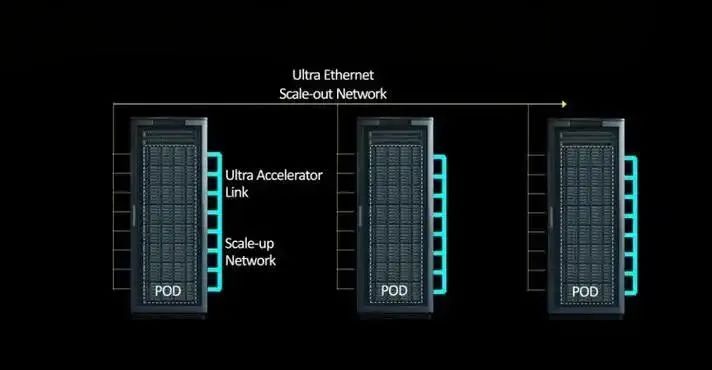

UALink与UltraEthernet Consortium(UEC)之间的合作,构成了其战略布局中的关键一环。UEC专注于对以太网进行优化,以满足AI和高性能计算在规模化方面的需求,而UALink则聚焦于Pod内部加速器之间的高速互连。将这两者结合起来,有望打造出一个涵盖“规模内与规模外”的全方位解决方案。举例来说,UALink能够用于连接包含8 - 128台服务器的Pod,而UltraEthernet则可实现跨Pod的扩展。这种协同作用极大地增强了UALink在生态方面的竞争力,但同时也带来了技术整合方面的复杂性。这就要求联盟在标准制定以及产品开发等各个环节,都必须保持高效且紧密的协作。

UALink 1.0规范的发布,无疑是AI产业竞争格局演变的一个重要标志。作为一项开放标准,UALink凭借其高速、低延迟以及低成本的互连技术,为AMD、Intel、Google等公司向英伟达的AI统治地位发起挑战,提供了至关重要的有力武器。

下载链接:

8、《3+份技术系列基础知识详解(星球版)》

9、《12+份Manus技术报告合集》

10、《100+份AI芯片修炼合集》

11、《60+份AI Agent技术报告合集》

《270+份DeepSeek技术报告合集》

《42篇半导体行业深度报告&图谱(合集)

亚太芯谷科技研究院:2024年AI大算力芯片技术发展与产业趋势

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。