----追光逐电 光引未来----

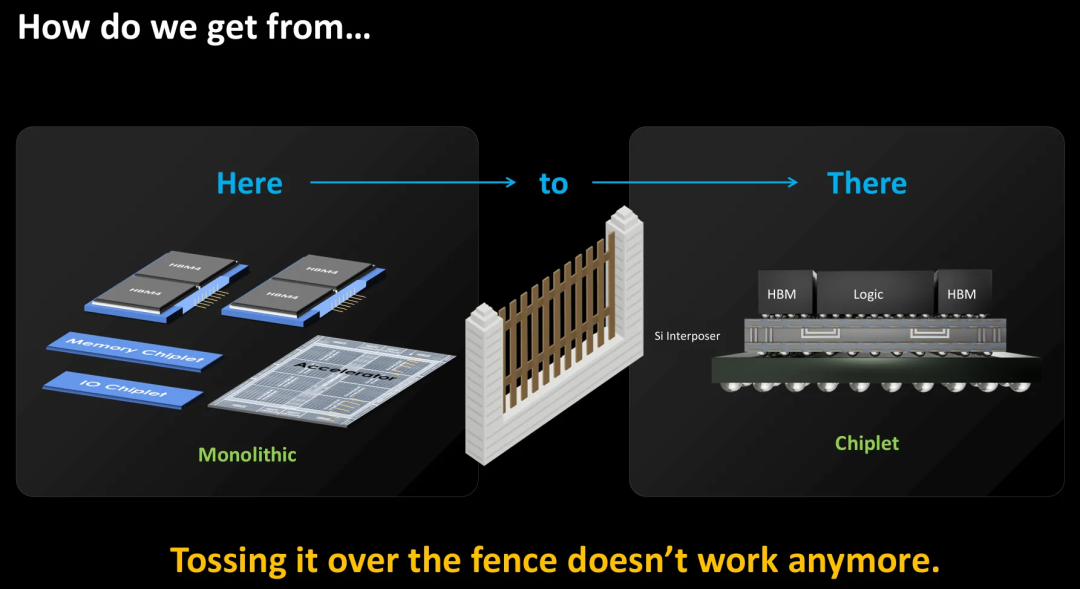

半导体行业正在经历从传统单片设计向更灵活的Chiplet架构转变,这种转变代表了芯片设计和制造方法的根本性变革,为提升可扩展性和性能优化提供了新的技术路径。

随着技术进步和芯片复杂度提升,芯片尺寸不断增大导致良率下降,在单个芯片上实现全部复杂设计变得越来越困难且成本高昂。

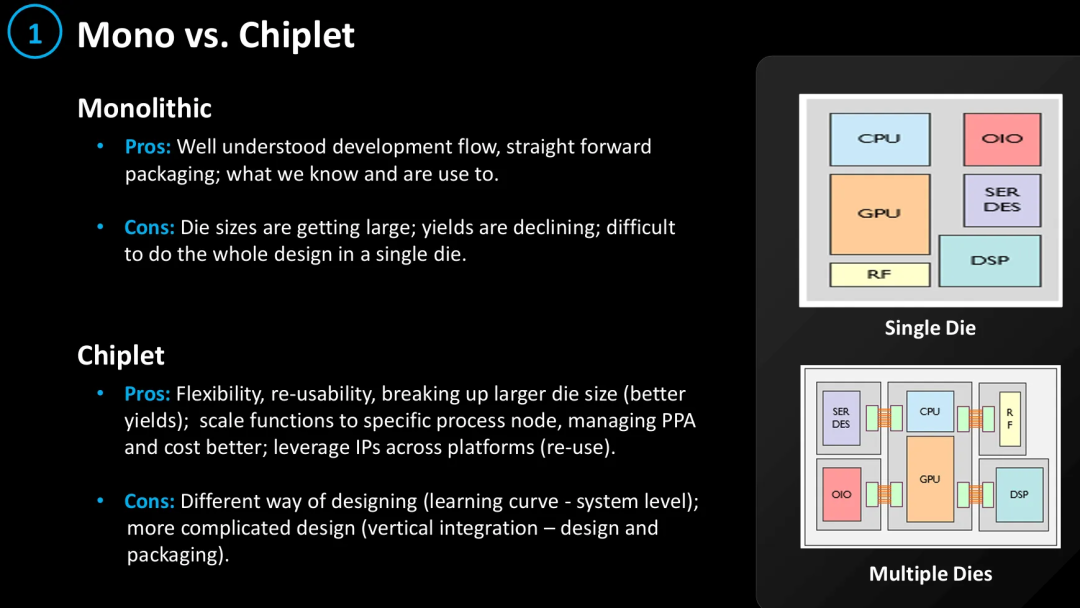

Chiplet技术:

① 将大型复杂设计分解为更小、更易管理的组件,提供更好的制造良率和设计优化灵活性。

② 将不同功能扩展到特定工艺节点,实现性能、功耗和成本之间的最佳平衡。

③ 便于在不同平台间复用IP,显著减少新产品的开发时间和成本。

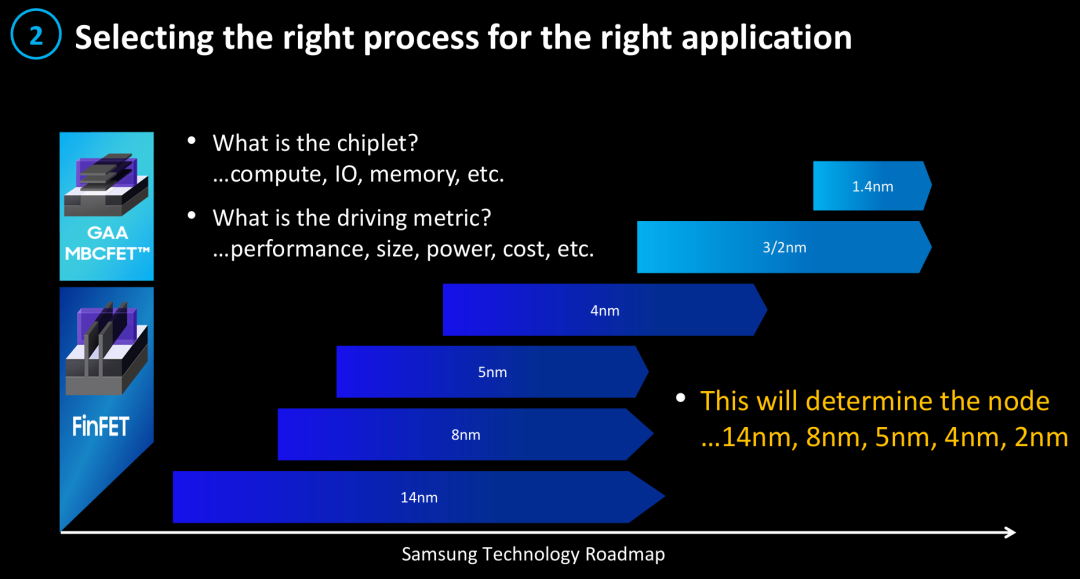

三星的技术路线图涵盖从成熟的14nm到尖端的1.4nm工艺,从FinFET(4nm)到环栅晶体管(GAA)技术(2nm)的工艺演进,特别适合人工智能和高性能计算应用,提供卓越的性能和能效。同时,14nm和8nm等成熟工艺节点在性能和制造成本之间取得平衡。

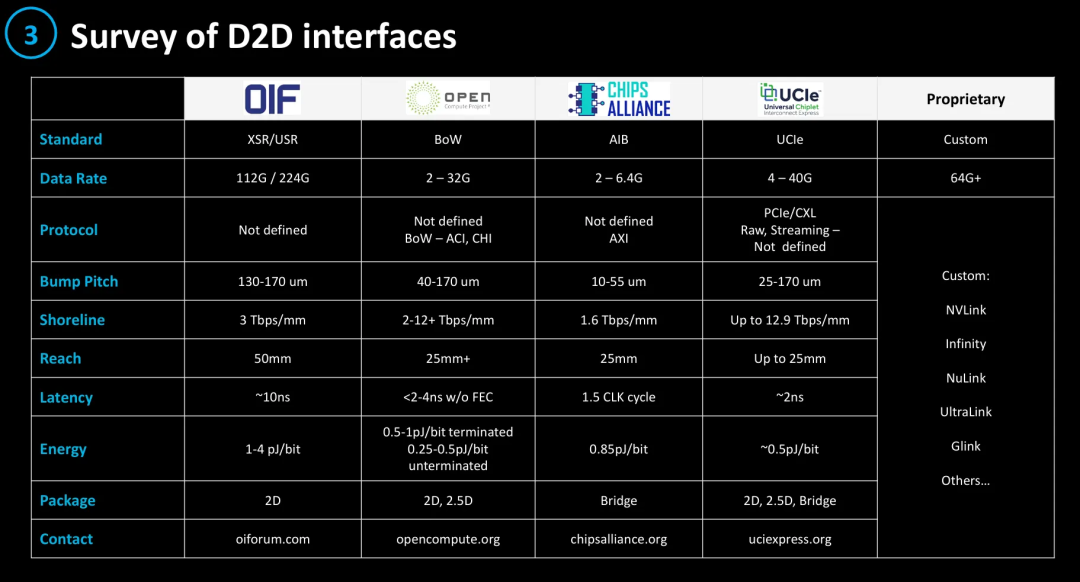

芯片间接口在Chiplet设计中面临诸多技术挑战,目前的行业标准提供了多种解决方案,每种方案都针对特定使用场景进行了优化:

① XSR/USR标准提供高达224G的带宽能力,传输距离可达50mm,但功耗和延迟较高。

② UCIe标准在性能和功耗效率之间取得了良好平衡,支持高达40G的数据速率,同时保持与PCIe/CXL协议的兼容性。

③ Bunch of Wires (BoW)标准强调功耗效率,在终端配置中实现0.5-1pJ/bit的能效,同时保持合理的带宽能力。

④ Advanced Interface Bus (AIB)提供了定义明确的协议结构和成熟的技术实现,但专有特性可能限制更广泛的采用。

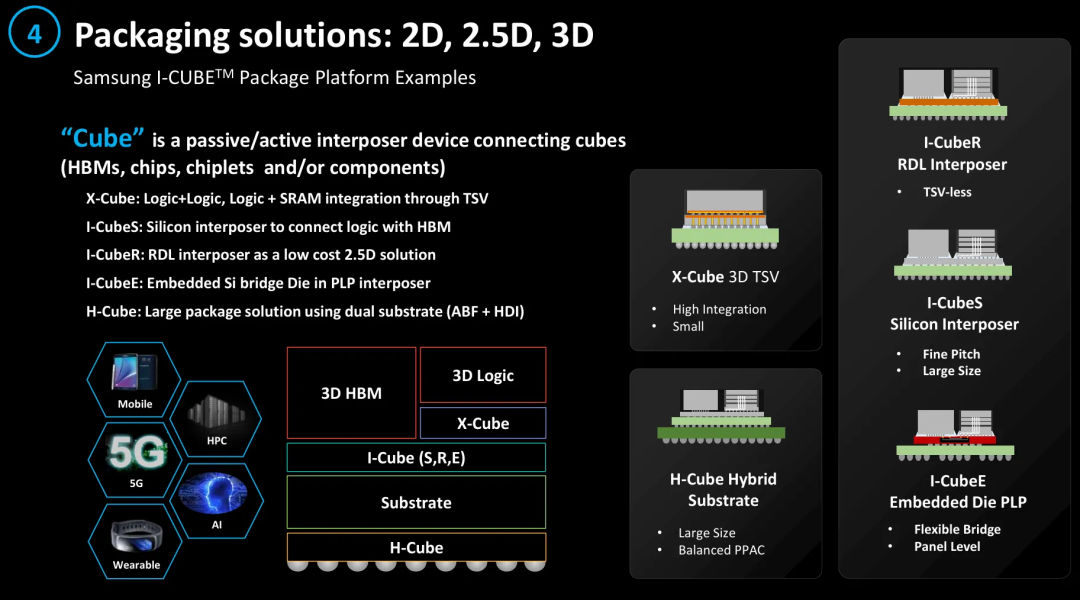

三星的I-CUBE™技术平台提供了多种集成方案,包含多种先进封装技术,每种技术都针对特定技术挑战和使用场景设计。

X-Cube技术通过硅通孔(TSV)实现先进的逻辑到逻辑和逻辑到SRAM集成。这种方法允许高密度垂直集成,最大化互连带宽的同时最小化整体占用面积。TSV的实现需要精确工程来管理热问题和应力效应,但为高带宽应用提供了优越性能。

I-CubeS技术利用硅中介层促进逻辑芯片与高带宽内存(HBM)的集成。这个解决方案解决了高性能计算应用中内存带宽的关键挑战。硅中介层提供高密度互连平台,支持逻辑芯片和HBM堆栈之间数千个连接。硅中介层的细间距能力与传统封装基板相比能提供显著更高的带宽。

I-CubeR解决方案引入了重布线层(RDL)中介层,作为一种经济高效的2.5D集成方案。此技术无需昂贵的硅中介层,同时仍能提供许多应用所需的互连密度。相比硅中介层,RDL方法提供更好的散热性能和更简单的制造复杂度,特别适合主流应用。

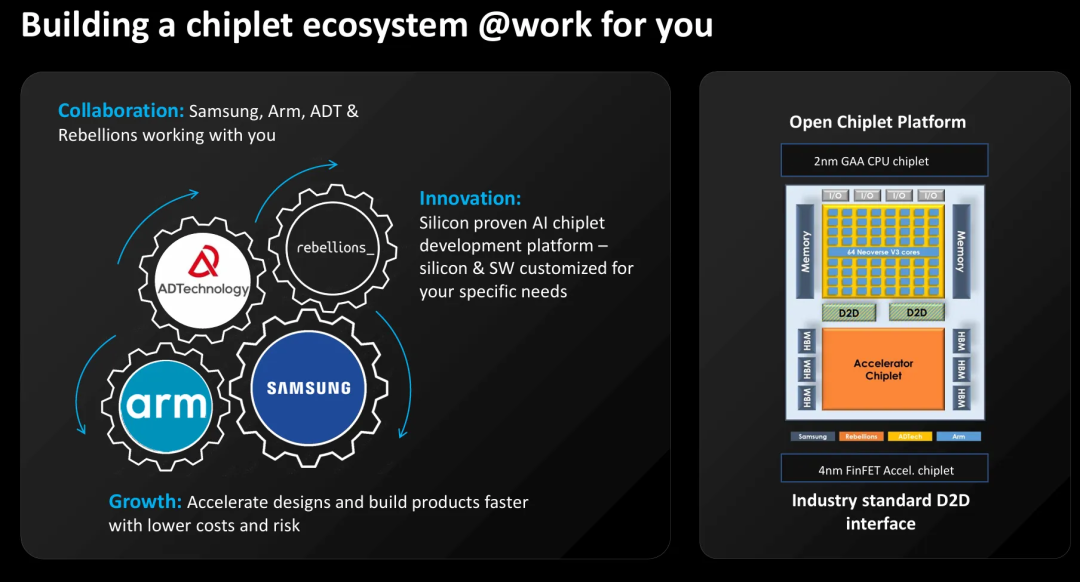

Chiplet技术的成功很大程度上依赖于支持设计、制造和集成的强大生态系统。三星、Arm、ADT和Rebellions之间的合作标志着建立Chiplet设计和集成标准化方法的重要进展。这种合作结合了三星的先进制造能力、Arm的处理器专业知识、ADT的设计工具和Rebellions的创新AI解决方案。

此生态系统的技术框架包括标准化的芯片间接口、经验证的设计方法和全面的测试协议。

三星完整晶圆厂解决方案,强调四个关键支柱:

① 基础在于其先进的晶圆厂技术,特别是在环栅晶体管(GAA)架构方面的领导地位。

② 存储技术(特别是HBM解决方案)的集成解决了内存带宽和容量等现代计算架构中最关键的挑战。

③ Cube™技术的先进封装解决方案。

④ SAFE生态系统。

随着新标准的出现和集成技术的改进,Chiplet技术将继续发展。三星的全面方法既能够适应这些发展,又能保持与现有解决方案的向后兼容性。这种灵活性确保了Chiplet设计投资的长期价值。

申明:感谢原创作者的辛勤付出。本号转载的文章均会在文中注明,若遇到版权问题请联系我们处理。

----与智者为伍 为创新赋能----

联系邮箱:uestcwxd@126.com

QQ:493826566