----追光逐电 光引未来----

一、什么是芯片封装?

芯片是电子元件的重要组成部分,芯片必须与印刷电路板(Print Circuit Board,PCB)之间形成电互连,以实现芯片之间或芯片与其它电子元器件之间的“沟通”。

芯片主要是以硅为载体的高精度集成功能单元,因为硅材料易脆裂的特点,所以芯片不能直接与PCB 直接形成电互连,而需要通过各种形式对脆弱的芯片进行保护,再与PCB相连。

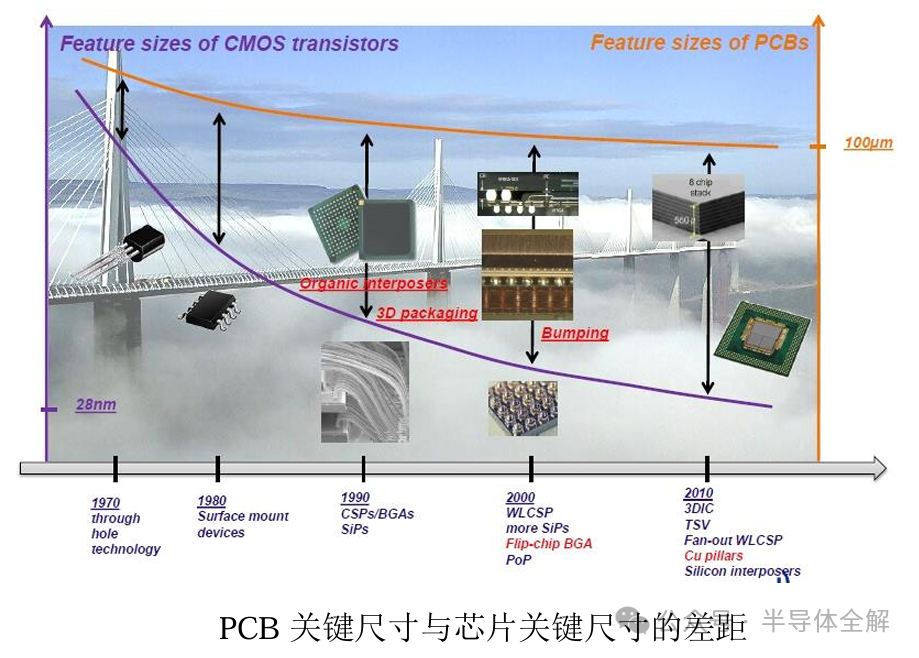

在集成电路诞生以来50多年的历史里,芯片的集成度持续提高,其关键尺寸急速缩小; 相比之下,PCB关键尺寸缩小的速度很缓慢;这就造成了芯片与PCB之间关键尺寸的差异持续扩大,如下图所示。

封装就是针对芯片因所用基底材料特性、芯片集成度与PCB集成度不匹配等问题,运用 相适应的材料和工艺,对脆弱的芯片进行保护,同时调整芯片焊盘的密度,使之与PCB焊盘的密度相匹配,是芯片与PCB之间的“桥梁”。

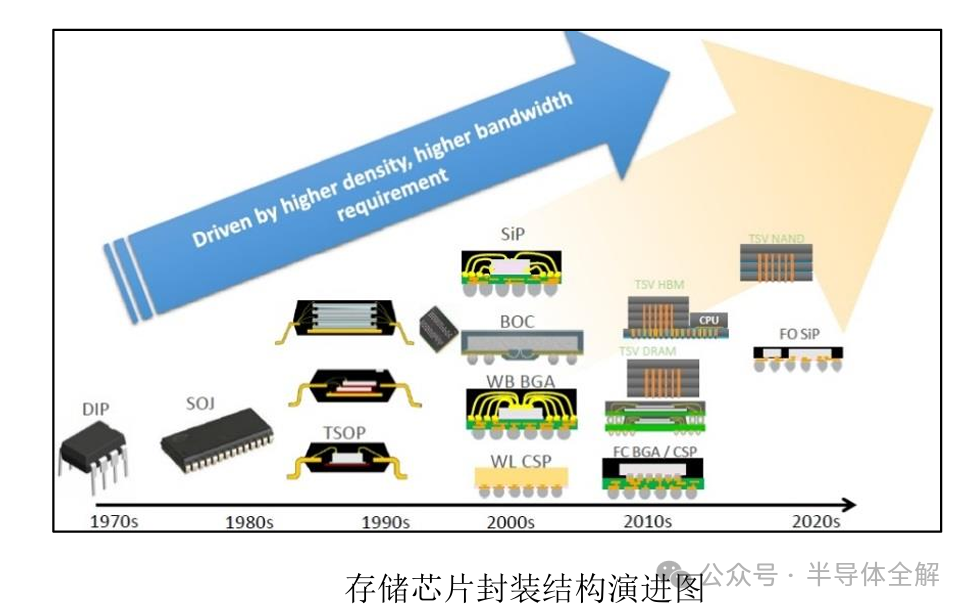

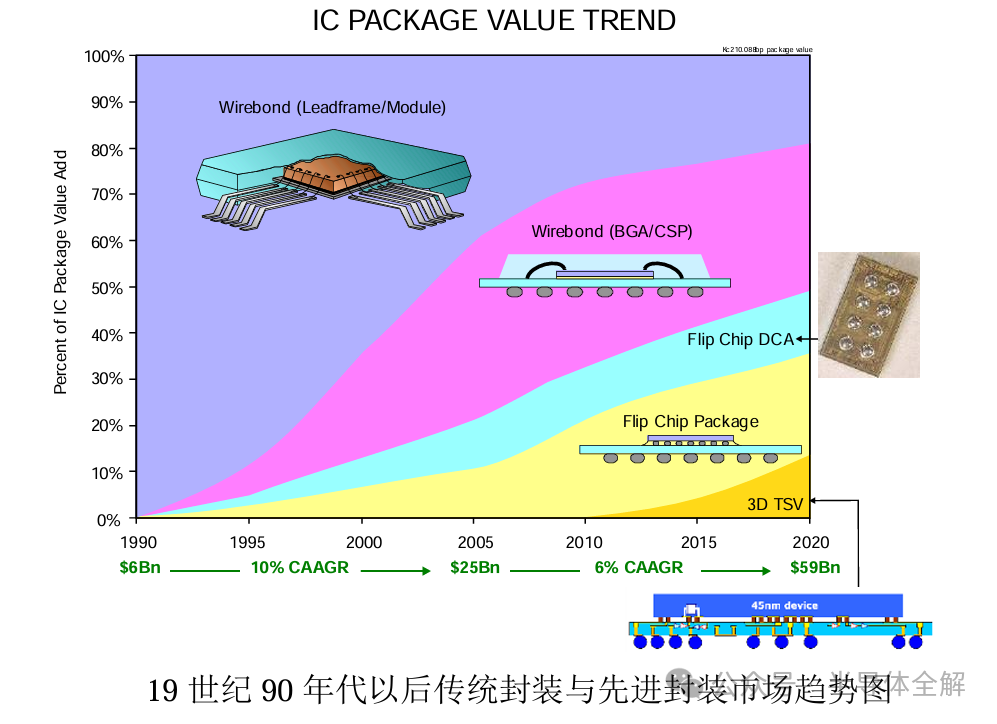

在过往的50多年里,封装结构及技术不断发展,以适应芯片集成度和性能不断提高的趋 势。下图是以存储芯片的封装技术演进为例,其早期产品的封装结构为双列直插式封装(Dual in-line Package,DIP),后来采用小尺寸 J 形引脚封装(Small Out-Line J-Lead,SOJ)和薄型小尺寸封装(Thin Small Outline Package,TSOP)结构,以提升封装的引脚数;为提高存储容量,开发了芯片堆叠封装;近十年,倒装芯片和硅穿孔(Through Silicon Via,TSV)技术被广泛运用于高性能存储芯片的封装,在增加存储容量、提高存储速度的同时,降低了产品的功耗。

芯片集成度按摩尔定律不断向前发展,必然推动封装技术的发展,尤其在“超越摩尔定律”的驱动下,对封装技术提出了更高的要求。

二、引线键合技术支撑下封装技术的发展

封装技术的一个关键功能是实现芯片与封装体之间、芯片与芯片之间的电互连。

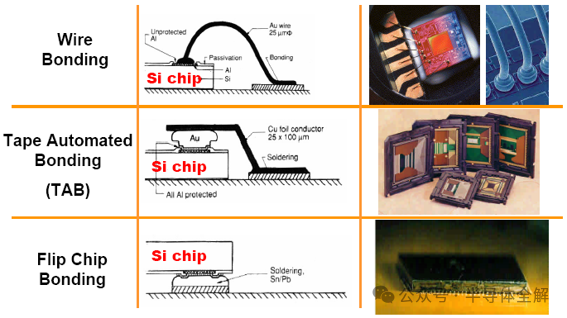

引线键合(Wire Bonding)是封装工艺中常用的电互连方式,是将芯片焊盘与封装体焊盘之间、芯片与芯片的焊盘之间用金属细丝连接起来的技术。

其原理是采用加热、加压和超声等方式去除焊盘金属表面的氧化层和污染物,让金属细丝与焊盘金属面接触,达到原子间的引力范围,使界面间原子扩散而形成焊接。

常用的引线键合方式有三种:热压键合、超声键合和热超声键合。

目前,大约90%的引线键合封装采用热超声键合工艺。

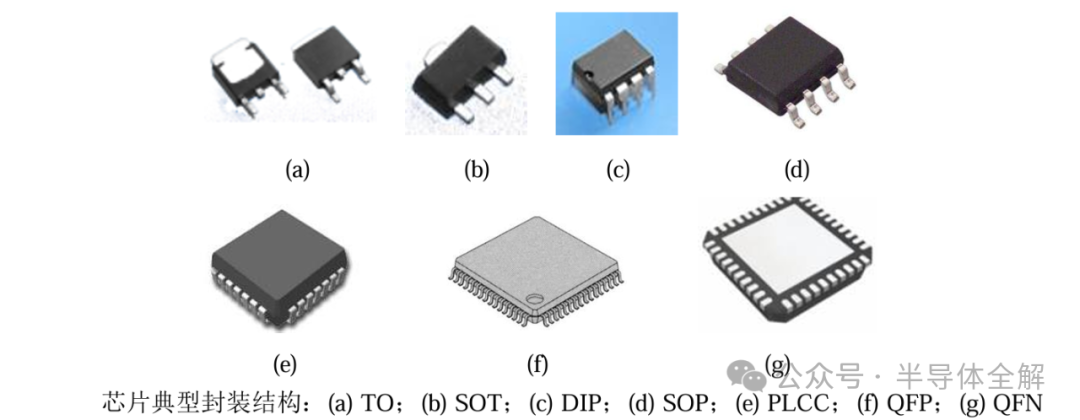

在集成电路出现后的一个相当长的时间内,因为芯片集成度不高,焊盘个数少、焊盘节距(两个焊盘中心的距离)大,所以芯片与封装体的电互连一直采用引线键合方式;封装外 形以晶体管外形封装(Transistor Out-line,TO)、双列直插式封装、小外形封装 (Small Out-line Package,SOP)、带引线的塑料芯片载体封装(Plastic Leaded Chip Carrier,PLCC)、方型扁平式封装 (Quad Flat Package,QFP)、方型扁平无引脚封装(Quad Flat No-lead Package,QFN)为主,芯片的载体以铜制引线框架为主,如下图所示。

到上世纪90年代,以有机基板为载体的球栅阵列封装(Ball Grid Array,BGA)产品数量开始增加;这是因为芯片集成度不断提高,芯片和封装体的焊盘密度急剧增加,以传统框架为载体的封装形式已经不能满足芯片封装要求。

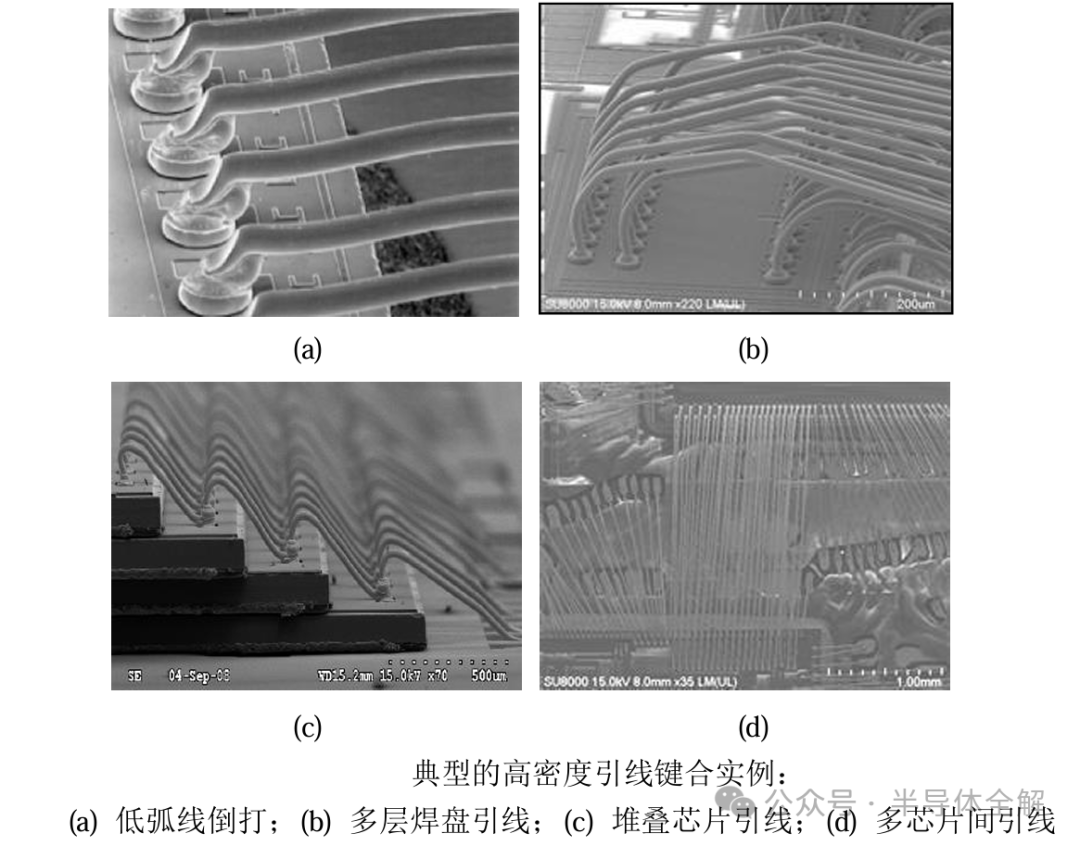

在此阶段,引线键合技术持续发展、创新,产生了如低弧线倒打、多层焊盘引线、堆叠芯片引线、多芯片间引线等技术,使其在引线密度上得到了极大的提升,满足了BGA封装初期的要求。下图展示的是高密度引线键合实例。

三、焊球凸块技术在先进封装发展中的应用

2004年以后,芯片工艺的关键尺寸进入到纳米时代,其集成度和功能进一步提高,单颗芯片内的焊盘数量已接近或超过 1000 个,传统的引线键合技术已不能满足芯片功能快速增加的要求。

另一方面,为适应移动类电子产品对功耗、散热、寄生效应的要求,急需一种性能更优的方式以实现芯片与封装体的电互连。

在这种情况下,基于凸块(Bump)技术的倒装芯片封装(简称凸块封装)技术开始被大规模使用。

传统引线方式将芯片正面朝上放到基板上,称为正装,再用引线实现芯片与封装体之间的电互连;

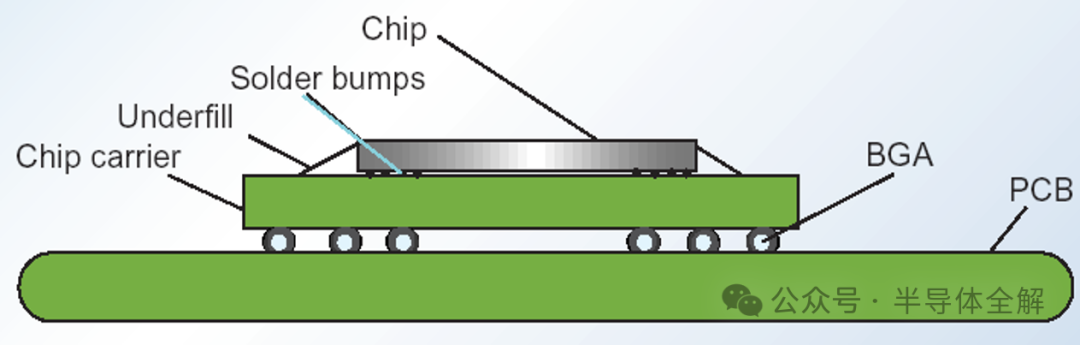

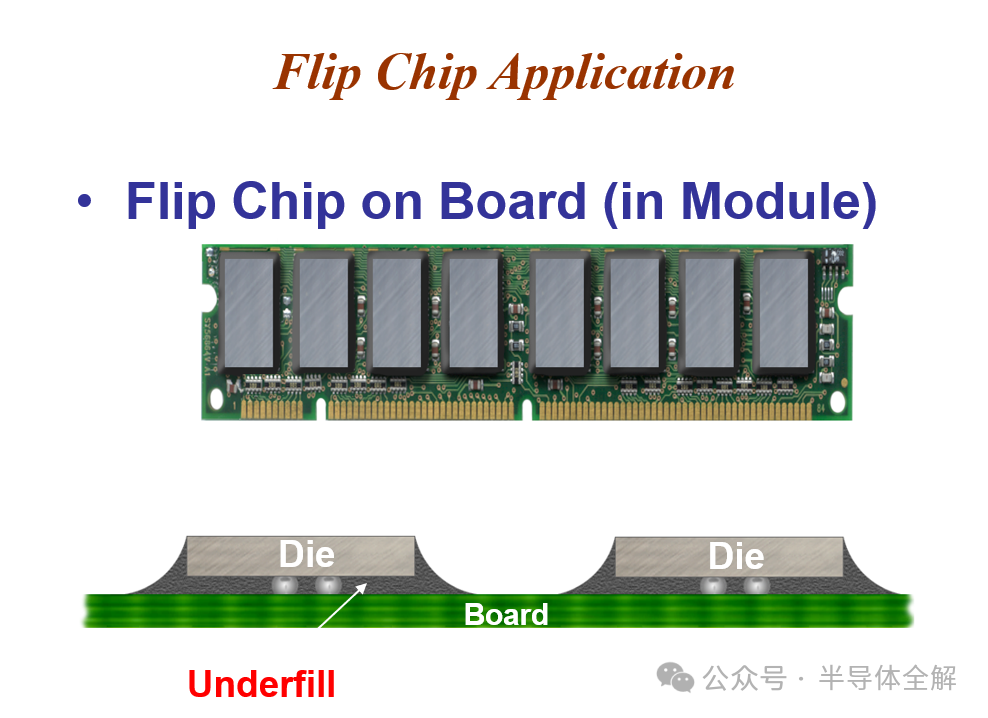

而倒装芯片技术是将芯片的正面朝下,使芯片正面与基板面对面,芯片与基板之间的焊盘采用凸块进行电互连,称为倒装。

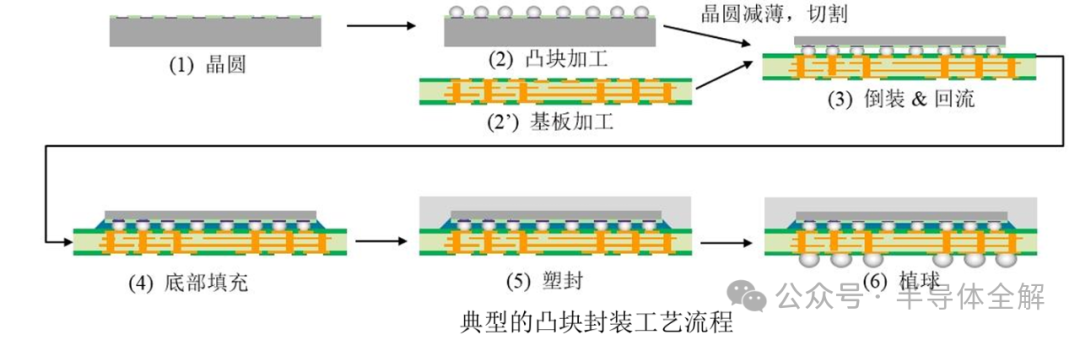

下图是典型的凸块封装工艺流程。

相比引线键合方式的电互连,凸块封装的电互连有多方面的优势。凸块封装的电互连无需引线,可以形成最短互连,降低电阻、电感等寄生效应,改善电性能;

在电互连中,充分利用了芯片面积和基板面积,缩小了封装尺寸;制程一致性高,易于良率管控;结合在芯片与基板之间的底部填充技术,产品的可靠性可以得到保证。

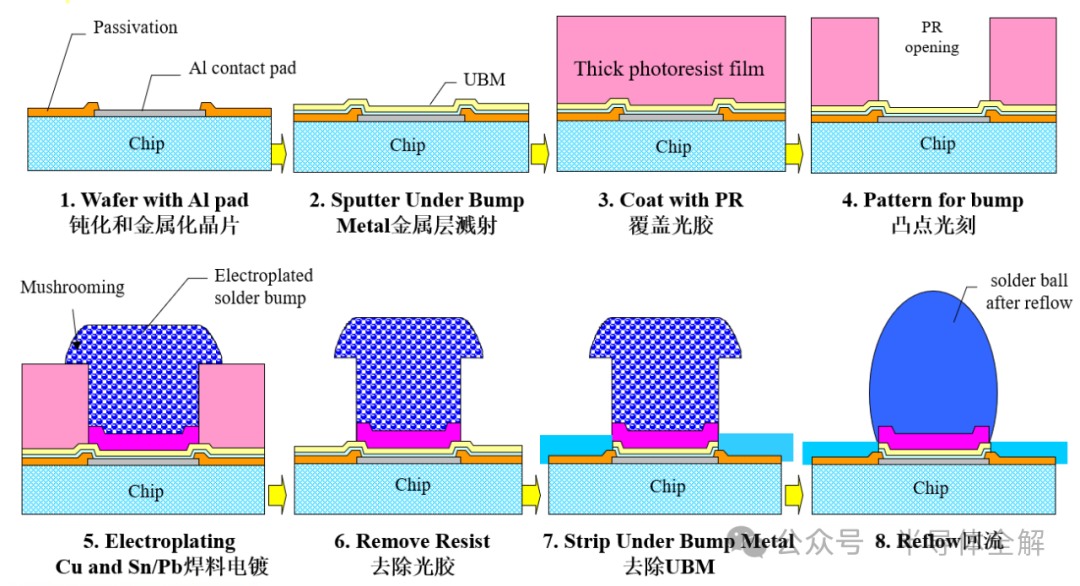

凸块封装技术最初由IBM 在上世纪 60 年代率先提出,即C4(Controlled Collapse ChipConnection)技术,其工艺原理是采用气相沉积的方法在芯片焊盘上沉积凸块下金属(Under Bump Matelization,UBM)和焊料(Solder),然后将芯片翻转加热,利用熔融的焊料与陶瓷板上的焊盘相结合。但是这种工艺成本过高,所以,后续工艺中焊料逐步由印刷锡膏和电镀两种方式所取代,而物理气相沉积或溅射配合电镀工艺作为加工UBM最常用的方式被沿用至今(化学镀镍作为一种低成本的 UBM 加工方案在较小的范围内运用)。

这一类凸块结构的特点是在薄的 UBM 上方加工厚的焊料,焊料使芯片与基板形成电互连;这一类凸块被称为焊球凸块(Solder Bump)。

焊球凸块因其易于加工、对倒装芯片工艺要求相对较低、高可靠性等优点,从凸块封装技术诞生至其后很长一段时间,一直作为优先选择的电互连结构。

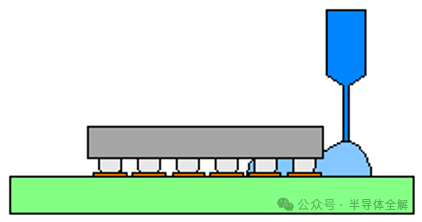

在倒装芯片和回流焊接后,芯片须与基板之间保持一定的间隙,称为站立高度,以利于进行其后的底部填充工艺,如下图所示。

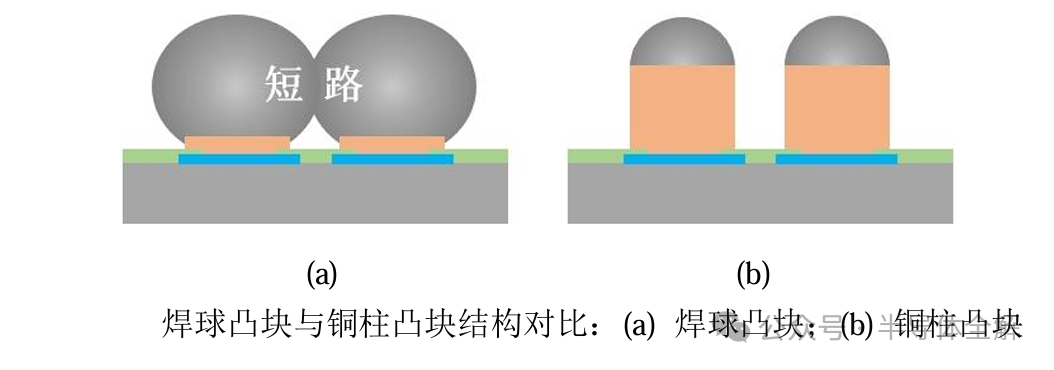

过小的站立高度会极大地增加底部填充工艺的难度与成本,所以,在焊球凸块结构中必须用大量的焊料,在实现芯片与基板之间电互连的同时,保持芯片在基板上的站立高度;又因为焊球凸块在熔化状态下其水平面尺寸必然大过其高度尺寸,所以焊球凸块的节距不能太小,否则会引起焊球凸块之间桥连,形成短路,如图(a)所示;这一点成为了焊球凸块结构的短板。

四、铜柱凸块技术在先进封装发展中的应用

铜柱凸块(Copper Pillar Bump)很好地解决了焊球凸块在节距上的限制问题,而且在热 学性能、电学性能、封装成本等方面有着更为优异的表现。

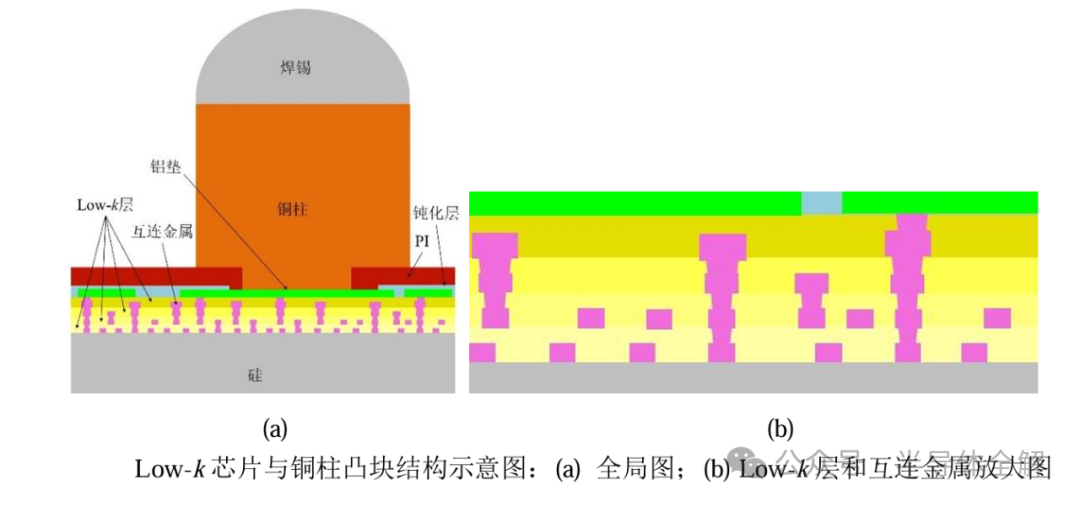

铜柱凸块用厚铜做UBM,把铜的厚度增加到数十微米,同时适当降低焊料的用量,利用 铜柱来提高凸块的站立高度,而不受焊料尺寸的限制,这样,很好地规避了焊球凸块在高度与节距上的矛盾,在不降低凸块高度的前提下进一步缩小凸块的节距,如图(b)所示。

凸块不但实现了芯片与基板之间的机械连接,而且建立了芯片与基板之间的热连接和电连接。

铜的导热系数为401 W/(m•K),锡的导热系数为64 W/(m•K),即铜比锡的导热能力强,所以铜柱凸块能更好的将芯片工作时的热量传递到芯片以外的区域。

铜也是电的良导体,其电阻率为1.7 μΩ•cm,而焊料中锡的电阻率是11.5 μΩ•cm,所以在相同尺寸条件下,铜柱凸块相比焊球凸块具有更小的电阻,可降低封装引入的电阻。

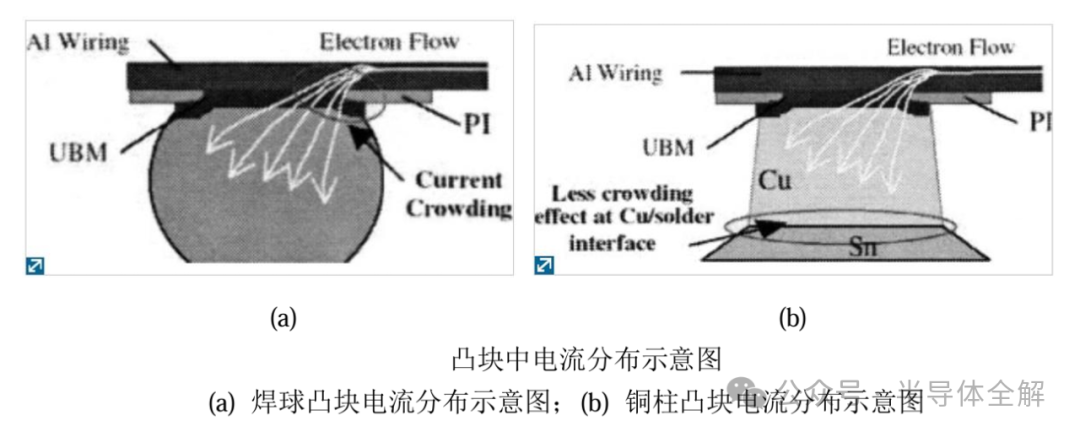

铜柱凸块比焊球凸块具有更好的抗电迁移性能。电迁移效应引起的焊球凸块结构破坏是凸块封装结构中常见的失效模式,当电流流过焊球凸块时,在 UBM 与焊料界面处有很高的 电流密度,加快了电迁移速率,使焊球凸块产生空洞,导电的截面积减小,进一步增加电流密度,加速结构失效,如下图所示:

而且铜柱良好的导热能力可以有效降低芯片和凸块区域的温度,从而提升凸块抗电迁移性能,提升封装结构的可靠性。在小尺寸凸块的应用场景下,铜柱凸块优秀的抗电迁移性能就更为重要。

选用铜柱凸块,并且对基板进行优化设计后,可以形成在铜柱凸块封装中所特有的铜柱导线直连(Bump on Trace,BOT)结构,这种结构不但进一步减小了凸块的节距,而且减少 了基板的层数,降低了基板的制作成本,这是采用焊球凸块所不能实现的,是铜柱凸块封装的另一个优点。

下表汇总对比了封装工艺中引线键合、焊球凸块和铜柱凸块三种电互连方式的性能,可以看出铜柱凸块在工艺一致性、生产效率、电互连密度、抗电迁移性能、电阻等多项性能上均优于焊球凸块和引线键合电互连方式。

铜柱凸块适应了封装技术高密度、低功耗、低成本的要求,被广泛应用于模拟类、数字类、存储类、射频类芯片封装的电互连,成为高端芯片封装互连的优选方案。

因为铜柱凸块封装优异的性能,所以世界各大集成电路公司相继在其高端产品中采用此项技术。

五、铜柱凸块技术具体应用案例

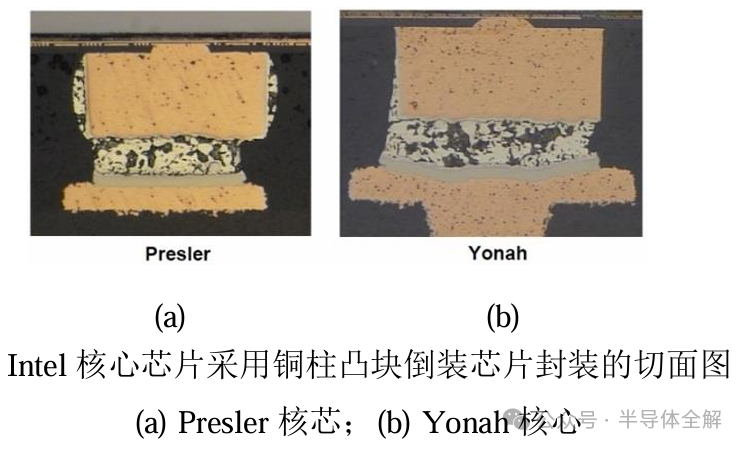

2005年,Intel 65 nm 工艺生产的 Presler 芯片采用基于铜柱凸块的倒装芯片封装技术进行封装;2006年,Intel 再次用铜柱凸块封装技术对其 Yonah 核心芯片进行封装;

下图展示了Presler 和 Yonah 核心芯片采用铜柱凸块封装的切面结构;

此后,Intel在其推出的所有处理器中均采用了这种结构。

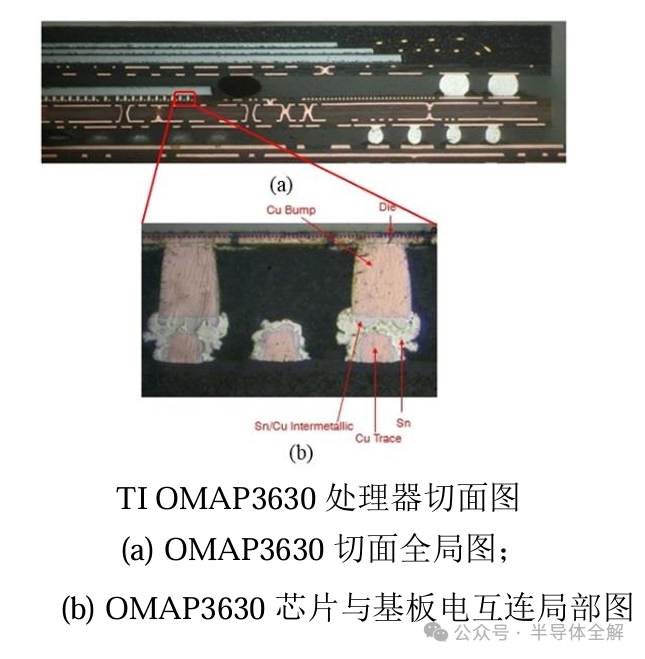

德州仪器(Texas Instrument,TI)在其应用处理器 OMAP3630 上验证了铜柱凸块封装,如下图所示,并在其后推出的 OMAP4 系列应用处理器中大量使用。

超微半导体公司(Advanced Micro Devices,AMD)的图形处理器HD6490M 采用了相同的封装结构。

当芯片关键尺寸达到40nm,并逐步向28nm 制程转变,芯片体积进一步缩小,对空间、密度提出了更高的要求,加上成本压力有增无减,促使芯片厂商纷纷改变产品结构,采用铜柱凸块封装技术。

主要芯片大厂,如TI、高通(Qualcomm)、迈威尔(Marvell)、博通(Broadcom)、英飞凌(Infineon)纷纷跟进采用,在其制定的技术路线中明确将铜柱凸块封装作为必须实现的技术,在其产品系列中必须有产品采用此技术进行封装,而且需逐步增加此封装技术在其产品中的占比。

在“More Than Moore”概念的推动下,铜柱凸块在先进封装技术中起到了更为重要的作 用,以满足“More Than Moore”对封装产品多功能的要求。

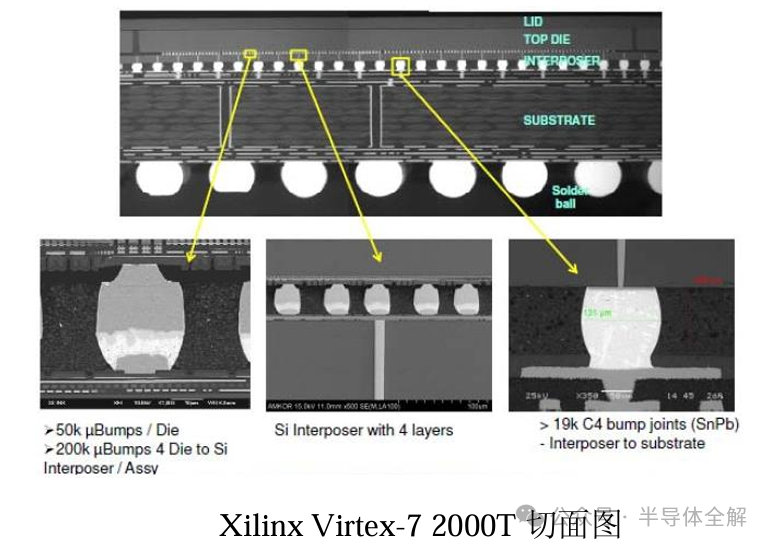

2012 年赛灵思(Xilinx)在 TSMC 和安靠(Amkor Technology)的帮助下,首次尝试将 2.5D封装技术运用到其产品 Virtex-7 2000T 中。

TSMC 采用TSV 技术制作出高密度的硅基转接板(Si Interposer),然后,Amkor 将 4 颗采用 28 nm 工艺制作的现场可编程门阵列(Field Programmable Gate Array,FPGA)芯片倒装到硅基转接板的一面,使其形成互连,硅基转接板的另一面与有机基板相连,最终形成 BGA 封装。在这一产品中,FPGA 芯片就是通过铜柱凸块与硅基转接板形成互连,如下图所示。

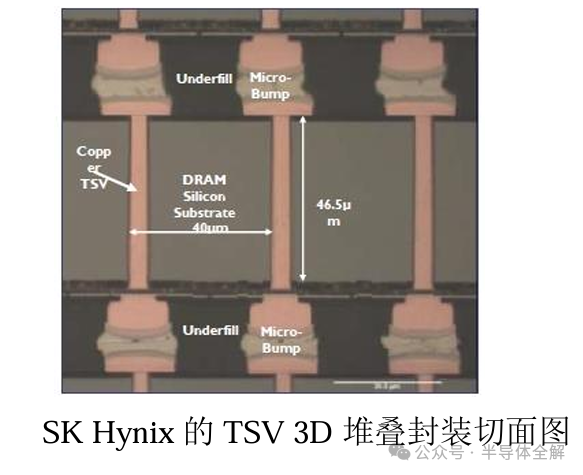

海力士(SK Hynix)的 3D 封装中,芯片之间通过铜柱凸块形成互连,如下图所示。

参考文献:

(1)龙欣江 晶圆级铜柱凸块封装结构设计、工艺和性能研究[D].

申明:感谢原创作者的辛勤付出。本号转载的文章均会在文中注明,若遇到版权问题请联系我们处理。

----与智者为伍 为创新赋能----

联系邮箱:uestcwxd@126.com

QQ:493826566