(本文编译自Semiconductor Engineering)

由于芯片复杂度不断提升,芯片制造商从单片芯片转向多芯片组件,需要进行更多次迭代,而且定制化程度不断提高使得设计和验证工作更加耗时,因此芯片首次流片成功率正急剧下降。

一项新的功能验证调查中的细节凸显出,开发既具备功能性又可靠的先进芯片,难度日益增大。在许多情况下,这些芯片尺寸比光罩大小的SoC更大,并且它们集成了多种组件和布线方案,这可能会降低其稳定性。因此,它们需要进行更多的优化和更多次的迭代。

这些芯片集成了更多逻辑电路,其中一些是在不同的工艺节点上开发的。它们拥有更多SRAM和更多互连线路,而这两者的发展速度都与逻辑电路的发展速度不一致。此外,它们需要更多软件支持,就大预言模型(LLM)和其他AI算法而言,软件的发展速度比硬件要快得多。它们还需要复杂的散热技术、新材料、经过高度工程化和定制化的封装,以及更精确的、与工作负载相关的模型。更糟糕的是,它们需要的验证比计划允许的要多。

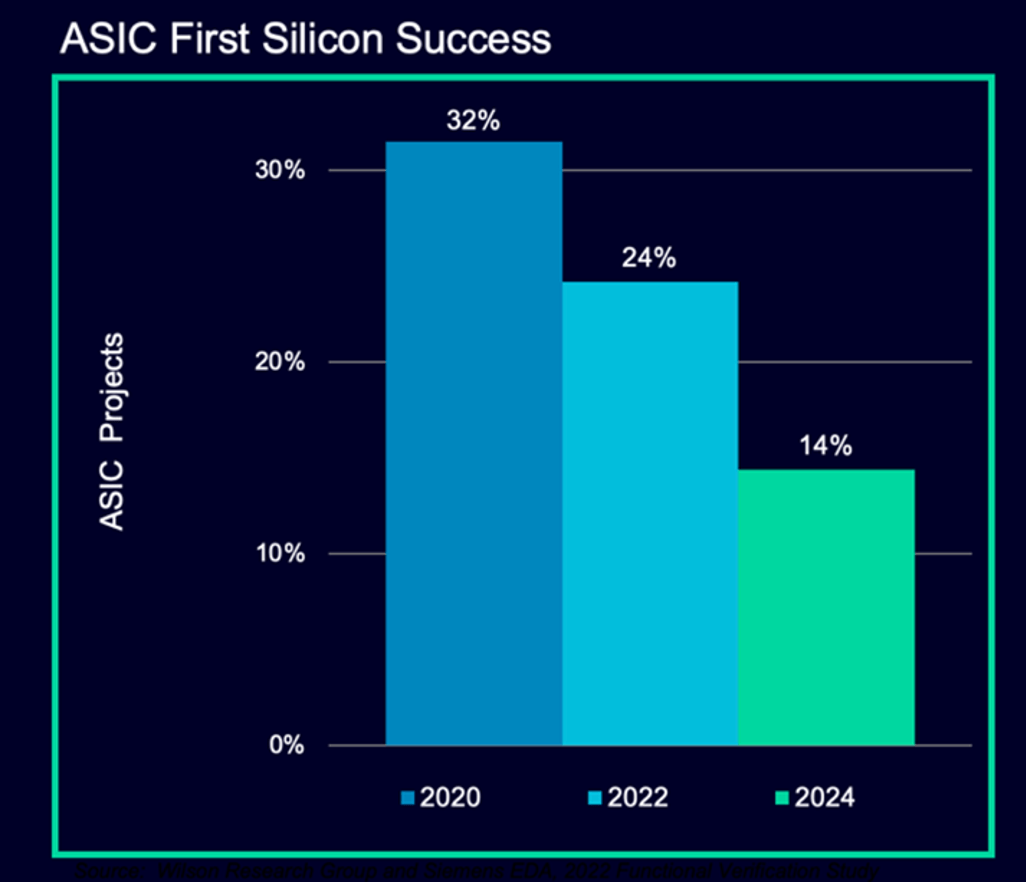

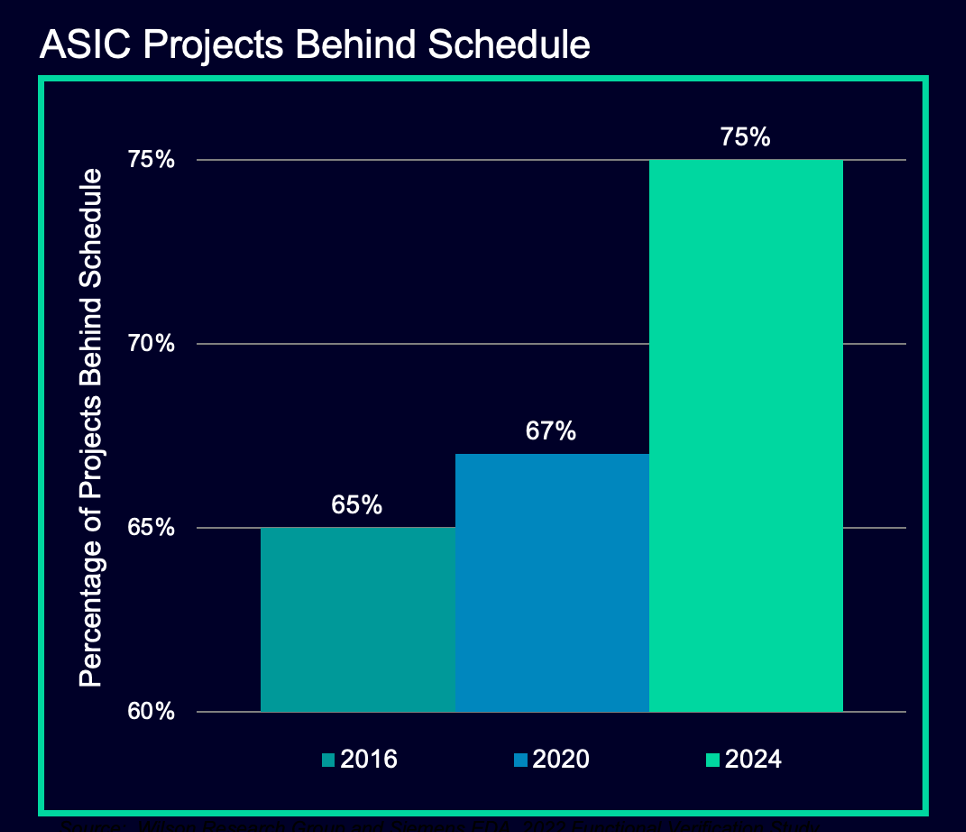

所有这些因素的综合影响在最新数据中得到了证实。西门子EDA首席验证科学家Harry Foster表示:“整个行业在实现首次流片成功方面已处于有史以来最低点。从历史上看,成功率一直在30%左右。两年前,从2023年到2024年间,这一比例下降到24%。现在下降至14%。这是一个数据点。另一个数据点是,从历史上看,我们发现大约三分之二的项目会延期,现在,项目延期的比例已经上升到75%。”

图1:功能正确且可制造的设计数量正在下降。

(图源:西门子EDA/Wilson研究小组2024年功能验证研究/DVCon)

在日益复杂和多层的设计流程中,每一步都需要提高生产效率。通常,这意味着要雇佣更多的工程师。而且现在工程师所需接受的广泛培训远远超出了过去的要求,所以这是不太现实的。这就是为什么EDA供应商如此专注于将AI融入到他们的工具中,基本上是通过强化学习来将相关知识进行编码。但这种转变仍需时间。

“我们的做法没有起到作用,”Foster表示,“我们需要大幅提高生产效率,但这并不是很多人喜欢谈论的指标,因为它很难衡量。相对容易说的是,‘这个比那个快10%’。此外,许多公司缺乏制造非常复杂芯片的技能,或者这对他们来说是新领域。在1990年代后期,每个人都在谈论生产效率差距。现在这是生产效率差距2.0版本。现在的问题与20年前不同,但也有一些共同的主题。我们需要从孤立的工具集转向更加互联和集成的工具集。”

图2:复杂度增加,加上生产效率差距,导致芯片的制造时间变慢。

(图源:西门子EDA/Wilson研究小组/DVCon)

然而,生产效率问题不能完全归咎于复杂度。即便主流芯片制造商生产芯片的速度也比过去更快。

Cadence验证软件高级集团总监Matt Graham表示。“之前我们似乎都对首次流片成功有着某种程度的担忧。但在过去的一年到一年半里,突然间每个人都在制造更多的芯片。即使是那些不以消费市场为中心的公司,比如那些为测试人员制造芯片的公司,现在对芯片数量的需求也达到了原来的四倍。他们从每18个月生产一款芯片,发展到现在每年生产四到五款芯片。这是因为一切都突然变得更加专业化了。”

这种情况经常发生在重大技术变革时期,因为此时工艺、工具和标准都需要跟上变革的步伐。“我们经常从更专业化走向更通用化,然后再回到专业化,我们似乎处于那些特定应用的周期之一,”Graham表示,“这导致每个人生产的芯片数量增加了四到五倍,但却没有人增加相应的人手来完成四倍数量的芯片流片工作。如果你处于技术前沿,拥有3D-IC或基于小芯片的设计,其中一个晶圆可能需要稍微改进一下。”

在前沿技术领域,变化深刻且繁多,有时还因设计而异,因此很难找出问题所在。很多这样的设计都是为大型系统供应商内部使用而专门定制的,这些供应商试图为特定的应用或数据类型突破性能极限。在这种情况下,重新流片的成本是预算过程的一部分,这也让相关数据变得有些模糊。

新思科技系统设计集团战略项目和系统解决方案执行总监Frank Schirrmeister表示:“对于重新流片的情况,逻辑功能仍然是最突出的问题。根据西门子EDA/Wilson研究集团的调查显示,70%的重新流片是由于规格变更而导致的设计错误。这意味着有人误解了规格要求并敲响了警钟,因此50%的设计会进行第二轮设计。一些大型芯片制造商实际上计划进行多达四次重新流片。所以归根结底,这只是复杂度的问题。”

这也为EDA公司创造了巨大的潜在机会,特别是那些将某种类型的AI融入其工具和设计流程的公司。

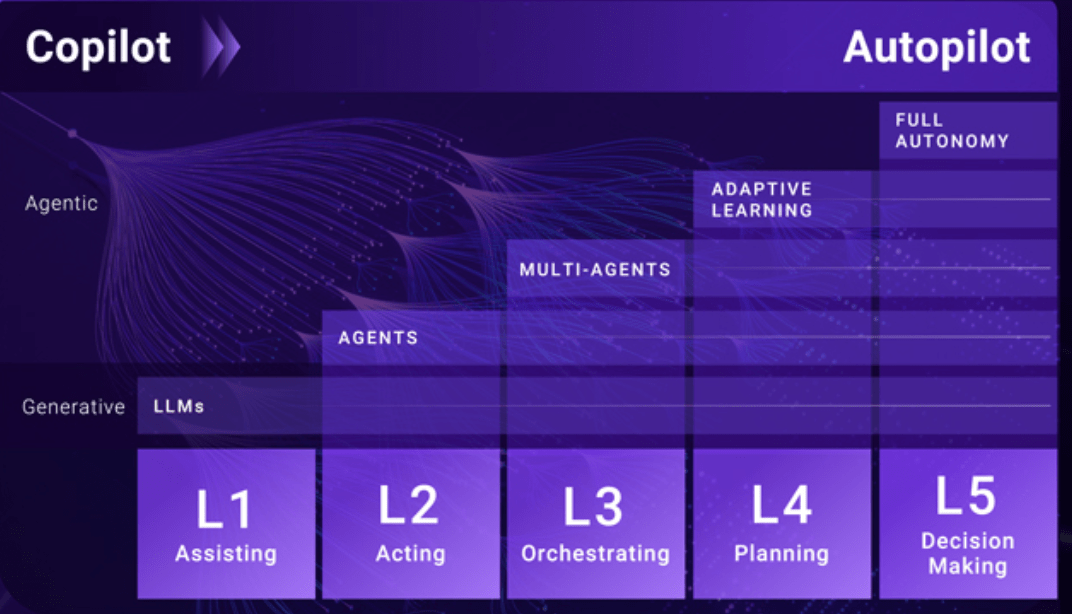

“在生成式人工智能中,你有一个‘副驾驶’来协助和创作,”新思科技首席执行官Sassine Ghazi在新思科技用户大会的主题演讲中表示。“借助我们与Microsoft合作开发的‘副驾驶’技术,你拥有了一个工作流程助手、知识助手和调试助手。你可以以更快的方式培养一名初级工程师和专家工程师。他们可以以更现代化、更有效、更高效的方式与我们的产品交互。然后就是创造性部分。我们与客户很早就展开了合作,从RTL代码生成、测试台生成到测试断言等方面,你可以拥有一个‘副驾驶’来帮助你创建RTL的一部分、测试台文档和测试断言。”

在某些情况下,生产效率已经从过去需要数天时间缩短到现在只需几分钟。但随着智能代理式人工智能的推出,最大的好处还在后面,它从根本上提高了整个设计和验证流程的抽象层次。

“随着人工智能的不断发展,工作流程也将随之改变,”Ghazi说道,“我们的利益相关者经常问我,我们何时才能看到人工智能给EDA市场带来变化。我认为,除非工作流程发生变化,否则这种情况不会发生。只有当你能够以截然不同的方式去做某些事情,从而以更快、更有效、更高效的方式交付产品时,才会看到变化。现在,在智能代理式人工智能时代,代理工程师将与人类工程师协作,以应对这种复杂性并改变工作流程。”

图3:从生成式AI到代理式AI的演变。

(图源:新思科技)

抽象问题

工程师在进行先进设计时面临的一些最大挑战在于理解设计中数百甚至数千个不同元素之间的依存关系。过去,其中一个关键的解决手段是实现硬件与软件更紧密的集成。如今的协同设计可能包括数十甚至数百个需要独立工作、有时需要协同工作的小芯片。为了理解所有可能的相互作用,需要进行多物理场模拟,而不仅仅是硬件与软件的协同设计,并且协同设计现在还包括各种类型的互连、封装、光子学,在某些情况下还包括更大规模的系统体系。

此外,所有设计都需要具备可测试性(DFT)、可制造性(DFM),并要有足够的良品率(DFY),并且还需要有足够的内部控制,以防止过热。如果运行过热且老化速度比预期的要快,则需要有重新路由信号的机制,这主要是由软件驱动的。

“在验证领域,我们看到软件正越来越多地成为完整解决方案的一部分,”Cadence的Graham说道,“这不仅仅是‘我们要制造一个芯片’。现在的芯片是特定用途的芯片。芯片的终端市场和最终应用场景是明确的。运行于芯片上的软件堆栈是已知的,机并且对于要搭载芯片的机器人、汽车或其他设备也有清晰的认识。而且我们需要从各个方面来考虑这些因素,我们需要考虑软件验证、芯片制造前的验证,甚至可能在将其放入仿真器或原型平台之前,就需要加快软件方面的工作。”

一开始,到底有多少功能应归入软件设计,又有多少应归入硬件设计,并不总是很明确。在复杂的设计中,微调这两者之间的平衡是一个耗时的过程,很容易导致多次重新设计。

“软件引入了大量的功能和特性,”Axiomise首席执行官Ashish Darbari表示,“如果硬件团队不完全了解这些功能特性,尤其是验证团队不了解的话,那么在测试内容与定义及规划的内容之间就会存在很大的差距。这正是许多错误被遗漏的原因。我们进行所有这些虚拟原型设计,并尽早启动软件测试,以获得一万或十万个模拟向量。但是,谁会关注边界条件的呢?在一个又一个项目中,我们在最初的两三周就发现所有这些错误案例问题,因为设计师已经没有时间了。”

新市场,不同的关注点

这些问题远远超出了功能验证和调试的范畴,而在芯片制造之前,功能验证和调试一直占据着芯片开发时间和资源的绝大部分。在汽车、军事/航空等安全关键型应用中采用更复杂的芯片,对设计提出了全新的要求。过去,这些市场都不允许使用先进制程的芯片,因为它们被认为不可靠。但随着来自中国比亚迪和蔚来等初创公司,以及美国Rivian和Lucid等电动汽车初创公司的竞争日益激烈,老牌汽车制造商正争相将更多功能转移到软件上。而这只有使用更先进的芯片和高度定制化的封装才能实现,并且随着汽车制造商朝着更高水平的自动化水平迈进,这将变得越来越必要。

在这些系统中,安全性是一项必备要求,但任何系统出现故障都会增加安全漏洞。因此,芯片的设计需要考虑更多极端情况,从炎热气候下的环境热量导致的加速老化,到真实道路状况等。虽然其中大部分情况可以通过模拟来测试,但芯片也需要进行道路测试。如果某些问题无法通过软件充分解决,芯片就需要重新设计。

“功能验证会耗费你大部分时间,”Axiomise的Darbari表示,“但简单的功耗优化,比如将‘无关项’(X)引入设计中,很容易使某个模块容易受到特洛伊木马的攻击,因为这些X现在在执行框架中提供了选择。所以在芯片中,一个X实际上要么是0要么是1。你实际上看不到X,但从模拟和行为的角度来看,这些X现在为终端用户增加了综合选择,使他们能够使用你不应该访问的设计区域。所以一方面,你要进行功能验证。另一方面,从功耗的角度来看,这些X问题被引入,然后就产生了冗余区域。在安全方面,芯片上的区域越大,暴露的风险就越高。”

整合各个部分

芯片内需要额外的芯片面积来容纳更多的处理元件和更多功能,或者在某些类型的先进封装中容纳多个小芯片。但这也使得首次流片的成功变得更加困难。

“你要处理的加速器具有非常复杂的工作负载,”西门子的Foster表示,“这会在设计中引入许多非确定性,我们甚至不知道如何从语义上进行描述,因此验证变得非常困难。其中一个挑战是,我们构建了许多以工具为中心的流程,而没有考虑到优化所有这些流程所需的反馈回路。未来,我们需要更多具有关联性的流程。这样我们才能利用人工智能。一个明显的例子是,当我在进行可测试性设计(DFT)时,发现‘哎呀,我无法达到故障覆盖率要求’。所以现在我需要手动返回到工具流程的早期阶段。所有这些回路都需要闭合。但你要去哪里找到做这件事的人呢?”

根据EDA公司以及一些领先的代工厂和OSAT的说法,答案在于新的工具、方法论,可能还包括更严格的设计规则和更有限的封装选择。但现在判断这一切最终会如何发展还为时过早。变化的速度比几年前任何人预测的都要快得多,而数据就是证明。

END