----追光逐电 光引未来----

【摘要】

作为第三代半导体材料 , GaN 因其高电子迁移率、 高击穿场强等优异特性 , 正被广泛应用 于高频、 高功率电子器件。 然而 , 其封装技术面临诸如热管理、 电气性能优化以及封装可靠性等挑 战 , 同时还需要满足更紧凑、 更集成的需求。 重点讨论了目前 GaN 芯片封装的多种解决方案 , 包括 晶体管外形 (TO) 封装、 四边扁平无引线 (QFN) 封装等分立器件封装结构 , 晶圆级封装 (WLP)、 多芯片模块 (MCM) 合封器件封装结构以及诸多先进封装技术。 分析了封装技术的发展趋势 , 如集 成化、 模块化封装 , 以及面向高频、 高功率应用的优化方法。 随着技术的不断突破 , GaN 封装有望 在更高效、 更可靠的方向上取得进一步进展 , 以满足不断增长的市场需求。

0 引言

GaN是一种第三代宽禁带半导体材料,凭借其高电子迁移率和高击穿电场等优越特性,在5G 通信基站、数据中心电源和消费电子快充等领域已实现规模化应用。在电动汽车领域,GaN器件凭借高频、高效优势,正逐步应用于车载充电器 (OBC)、DC-DC转换器等关键系统。例如,NavitasSemiconductor于2023年推出的GaN功率器件可将OBC效率提升至95%以上,并减少 30%的体积;特斯拉等车企也在探索 GaN 电机驱动系统的可行性[1-2] 。然而,GaN芯片的高效性能需要依靠先进的封装技术来实现,这对封装提出了更高的要求,如高功率密度散热、低寄生电感、电气隔离以及机械应力管理。常见的GaN封装技术包括倒装芯片封装、铜柱键合、多芯片集成封装和嵌入式封装等,这些技术能有效减少寄生电感,提高散热能力,确保GaN芯片在高频和高功率下的稳定性和效率[3] 。

研究GaN芯片封装技术意义重大,不仅有助于提升功率转换效率,推动 5G 通信、无线充电和新能源电动汽车等系统的发展,还能通过改进散热能力和提高可靠性来延长芯片使用寿命。此外,利用先进封装技术降低系统复杂性和成本、提高器件的集成度,有助于实现更高的系统性能,从而促进高频、高功率密度应用的普及和整个功率半导体产业链的升级。本文从GaN芯片封装原理、主流分立和合封封装技术以及先进封装技术的角度探讨了GaN芯片封装的发展趋势、关键问题和未来市场需求。

1 GaN芯片封装的基本原理

1.1 GaN材料特性

GaN材料具有禁带宽度大 (≈3.4eV,是硅的3倍)、临界击穿电场强度高 (≈3.3MV/cm,是硅的10倍)、电子饱和漂移速度快 (≈2.5×107 cm/s,是硅的 2倍)等优异特性,在高频、高功率、高温等应用场景中表现出显著优势[4-5] 。GaN在200℃结温下仍保持 >80%的电子迁移率(传统硅基器件在 150℃即失效);在高频响应上,载流子渡越时间缩短至皮秒级,支持K√ 波段 (26.5~40GHz)信号处理;单位面积导通电阻低至2 mΩ.cm2 ,允许芯片承受>1 000 V/μs 的电压斜率,使器件功率密度跃升。

与传统的硅和砷化镓相比,GaN器件能够在更高的电压和毫米波频率下工作,同时具有更低的导通损耗和更高的功率密度,这些特性使得GaN在微波通信、功率电子、军事雷达、5G 基站等领域具有广泛的应用前景。此外,先进的封装材料(如高性能导热界面材料和高温胶黏剂)也在 GaN芯片封装中发挥了重要作用,有效提升了散热性能和机械强度。

1.2 封装要求

GaN器件封装设计面临的核心挑战源于材料本征特性与系统级可靠性需求的深度耦合。从物理机制层面分析,GaN的高电子迁移率使其具备MHz级高频开关能力,但由此引发的瞬态电流变化率会通过封装寄生电感Lloop产生显著的电压尖峰, 以 JEDEC JEP180 为标准,实验结果表明,当Lloop超过0.5 nH时,栅极过压风险将导致器件寿命下降50%以上。同时,3.3MV/cm的高击穿电场强度虽支持1 200 V高压工作,却使芯片边缘电场集中效应显著,若封装介质层局部场强超过1 MV/cm,将引发不可逆的绝缘劣化。为此,现代GaN封装技术需围绕以下维度展开协同优化。

热管理层面,尽管 1.3 W/(cm.K)的热导率使GaN 显著优于硅,但在 650 V/100 A工况下,器件局部热流密度可达300 W/cm2 ,传统封装结构因热阻过高易导致结温Tj超出可靠性边界(Tj<150℃)。为此,双面散热(DSC)技术通过铜盖与直接键合铜(DBC)基板协同导热 , 可将热阻降至1.2 ℃ /W (如InfineonGaN EiceDRIVERTM模块),并提升功率循环寿命至10 万次;针对激光雷达驱动等极端热负荷场景'热导率 >2 000 W/(m.K)的CVD金刚石衬底的应用可降低60%的界面热阻'实现 500 W/cm2级的热通量承载能力。

电性能优化方面'高频特性也对封装互连提出严苛要求。一般的传统引线键合寄生电感约为2 nH'会导致开关损耗增加30%。而铜柱凸点与嵌入式封装技术如RogersCuramikTM基板的结合可将寄生电感压缩至0.05 nH'支持 4 MHz以上高频开关'同时通过微孔激光直写可缩短互连路径'使换流回路面积缩减80%、电磁干扰降低20 dB。

绝缘可靠性强化需应对高压工况下的电场集中效应。梯度介电环氧模塑料(EMC)通过介电常数梯度分布将介质层场强抑制在0.8 MV/cm以下。根据住友电木方案'经 150℃/1 000 h高温栅偏测试'绝缘电阻衰减率<5%;氟化聚酰亚胺覆层的引入有效阻断了潮湿环境下离子迁移路径'使DBC基板绝缘寿命延长至15年。

工艺—材料协同创新方面'针对GaN异质结机械脆弱性(其应变容限 <0.1%)'低温纳米银烧结技术通过纳米银颗粒表面扩散形成多孔互连层'其剪切强度达45MPa'较 SnAg焊料提升4倍'且热循环后界面分层率<0.5%;以IEC 60749-25 为标准'硅胶弹性体应力缓冲结构的同步集成可吸收90%以上的热失配形变'使焊点疲劳寿命突破 5 万次'为高密度封装提供可靠机械支撑。

综上所述'封装技术在微电子器件和车规级功率器件中的应用'不仅需要满足高功率密度、低寄生参数、高绝缘能力等性能要求'还需通过先进的封装工艺和严格的可靠性评估'确保器件在复杂工况下的长期稳定运行。随着第三代半导体材料的广泛应用'GaN 封装技术将继续朝着高集成度、高可靠性和高性能的方向发展。

2 主流GaN封装技术

2.1 分立器件

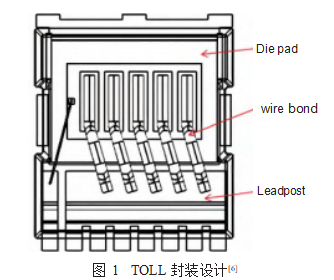

晶体管外形(TO)封装作为一种经典的分立器件封装形式'广泛应用于功率半导体器件中'使功率MOSFET、绝缘栅双极型晶体管(IGBT)和 GaNHEMT等器件表现出优异的电气和热性能。近年来'随着功率器件向高功率密度、高频率和高可靠性方向发展'TO封装的设计和优化成为了研究热点。SIM等[6]提出了一种创新的晶体管外形无引线(TOLL)封装'如图 1所示'通过缩短引线长度和优化引线框架设计'显著降低了封装电阻'提升了电流承载能力'并在汽车应用中展示出优异的性能。TOLL封装的设计不仅提高了功率密度'还通过引入“侵入式模具边缘”专利技术'进一步增强了生产过程中的处理能力。然而'TO封装在高温环境下的可靠性问题仍然存在'尤其是在热机械应力导致的焊料疲劳方面'仍需进一步优化与改进。

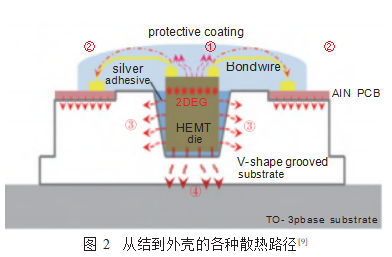

对于GaNHEMT器件'TO封装的热管理问题尤为突出。JORDA等[7]分析了GaNHEMT在TO-247 封装中的自然对流冷却方案'指出TO封装的热阻主要来自封装内部的导热路径'尤其是焊料层和基板之间的热传导。SONG等[8]进一步研究了GaNHEMT在TO封装中的功率循环测试'发现焊料层的热疲劳是导致器件失效的主要原因'尤其是在高温循环条件下'焊料层的热机械应力导致热阻增加'进而影响器件的可靠性。CHOU等[9]提出了一种基于TO-3P 封装的GaNHEMT横向散热设计'通过V型槽铜基板增强了器件的散热能力'从结到外壳的各种散热路径如图2 所示'实验结果表明'该设计能够有效降低器件的热阻'提升功率密度。

在封装材料的选择上'陈泽亮[10]指出TO-220FL 封装中使用的黏片材料和塑封料对器件的散热性能有显著影响。ANSYS仿真和实验验证结果表明'高导热率的银浆和塑封料能够显著降低器件的热阻,提升器件的电流承载能力。这一发现为TO封装的材料选择提供了重要的参考依据。

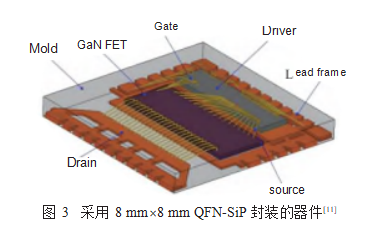

四边扁平无引线(QFN)封装因其低电感、高散热性能和紧凑的尺寸,逐渐成为 GaNHEMT器件封装的主流选择。QFN封装通过其无引线设计,减少了寄生电感,特别适合高频和高功率应用。CHEN等[11]通过系统级协同设计,成功将 600 VGaNFET与集成驱动器封装在32引脚QFN-系统级封装 (SiP)中,尺寸为8 mm×8 mm,展示了QFN封装在高功率密度和高效率应用中的潜力,如图 3所示。研究表明,通过优化封装和PCB布局,可以显著降低寄生电感,从而提升器件的开关性能和可靠性。

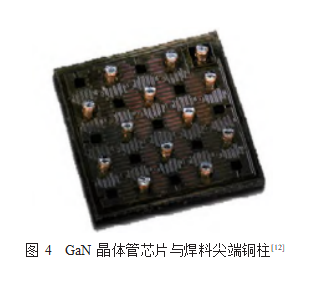

在QFN封装中,热管理是一个重要的挑战。GaN HEMT器件在高功率条件下工作时会产生大量热量,若不能有效散热 , 器件性能将下降甚至失效。LONGFORD等[12]指出,QFN封装通过暴露的散热焊盘能够有效传导热量,尤其是在高功率应用中,QFN 封装的DSC设计可以显著降低器件的热阻;通过使用铜柱(CuP)凸点技术和倒装芯片工艺,可以进一步优化QFN封装的热性能,减少热阻并提高器件的可靠性,GaN晶体管芯片与焊料尖端铜柱如图4 所示。

此外,QFN及同类封装在射频器件中的应用也取得了显著进展。陈家乐[13]通过ANSYS仿真和实验验证,展示了双边扁平无引线(DFN)封装在 GaN基射频器件中的优异散热性能。他们的研究结果表明,DFN封装通过优化引线键合和散热设计,能够有效降低器件的结温,从而提高其崩溃电压和开关稳定性。特别是在高频应用中,DFN封装的低寄生电感和高散热性能使其成为GaN射频器件的理想选择。

李祥生等[14]研究了封装对600 VGaNHEMT开关特性的影响,发现封装中的寄生电感(如 Ls、Lg、Ld)对器件性能有显著影响,尤其是Ls会将主功率电流耦合至驱动电路,增加开关损耗。对于高速 GaN器件,封装寄生电感的影响比传统CMOS更为显著。实验结果表明,TO-220 封装的GaN器件在10 A以上的高电流时漏极电压会出现振荡,导致应力超标,这是因为在TO-220 封装中,较大的寄生电感 (如 7 nH)与GaN HEMT的高速开关特性相互作用,电感与器件电容如Coss形成谐振回路,导致开关瞬态中的电压振铃。TO-220 封装下,在电流大于 10 A 时,漏极电压振荡至747 V,远超额定值600 V,直接引发应力超标。而PQFN封装则无此问题,PQFN封装通过低寄生电感(如 2 nH)和优化布局,显著抑制了谐振与尖峰,从而避免了电压超限问题,且能有效降低开关损耗。具体而言,PQFN封装可将CMOS的开关损耗减少8.4%,将GaN器件的开关损耗减少19.3%。此外,高速GaN 器件功率处理能力强且芯片面积小,要求封装不仅具有低寄生电感,还要有良好的散热能力。因此,未来高速器件封装的发展方向将聚焦于低电感、DSC以及集成封装等技术,以满足GaN 器件在高性能应用中的需求。

TO封装和QFN封装是GaN芯片中常用的2种封装技术,各自有其优缺点。TO封装因其较大的体积和引脚结构,能够提供良好的热管理和电气性能,特别适用于高功率、大电流应用,具有较强的散热能力和较低的接触电阻,因此在功率电子领域应用广泛。然而,TO封装的尺寸较大,可能不适合空间受限的小型化应用,且在高频领域可能引入较高的寄生电感和电容,限制了其高频性能。相对而言,QFN封装采用无引脚设计,提供更高的空间利用率,适用于高密度组装和小型化设备,特别在高频和射频应用中表现优异,能够有效降低寄生电感和电容,改善高频特性。此外,QFN封装的散热性能在低功率应用中较为突出,但在高功率和大电流条件下,其散热能力不及TO封装,QFN封装的散热路径高度依赖底部裸露焊盘与PCB铜层的热耦合,然而其有限的热传导面积 (通常仅为数平方毫米)导致单位面积热密度较高,加剧了芯片结温的积累,从而需要额外的散热设计,例如通过高导热基板如热导率为170~200 W/(m.K)的氮化铝陶瓷、嵌入式散热片或强制风冷等设计来补偿其固有热管理短板,以满足高功率场景的可靠性需求。综上,TO封装适合于高功率、高电流和恶劣环境下的应用,而QFN封装则更适合于高频、紧凑和低成本的设计需求,应根据具体应用的功率需求、空间限制和电气特性来决定选择哪种封装技术。

2.2 合封器件

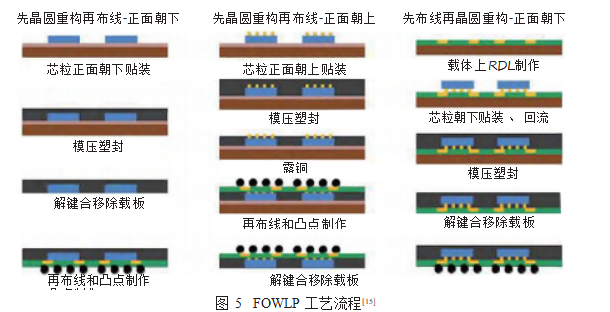

近年来,扇出型晶圆级封装 (FOWLP)技术因其在异构集成和热管理方面的优势,逐渐成为GaN器件封装的主流选择之一。其基本结构是将切割后的裸芯片重新排列在临时载板上,通过 EMC包封形成重构晶圆,在其表面利用光刻和电镀工艺制作多层重新布线层 (RDL),扩展 I/O接口,并植入焊球实现无基板的高密度互连封装。FOWLP工艺流程大致分为晶圆重构再布线和先布线再晶圆重构2种,如图5所示。

封装设计对热阻的影响尤为显著。YU等[16]研究了不同封装配置下GaN器件的热阻表现,发现将GaN器件的硅衬底研磨并采用银烧结技术将其背面与DBC基板连接,通过顶部冷却和背面冷却的方式,可以将GaN器件的热阻从15℃/W降低至4.5℃/W。这种改进主要得益于DBC基板的高热导率和银烧结技术的优异热传导性能。此外,作者通过有限元仿真(FEM) 验证了DBC基板在热管理中的优势:DBC基板的热阻显著低于传统的PCB基板,尤其是在高功率密度应用中表现出更好的散热性能。

KAKOU等[17]通过多尺度热仿真分析了FOWLP 封装中GaN功率放大器的热行为,发现多层PCB相较于单层PCB在热管理上具有显著优势,能够将最大结温降低25℃ 。通过将导通电阻Rds_on作为温度敏感参数(TSEP)可以实现 GaN器件的热阻测试:邱金朋等[18]通过实验验证了Rds_on与结温之间的相关性,并提出了基于 Rds_on的热阻测试方法,该方法适用于不同电压等级和封装形式的GaN器件;PASCAL等[19]通过在线 S 参数测量验证了 GaNHEMT的Rds_on作为TSEP 的有效性,其温度依赖性与散射参数(如S11频移)的关联性可实现动态结温反演,误差范围与内置传感器一致,且无须额外硬件;DONG等[20]的电热联合仿真结果表明,SiCMOSFET的Rds_on正温度系数(PTC)可抑制并联模块的电流失衡,结合热阻差异建模后,电流不均衡度从2.61 A降至1.31 A,最大温差由10℃优化至4.67℃ ,间接反映热阻分布特性。然而,该方法准确性受器件参数分散性、热耦合效应及测量带宽限制,需通过参数校准、三维热阻抗建模等协同设计提升稳健性。综上,Rds_on的温度敏感性为热阻评估提供了理论和实验基础,但其工程化还需兼顾器件特性与系统级优化。此外,KAKOU等[21]还通过瞬态热仿真研究了FOWLP封装中GaN器件的热响应时间,发现器件可在0.8 s内达到稳态温度,进一步验证了FOWLP封装在热管理中的高效性。

多芯片模块(MCM)封装技术广泛应用于功率电子器件,尤其是 GaN功率器件。基于层压有机基板、陶瓷基板或薄膜基板集成多工艺裸芯,通过引线键合/倒装焊与基板内多层布线实现互连,并由金属/陶瓷/塑料封装外壳提供保护与散热功能,MCM封装通过将多个芯片集成在同一基板上,能够有效减少寄生电感、提高热管理效率,并提升系统的功率密度和可靠性。

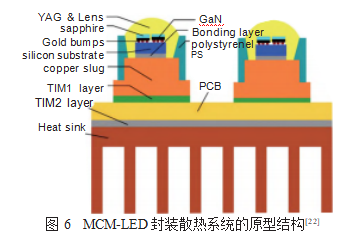

PAN等[22]通过研究多芯片模块高功率LED (MCM-LED)封装的热管理,提出了基于热阻网络的 热分析模型, 并 通 过FEM 验证了其有效性。MCM-LED封装散热系统的原型结构如图6 所示。研究表明'MCM封装结构的总热阻为6.53 K/W'结温为77.2℃ '仿真与理论计算结果基本一致。此外'作者通过正交实验设计优化了封装结构参数'发现焊球直径对热性能的影响最显著。这一研究为GaN器件的MCM封装提供了重要的热管理参考。

KODOROVA等[23]提出了一种新型的GaN多芯片功率微模块(GaNMPM)封装方案'GaNMPM封装的三维模型如图7 所示'该方案将GaNHEMT芯片、Si栅极驱动器和无源元件集成在AlNDBC基板上'并通过金属基板实现散热。通过FEM'发现该封装方案的结到环境热阻为43K/W'比传统的PCB封装方案降低了42%。AlN陶瓷基板的高导热性和优化的封装结构使GaNMPM在高密度DC-DC转换器中能够有效提升功率密度和可靠性。

严鼎等[24]从驱动电路设计的角度提出了一种GaN功率器件的预驱动芯片'并通过多芯片合封技术将预驱动芯片与GaN功率器件集成在同一封装中。这种集成封装方案显著降低了寄生电感'提升了GaN器件在高频工作环境下的开关性能。实验结果表明'集成封装后的GaN器件在400V电压下的开关速度达到133V/ns'且未出现误开启现象'满足了高频系统的要求。

FOWLP和MCM封装技术在GaN器件封装中各具特色。FOWLP将芯片嵌入封装体并利用RDL实现电气连接'能够显著减小封装尺寸'提高集成密度'同时具备优异的热管理性能'尤其是在多层PCB结构中'能够有效降低结温并实现快速热响应。MCM封装则通过将多个芯片集成在同一基板上'减少寄生电感'提升热管理效率和系统功率密度'特别适用于高功率密度和多芯片协同工作的场景'如高功率LED和DC-DC转换器。总体而言'FOWLP更适合高集成密度和快速热响应的应用'而MCM则在高功率和多芯片集成领域表现更优'需根据应用需求进行选择。

3 先进封装技术

3.1 电气性能优化

3.1.1 低寄生电感封装

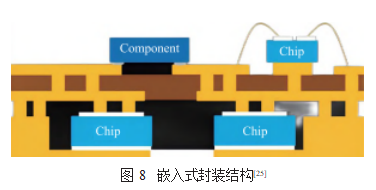

低寄生电感设计的核心在于电磁场能量分布重构。根据麦克斯韦方程组'电感本质是导体周围磁场能量储存能力的表征。传统引线键合的弧形结构会形成闭合电流环路'其自感量与环路面积正相关。LI等[25]提出了一种基于板级嵌入式封装技术的GaN模块'嵌入式封装结构如图8 所示'通过将 GaN芯片直接嵌入到基板中'使电流路径缩短至毫米级'较传统引线(5~8 mm)减少 60%以上'电感量呈对数关系下降'减少了传统引线键合带来的寄生电感'并显著降低了热阻'结到周围环境的热阻为 17.1℃/W'结到 PCB的热阻为8.95℃/W。

此外'胡涛[26]基于GaNFET的窄脉冲激光驱动设计'采用板上芯片封装 (COB)技术'通过缩短键合线和优化放电环路布局'显著降低了寄生电感'实现了上升时间为2.01 ns、脉宽为4.05 ns的高性能激光脉冲输出。COB键合线优化采用扁平铜带代替圆形引线'通过增大表面积将趋肤深度的有效利用率提升3倍以上。

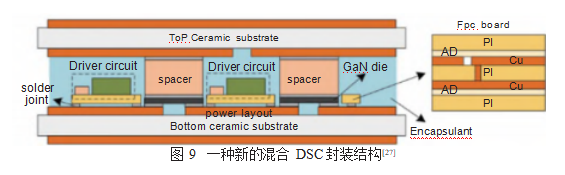

传统的单面冷却 (SSC)封装技术虽然简单'但在高频开关应用中'其热性能和寄生电感限制了GaN器件的性能表现。DSC技术通过将器件夹在2 个陶瓷基板之间'显著提高了散热性能'并降低了功率回路的寄生电感。然而,传统的DSC封装在多芯片并联时,GaN器件的横向结构使功率和栅极布局难以同时对称,导致电流分配不均。为此,LI等[27]提出了一种新型混合DSC封装技术,其封装结构如图 9 所示,通过引入柔性印刷电路板(FPC)实现了功率和栅极布局的分离与优化,显著提升了多芯片 GaN模块的电流均衡能力和开关速度。该封装结构不仅实现了低至0.65 nH 的功率回路电感和1.33 nH的栅极回路电感,还在实验中验证了器件在高达—29.3A/ns和204V/ns的开关速度下仍能保持电流均衡。此外,该封装技术通过DSC设计,将结温升降低了 51.3% ,显著提升了模块的热性能。相比之下 ,传统的SSC封装和DBC/PCB混合封装在多芯片并联时难以实现对称布局,且热性能较差。因此,在多芯片并联中,混合DSC封装技术为GaN器件的高功率应用提供了新的解决方案。

3.1.2 高频互连技术

先进封装技术的高频互连技术通过低损耗材料(如低介电常数和低介质损耗因子基板)、精细化布线(RDL/TSV)及三维互连结构(如倒装焊/ 硅中介层),结合阻抗匹配与电磁屏蔽设计,实现 GHz以上信号的高效、低损耗传输,支撑 5G 通信、高性能计算及毫米波雷达等高频应用场景。

张宗烽[28]研究了异质集成工艺下的互连结构,重点分析了去嵌技术、信号传输特性及宽带电路模型构建。通过对比THRU-L 与L-2L 去嵌方法的精确度,验证了其在微波毫米波频段 (0.1~50 GHz)下的准确性,并探讨了衬底损耗和结构尺寸对传输性能的影响,确保了高速射频信号传输的完整性。此外,研究构建了宽带等效电路模型,通过仿真与测试数据对比,验证了模型的高精度,为硅基异质III-V族化合物集成下的互连技术提供了快速评估方法。

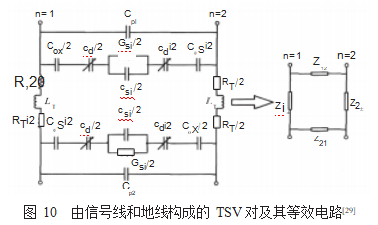

在TSV技术的实际应用中,材料的电—热—力耦合特性对封装可靠性有重要影响。王晓鹏[29]在其研究中详细分析了TSV和GaN场效应管在多物理场耦合下的电—热—力特性,其中由信号线和地线构成的 TSV对及其等效电路如图10 所示,TSV的等效电路参数提取对电路性能研究至关重要,尤其是在周期性电磁脉冲(EMP)注入的情况下,TSV的电—热—力耦合响应会严重影响集成电路的可靠性。

3.2 热管理结构创新

3.2.1 高效散热结构

在GaN器件中,高效散热结构通过三维堆叠导热材料、嵌入式微通道及高导热界面材料如石墨烯、液态金属,结合主动散热设计,实现高功率密度芯片的热量快速传导与均匀耗散,确保系统在高性能计算、5G 等场景下的稳定运行。

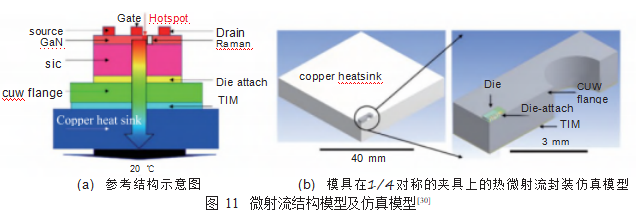

ZHANG等[30]提出了一种基于3D打印的微射流冷却技术,用于高功率GaN晶体管的封装级热管理,微射流结构模型及仿真模型如图11 所示,该技术通过微射流阵列直接冷却晶体管背面,显著降低了热阻,相比传统封装,热阻减少了约 60%。这种技术特别适用于高功率密度的金刚石基GaN器件,能够有效解决器件背面的高热流密度问题。

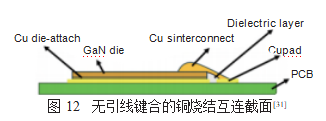

AIN等[31]介绍了无引线键合的铜烧结互连技术,设计的截面如图12 所示。该技术采用印刷铜烧结膏替代传统的铝线键合,减少了寄生电感和热阻,适用于GaN功率器件的精细封装。实验结果表明,尽管铜烧结互连的电导率较低,但其在高功率应用中的热管理性能优于传统引线键合技术。HONG等[32]研究了倒装芯片封装技术在GaNHEMT中的应用,通过在器件顶部引入金属散热层和优化的凸点设计,显著降低了器件的工作温度,相比传统的面朝上封装,温度上升减少了44%~46%。这种倒装芯片设计不仅提高了热管理效率,还减少了寄生电感,适用于高功率和高频率的应用场景。

自然对流冷却技术在GaNHEMT的热管理中展现了其简单性和高效性。JORDA等[7]通过对比不同的自然对流冷却方案,发现使用散热片的方案能够将结到环境的热阻从44.8 K/W 降低到11.8 K/W,显著提升了器件的散热性能。强制对流冷却可以将热阻进一步降低至5.1 K/W,但这会增加系统的复杂性和成本。

3.2.2 先进散热材料

陶瓷基板嵌入式封装技术是一种结合了低电感和高散热能力的先进封装方案,特别适用于高频、高功率的GaNHEMT应用。该技术通过将GaN芯片嵌入高导热率的AlN陶瓷基板中,利用直接镀铜(DPC)技术实现低电感互连。马创伟[33]指出陶瓷基板嵌入式封装的功率回路电感可低至2.86 nH,节壳热阻为0.236℃/W,较有机基板嵌入式封装分别减少了8%和50%。此外,陶瓷基板嵌入式封装通过优化 PCB布局和去耦电容的“I”型结构,进一步降低了功率回路的寄生电感。

KE等[34]指出低温烧结纳米铜材料因其优异的导电性和导热性,是第三代半导体封装互连材料的重要发展方向。通过优化纳米铜颗粒的尺寸、形貌和表面处理工艺,研究人员成功实现了低温烧结,显著提升了封装互连的导电性能和剪切强度,为高功率器件的封装提供了新的解决方案。

3.3 集成化封装

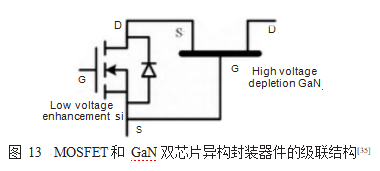

在功率器件的封装中,异质封装结构被广泛应用。MOSFET和GaN双芯片异构封装器件的级联结构如图13所示,MOSFET和GaN器件通常分别作为低压侧和高压侧器件,通过共源共栅(Cascode)结构实现高效控制[35] 。FOPLP技术通过EMC介质层上的RDL和激光钻孔实现垂直导通,使器件的体积和Rds_on显著减小,从而提高了器件的集成度和散热性能。

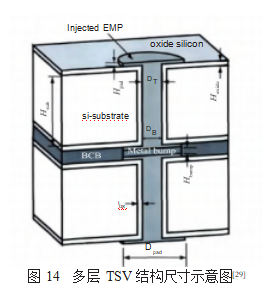

三维集成电路(3D-IC)技术通过垂直堆叠多层芯片的架构创新,突破了传统平面集成的物理限制,利用TSV技术实现芯片间亚微米级垂直互连,将互连长度缩短至数十微米量级,显著降低了信号传输延迟与动态功耗[29] 。图14为多层TSV结构尺寸示意图,TSV 工艺通过深硅刻蚀、绝缘层沉积和铜填充等关键步骤,在硅基板内形成直径为 5~50μm的高密度导电通道,不仅实现了芯片堆叠层间的直接电气连接,更创新地将TSV阵列作为三维热传导路径,利用铜等高导热材料构建贯穿芯片的热通道,结合微凸块与热界面材料,可将芯片结温降低15~20℃ , 同时通过优化TSV布局实现热应力均匀分布。该技术已成功应用于高带宽存储器 (HBM)与 GPU的异构集成,在将带宽提升至TB/s 级的同时解决了3D堆叠架构下的“热障”难题,为人工智能加速器、5G 毫米波射频模块等高性能场景提供了兼具高算力与高可靠性的封装解决方案。

3.4 应力优化设计

应力优化是通过梯度CTE复合介质材料、聚酰亚胺柔性衬底及纳米级应力缓冲层的系统集成,结合TSV阵列拓扑优化设计与低温固晶键合工艺,基于热—机械耦合效应调控,实现热膨胀系数失配诱导的界面分层失效机制的系统性抑制,并通过热应力梯度分布重构保障3D异构集成封装体系在宽温域 (—55~125℃)循环载荷下的结构完整性,为高密度柔性电子及量子芯片封装提供跨尺度的可靠性解决方案。

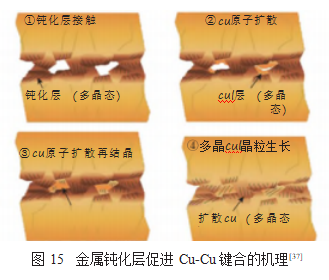

铜线键合技术作为新一代键合材料,因其优异的导电性和导热性,逐渐取代传统的铝线和金线,成为功率器件封装中的主流选择。铜线键合在IGBT模块中的应用能够显著提高电流传输能力和散热性能,尤其是在大电流和高功率密度场景下表现出色[36] 。通过优化超声功率、键合压力和键合时间等工艺参数,铜线键合能够有效提高键合点的剪切强度,减少键合失效的风险。此外,Cu-Cu直接键合技术在3D 封装中的应用也显示出其独特的优势。Cu-Cu键合不仅能够实现μm级的精密互连,还能在高电流密度下保持稳定的电学性能,成为替代传统Sn基钎料凸点互连的理想方案[37] 。通过表面活化处理(SAB)和自组装分子层(SAM)技术,纳米铜烧结过程依赖表面等离子体共振效应:当铜颗粒尺寸小于电子平均自由程 (~40 nm)时,局域表面等离子体共振(LSPR)在 532 nm激光激发下产生热点,局部温度 >800℃ ,促使颗粒表面氧化层CuO发生还原反应,金属钝化层促进 Cu-Cu键合的机理如图15所示。这种光—热—化学耦合机制实现了低温200℃以下的致密化烧结,孔隙率<5%。Cu-Cu键合可以在较低的温度下实现高强度的键合,显著提高了封装的可靠性和性能。

4 结東语

作为代表性的第三代宽禁带半导体,凭借其大禁带宽度、高击穿场强等特性,GaN器件在功率密度与频率性能上显著超越硅基器件,可实现2~10 MHz高频工作,而硅基 IGBT仅为200 kHz~1 MHz。然而,其产业化进程受封装技术制约,市场渗透率不足5%,面临的核心挑战体现在以下3方面:高频特性导致寄生电感敏感度较硅基器件高1 个量级,每 0.5 nH寄生电感即可产生20%损耗;热流密度达 300 W/cm2(Si基仅为50 W/cm2),与封装衬底的热膨胀系数失配更显著;硅基GaN异质集成工艺难度高,限制三维封装的发展。

当前技术突破集中于低寄生封装、高效散热及三维集成。栅极脆弱性与传统封装工艺兼容性矛盾、封装成本占比高等问题亟待解决。其未来发展方向呈现3大趋势:异构集成、智能热管理、低成本材料革新。随 着12英寸晶圆级封装良率突破95%,GaN有望在消费快充、数据中心电源等领域加速替代硅基器件,开启高频、高功率电子新时代。

GaN封装技术的进步正推动GaN器件在高频、高功率和高集成化场景中的应用。未来,通过寄生电感控制、散热设计优化及异构集成技术创新,GaN器件在5G 通信、汽车电子和光伏储能领域的应用前景可期。

*参考文献(上下滑动可查看):

作者简介:

宋海涛 (2002—),男 ,江苏盐城人,硕士研究生,主要研究方向为面向CMOS应用的GaN器件。

申明:感谢原创作者的辛勤付出。本号转载的文章均会在文中注明,若遇到版权问题请联系我们处理。

----与智者为伍 为创新赋能----

联系邮箱:uestcwxd@126.com

QQ:493826566