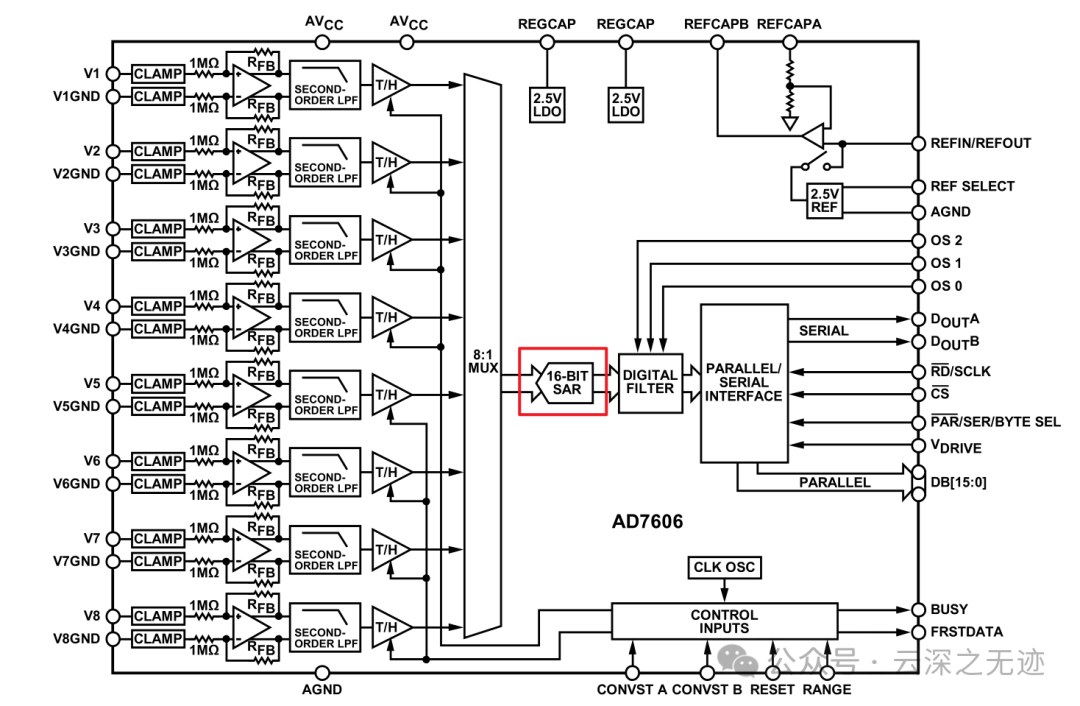

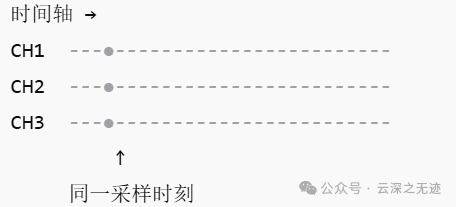

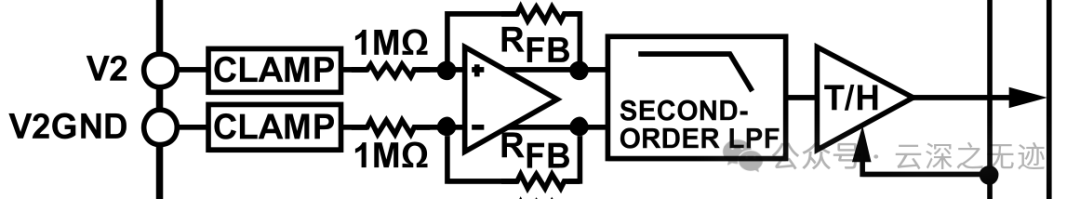

为什么是标题这样的,因为是不是真真正正意义上面的同步:AD7606 内部每个模拟通道都配有一个 Track-and-Hold(T/H)放大器,可以先“跟踪”模拟输入信号,并在采样瞬间“保持”这个值等待 ADC 转换。所有通道在同一时刻由 CONVST 引脚启动,T/H 同时进入 hold 状态,然后再由 ADC 顺序转换。- 所有通道的 T/H 同时在 “track” 模式中跟踪输入。

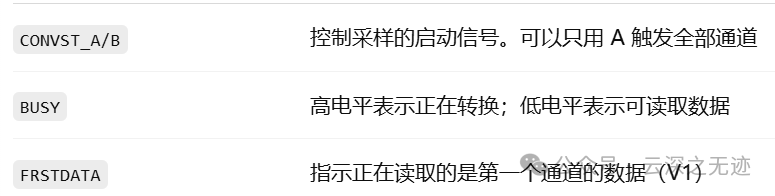

- 主控 MCU / FPGA 拉高 CONVST_A

- 所有通道的 T/H 在 同一时刻锁定当前输入电压。

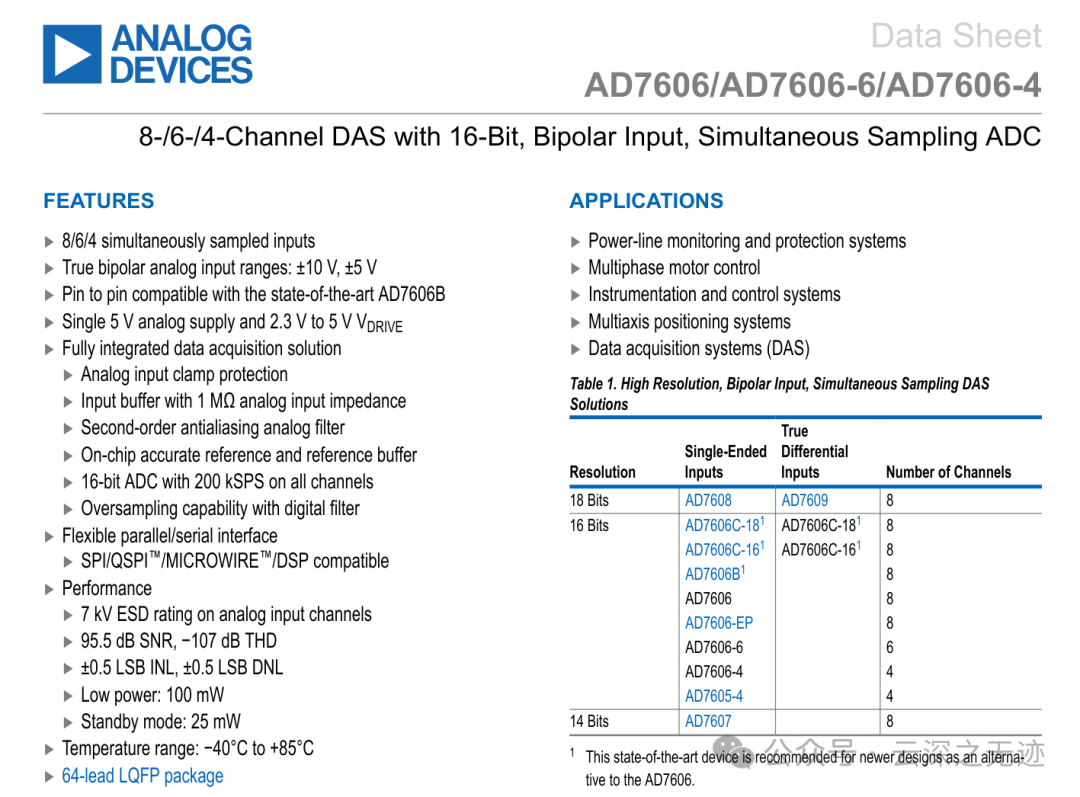

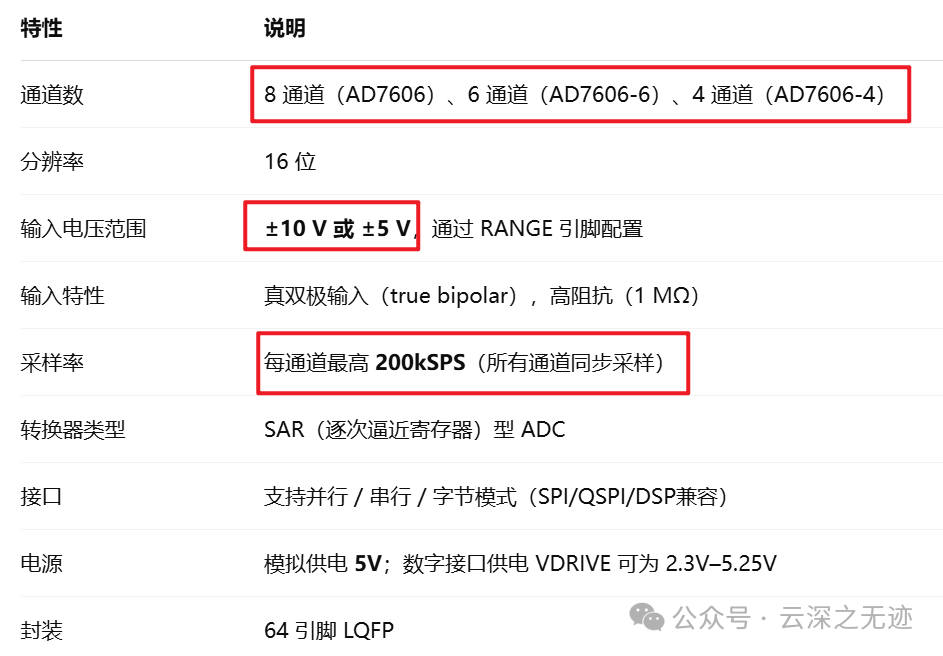

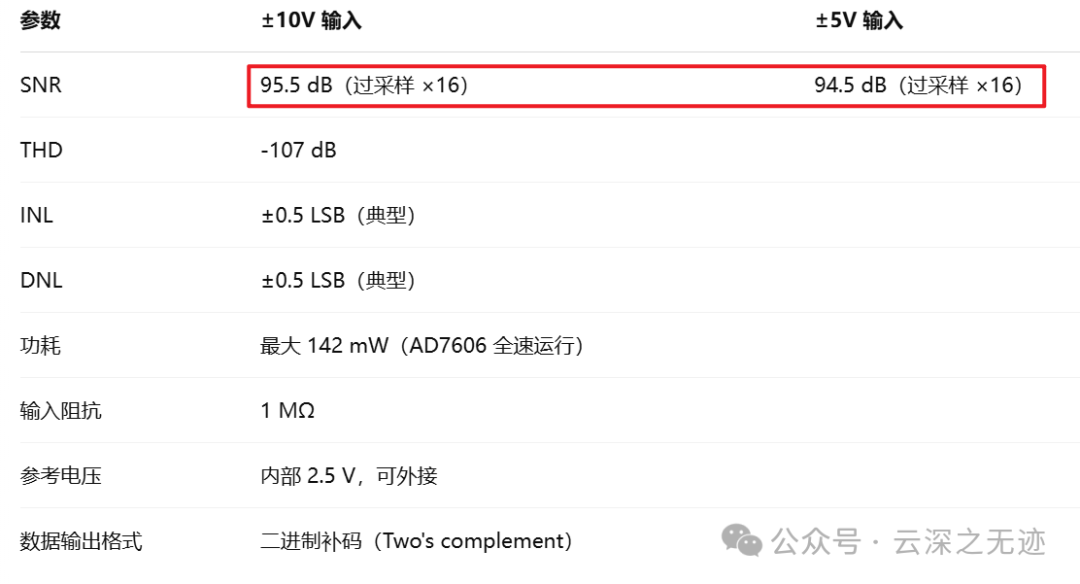

事实上这个芯片卖了这么多年,经久不衰就是因为特别的全面:数据格式:二进制补码(Two's Complement)- MCU/FPGA 拉高 CONVST_A 启动采样

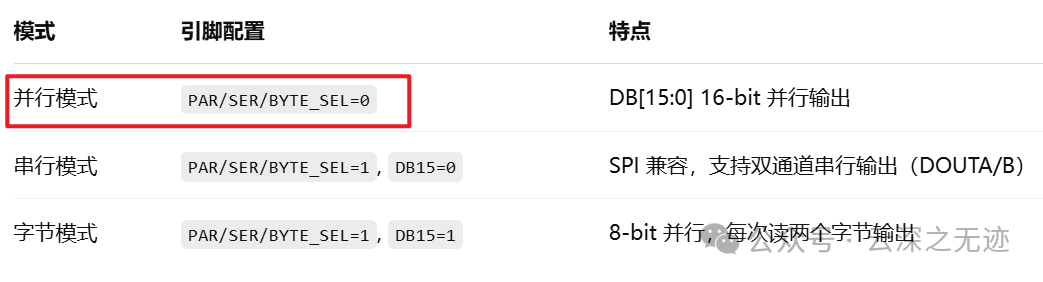

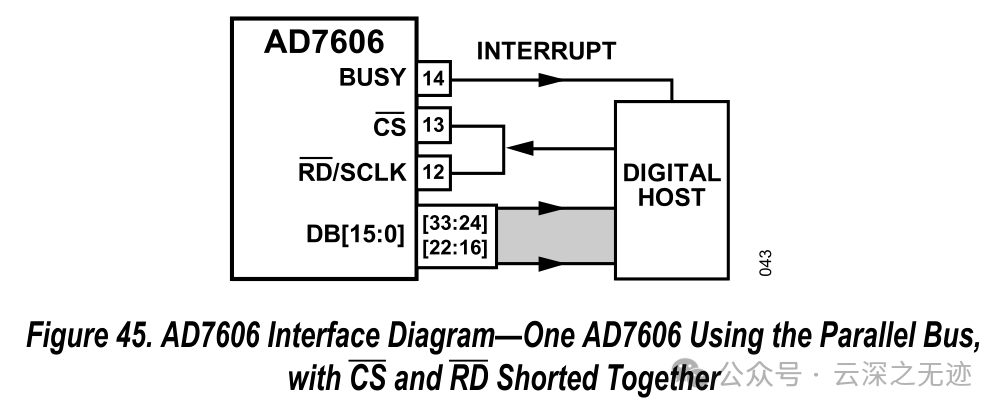

- 每次从 DB15:DB0 输出一个通道的 16bit 数据

- 第一通道(V1)输出时 FRSTDATA = 高,标记为起始

⚠️ 所有数据必须在下一次 CONVST 上升沿前读完,否则会被覆盖。

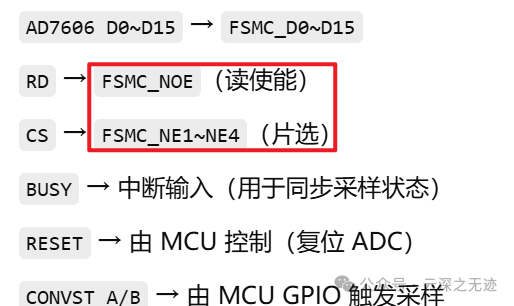

FSMC 是一个灵活的静态内存控制器,支持下列类型的存储器或并行接口设备:

最大 FSMC 时钟频率:60 MHz

支持 16位数据总线,适配 AD7606 并行输出接口

使用非复用异步 SRAM 模式(Non-multiplexed Asynchronous SRAM)ADC “行为上像 SRAM 的设备”,它拥有类似 SRAM 的并行访问结构:

地址线 + 数据线 + 读写控制引脚,可以被 FSMC 当作外部静态内存一样“读写”。虽然这个外设不一定真的是存储器,但它的时序协议与静态 RAM 兼容或类似,因此可以使用 FSMC 的 SRAM 模式 驱动它。https://www.analog.com/en/products/ad7606.html