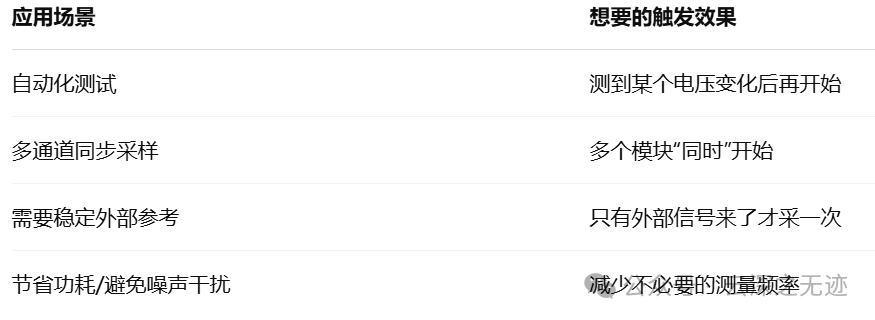

用外部 MCU(或按键)输出一个上升沿脉冲;

连接到每个模块的 CTRL 脚;

设置 TRIG:SOUR EXT;

所有模块将在收到这一个脉冲后同时采样一次,保证时间同步。

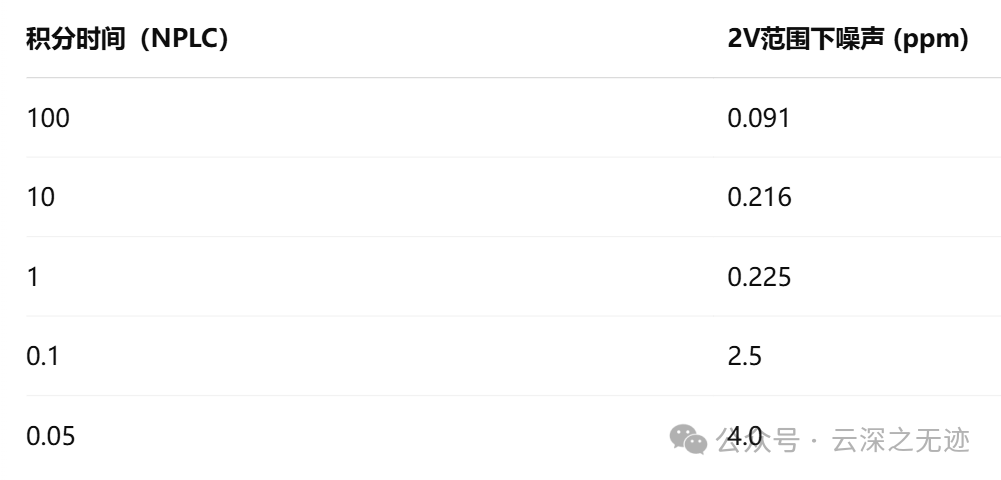

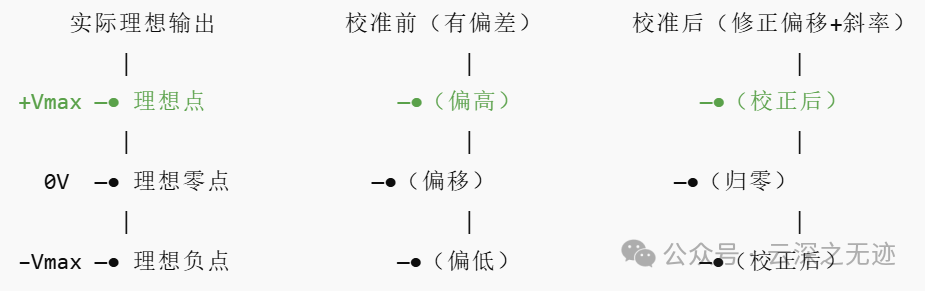

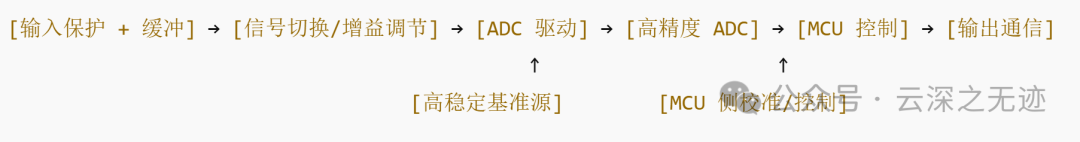

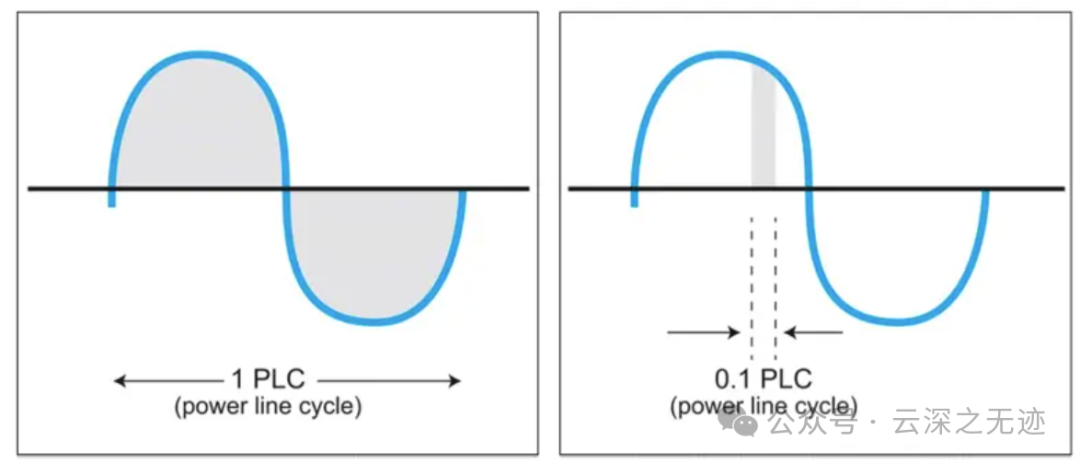

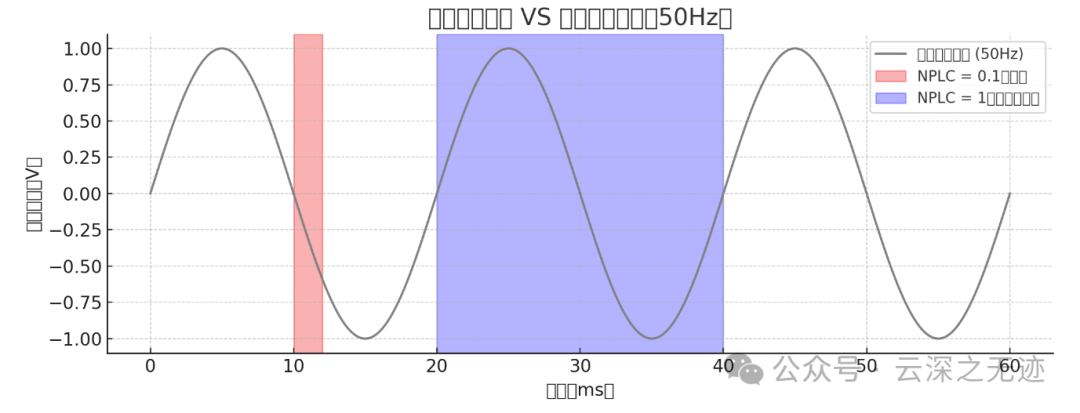

一种基于积分原理的抗干扰采样策略,本质目的是:

用 ADC 的采样积分窗口覆盖一个或多个完整的电源周期,让电源频率干扰积分为零,从而大大抑制 50Hz/60Hz 工频干扰对精密测量的影响。

这 20 次采样分布在一个完整的“嗡嗡震荡”中(50Hz 工频干扰),所以正负干扰互相抵消,最终读数更纯净。

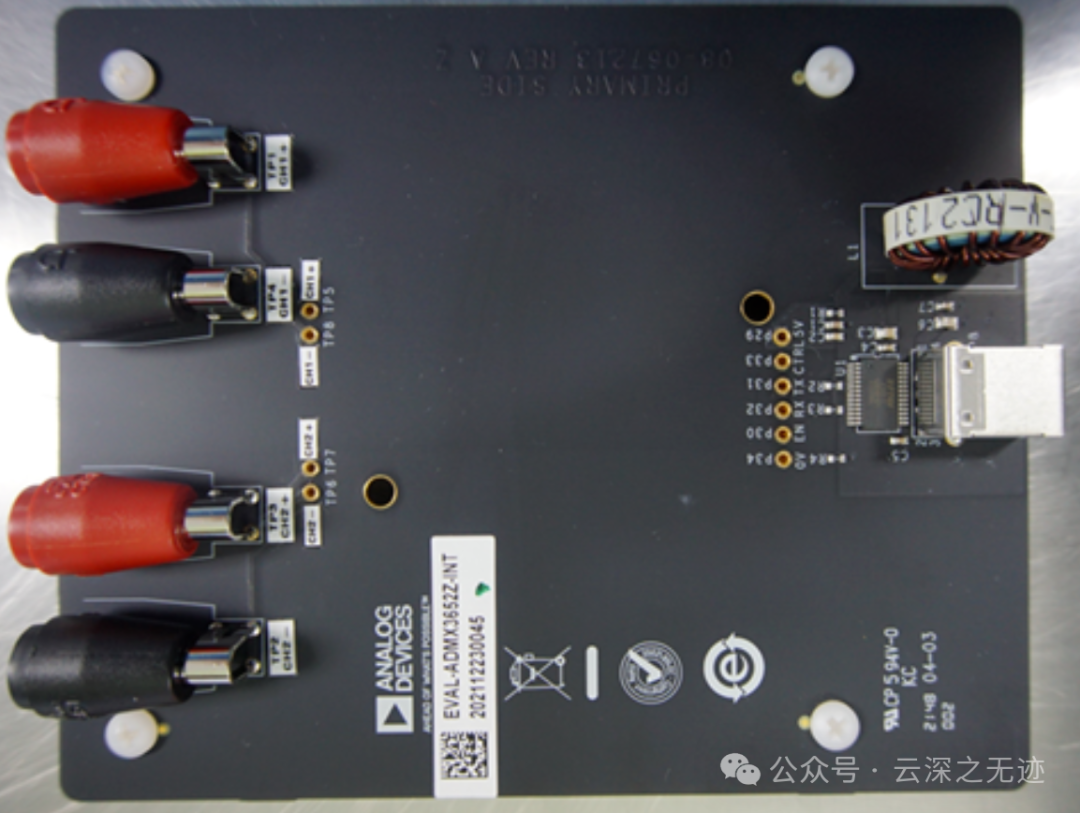

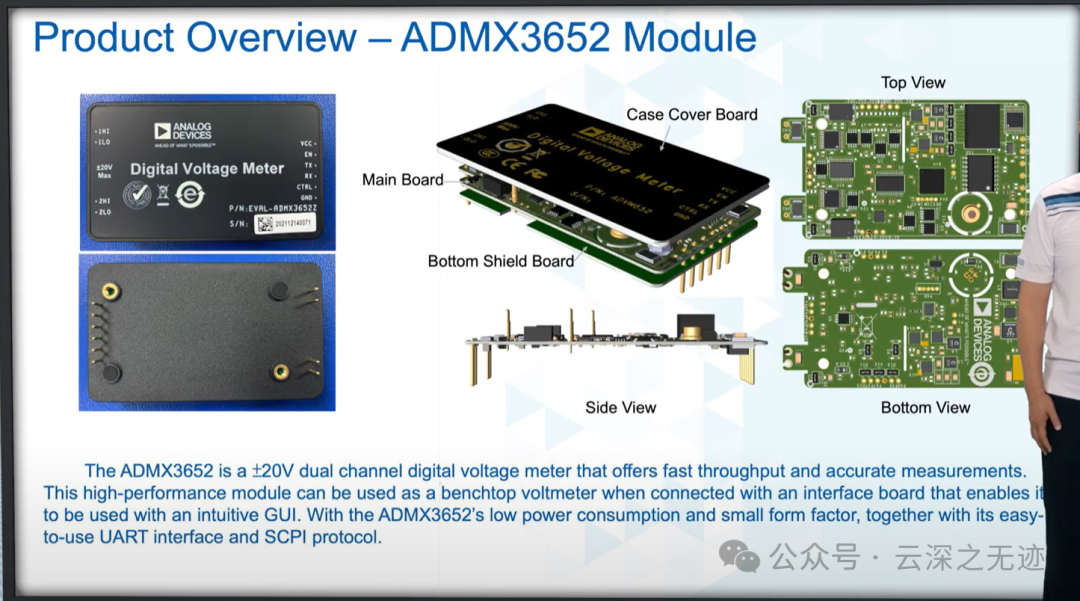

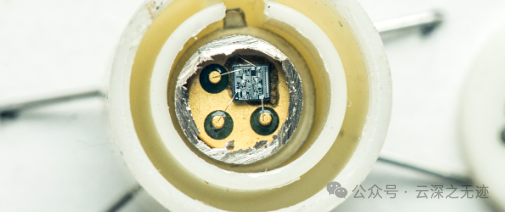

因为之前没有看到这个拆解图,我自己做了一些可能的器件的工作,也放了。

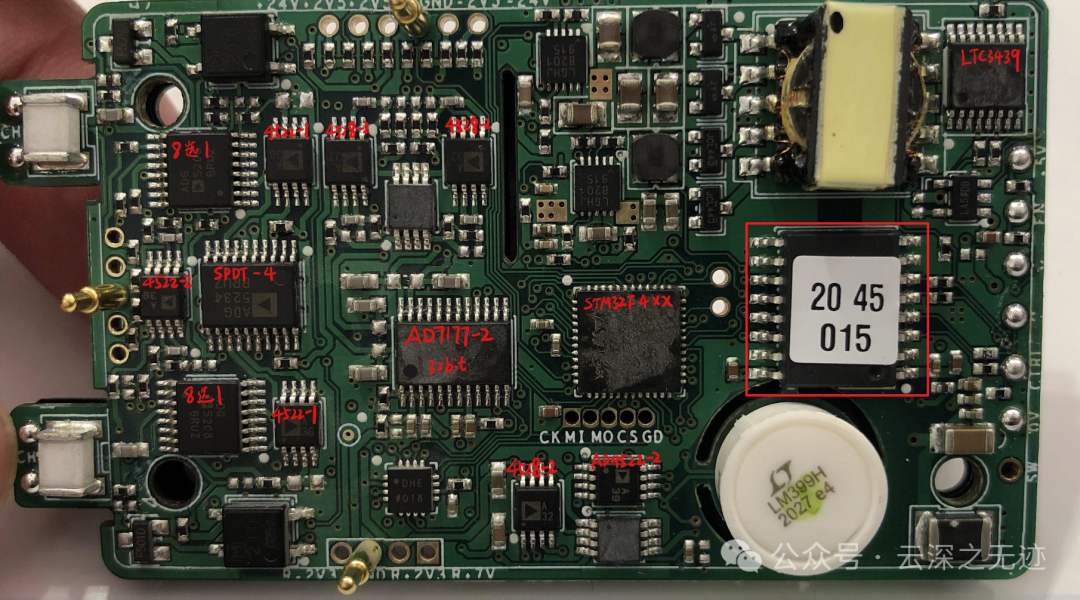

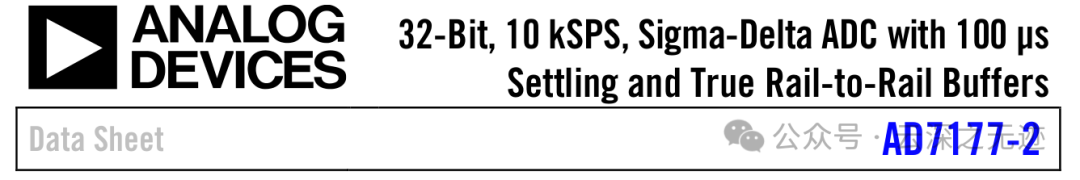

ADA4625-1:超低噪声、低偏置、精密 JFET 输入放大器

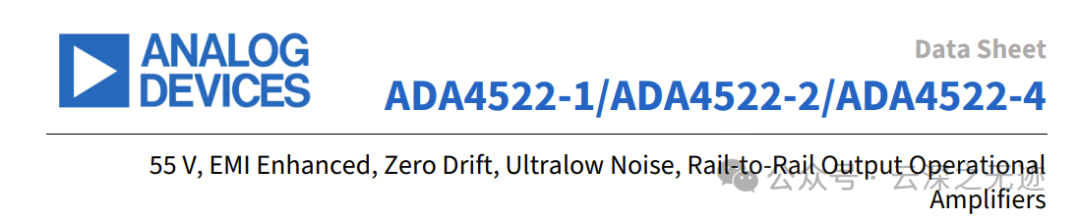

ADA4522-1/2:低偏移电压、零漂移、轨到轨输入输出

ADA4096-2:内建输入保护的精密放大器(带 ±40V 保护)

AD8250/AD8253:高速、低噪声的可编程增益仪表放大器(PGA)

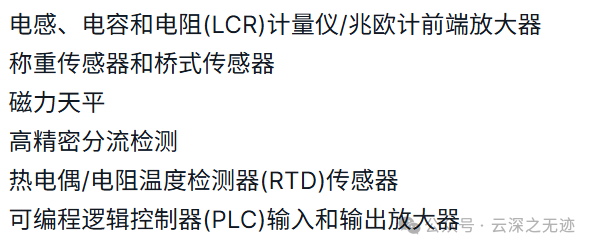

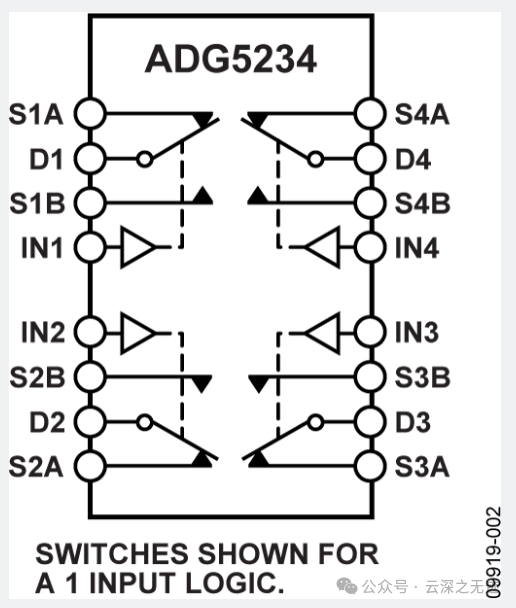

ADG series(开关/多路复用器):如 ADG704/ADG734 实现增益电阻切换

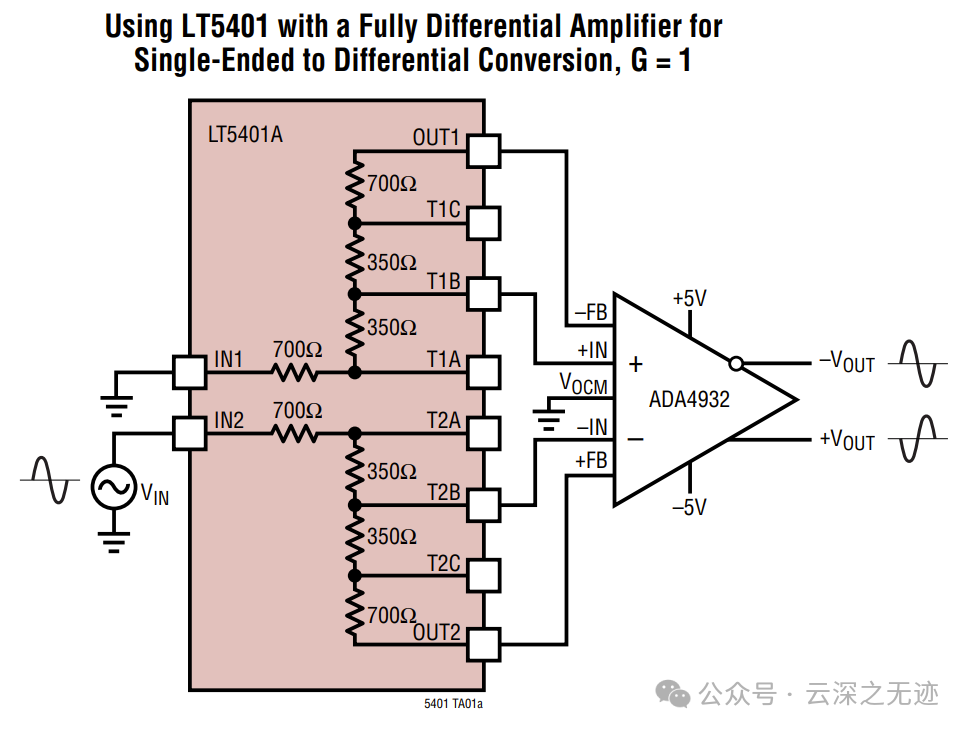

ADA4945-1:高精度、低失真差分ADC驱动器

ADA4940-1:适合低压供电的高性能驱动器

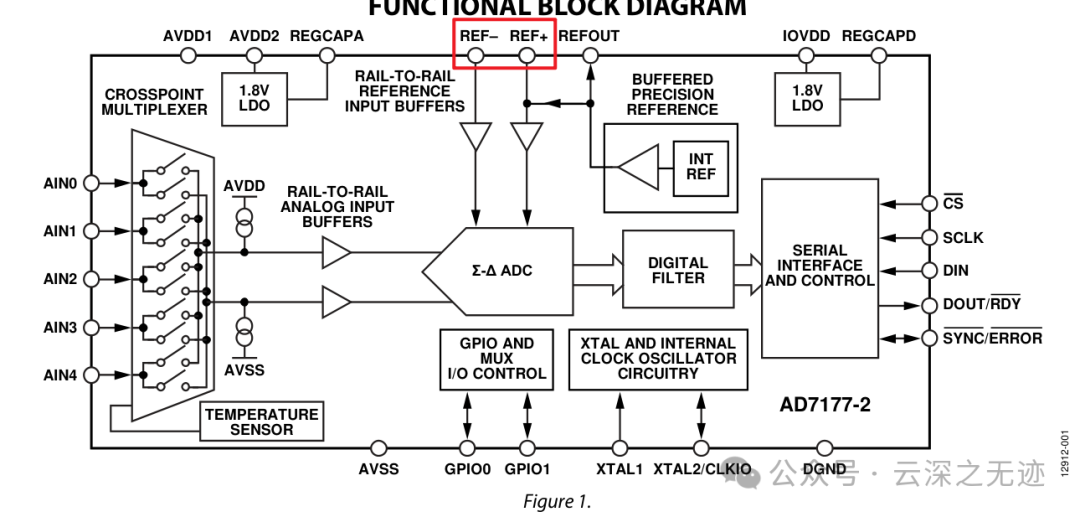

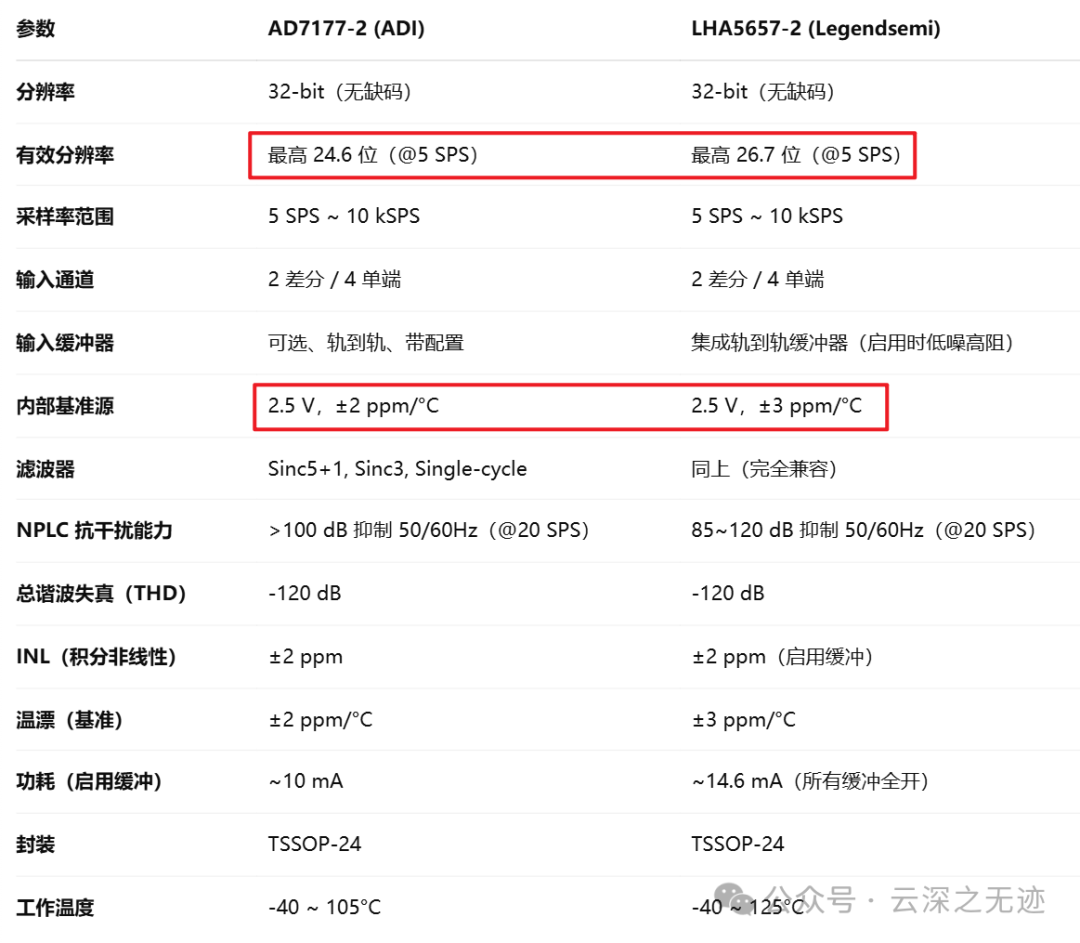

AD7177-2:24 位、低噪声、双通道、最大 10 kSPS,支持 ±10V 输入范围

AD7124-4/AD7124-8:超高分辨率、多通道精密 ADC,集成 PGA 与滤波器

AD7768-1(可能性较低,因该芯片面向更高采样率)

ADuCM4050 或类似 Cortex-M 系列微控制器(ADI自有MCU)

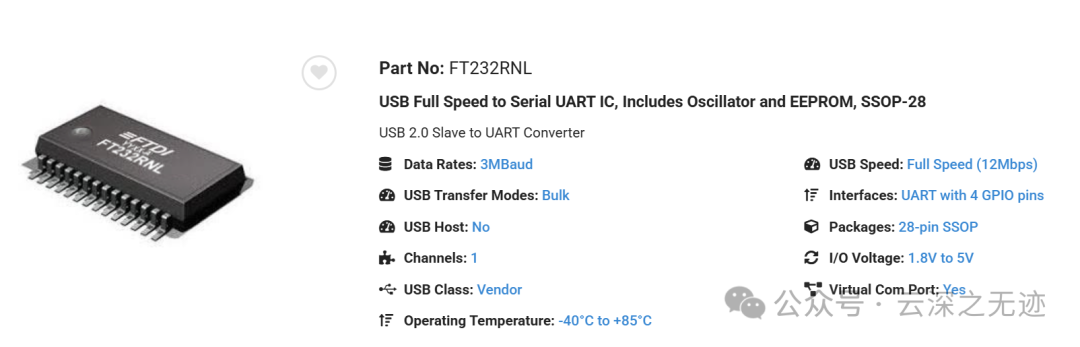

FTDI FT232RL:用于 UART → USB 转换(确认出现在 GUI 驱动中)

ADP7142/ADP7118:超低噪声 LDO,适合给模拟部分供电

# 重新导入库并生成图像import matplotlib.pyplot as pltimport numpy as np# 时间轴t = np.linspace(0, 60e-3, 1000) # 0 ~ 60 ms# 工频干扰信号(50Hz)f = 50 # Hzpower_line_noise = np.sin(2 * np.pi * f * t)# 三种积分窗口(NPLC = 0.1, 1)nplc_0_1_start, nplc_0_1_end = 10e-3, 12e-3 # 2ms windownplc_1_start, nplc_1_end = 20e-3, 40e-3 # 20ms windowfig, ax = plt.subplots(figsize=(10, 4))ax.plot(t * 1000, power_line_noise, label='工频干扰信号 (50Hz)', color='gray')# 填充积分区域ax.axvspan(nplc_0_1_start * 1000, nplc_0_1_end * 1000, color='red', alpha=0.3, label='NPLC = 0.1(短)')ax.axvspan(nplc_1_start * 1000, nplc_1_end * 1000, color='blue', alpha=0.3, label='NPLC = 1(完整周期)')ax.set_title("积分时间窗口 VS 工频干扰信号(50Hz)")ax.set_xlabel("时间(ms)")ax.set_ylabel("干扰电压(V)")ax.grid(True)ax.legend(loc='upper right')plt.tight_layout()plt_path = "/mnt/data/NPLC_vs_PowerLineNoise.png"plt.savefig(plt_path)plt_path

https://www.armbbs.cn/forum.php?mod=viewthread&tid=127097https://enlitechnology.com/blog/accurate-pv-testing-smu/