----追光逐电 光引未来----

01

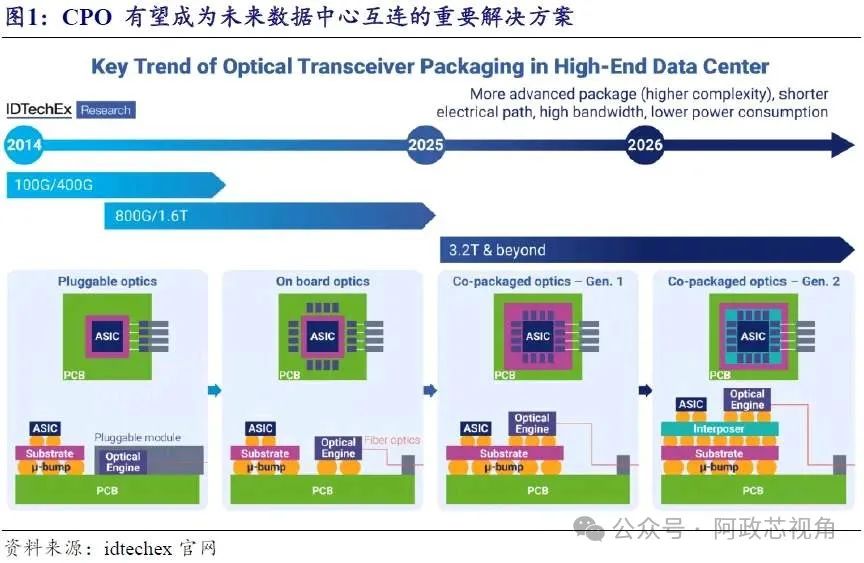

CPO在人工智能应用中的加速落地

在摩尔定律效应逐渐放缓的背景下,人工智能集群的性能提升正从晶体管优化转向通信效率优化。共封装光学(CPO)技术通过高度集成,显著提高了数据传输的带宽和距离,同时降低了延迟,为解决AI集群扩展中的通信瓶颈提供了关键支持。美满电子和台积电近期的技术发布标志着CPO在人工智能应用中的加速落地,行业对高效通信解决方案的需求正在推动这一技术的快速普及,成为未来人工智能基础设施发展的重要方向。

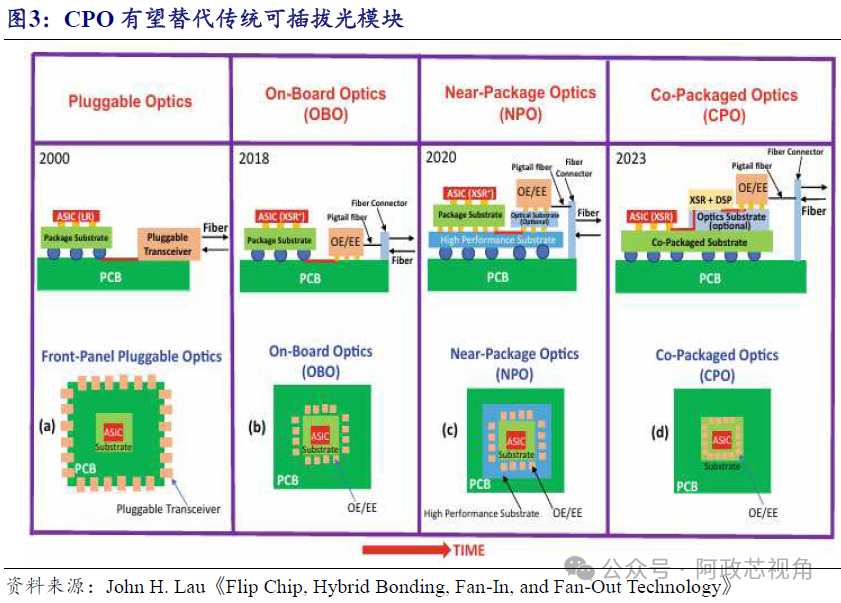

光电共封装(Co-Packaged Optics,CPO)是一种新型的光电子集成技术。光电共封装基于先进封装技术将光收发模块和控制运算的专用集成电路(ASIC)芯片异构集成在一个封装体内,形成具有一定功能的微系统。

光电共封装技术进一步缩短了光信号输入和运算单元之间的电学互连长度,在提高光模块和 ASIC 芯片之间的互连密度的同时实现了更低的功耗,是解决未来大数据运算处理中海量数据高速传输问题的重要技术途径。

02

CPO/OIO 深度拆解:更高集成度的下一代高速通信解决方案

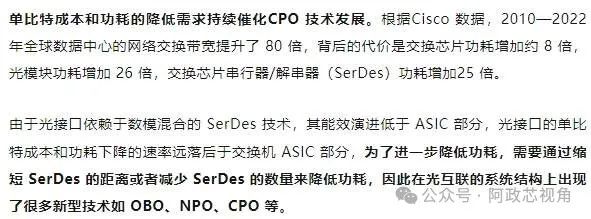

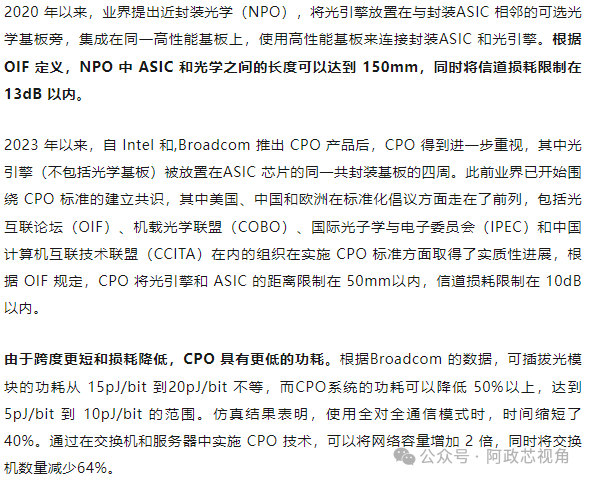

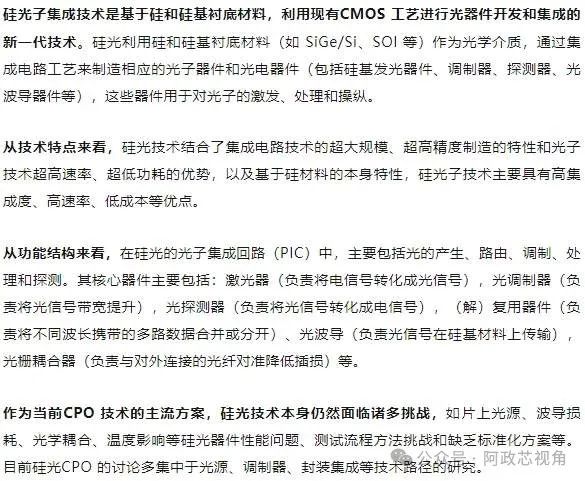

硅光基于硅和硅基衬底材料,通过CMOS工艺进行光器件开发和集成,在高速光模块领域可带来低成本、低功耗等优势,同时也能缓解EML短缺现状,硅光模块份额或加速提高。LPO由于其兼具可插拔性与低功耗优势,预计成为25-26年高速光模块的快速落地方案。CPO&OIO作为更高集成度的下一代高速通信解决方案,台积电、高通等厂商亦积极布局,台积电预计其交换机CPO平台26年成熟。

CPO或带动硅光光引擎、CW 光源、光纤、FAU、MPO/MTP 等需求增长

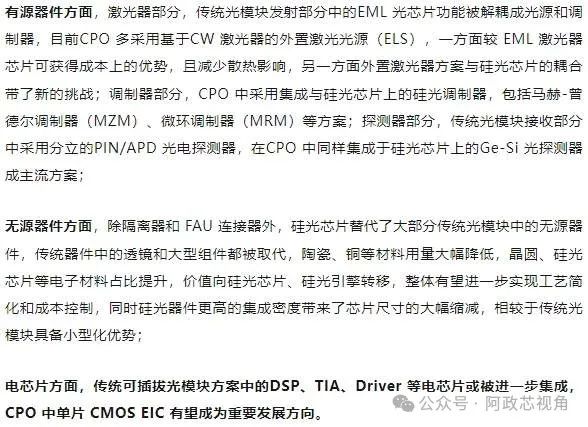

CPO 方案通过将光引擎与交换芯片近距离互连,相较于传统可插拔方案具有高带宽、低延时、低功耗、小尺寸等优点,同时利用基于硅光的光引擎,CPO 使用经过验证的半导体制造技术和设计工艺实现了高水平的光学和电气设备集成,有望实现规模化生产、可靠性提高和成本的降低。

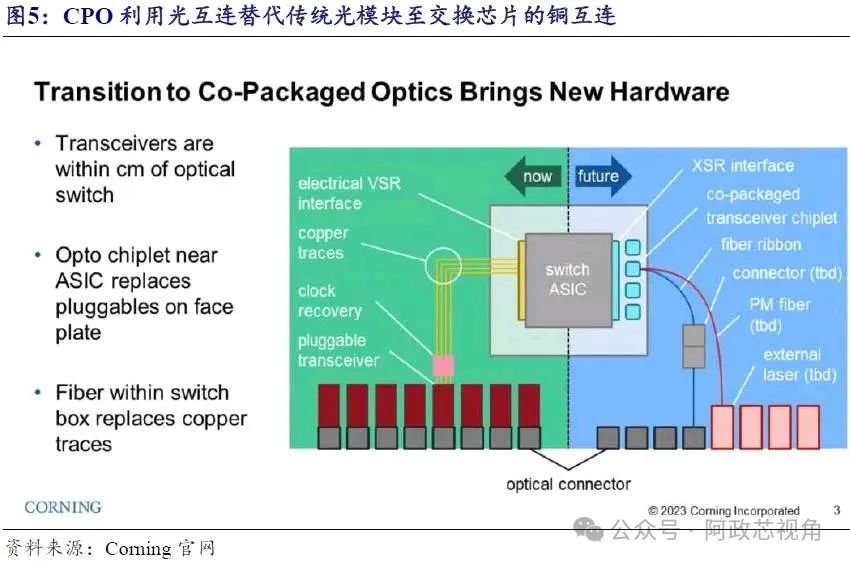

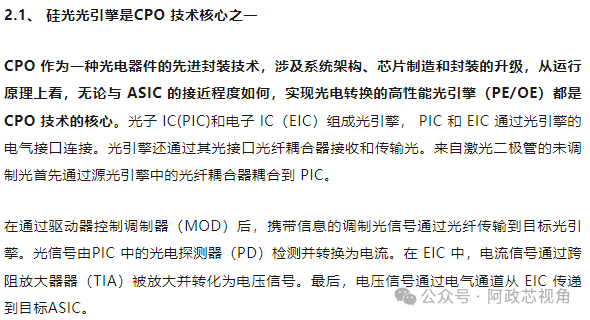

从器件构成上来看,相较于采用分立式器件的传统可插拔光模块,主流CPO 方案中由于硅光光引擎的引入,除激光器外,大部分已实现了多种光电器件的硅基集成:

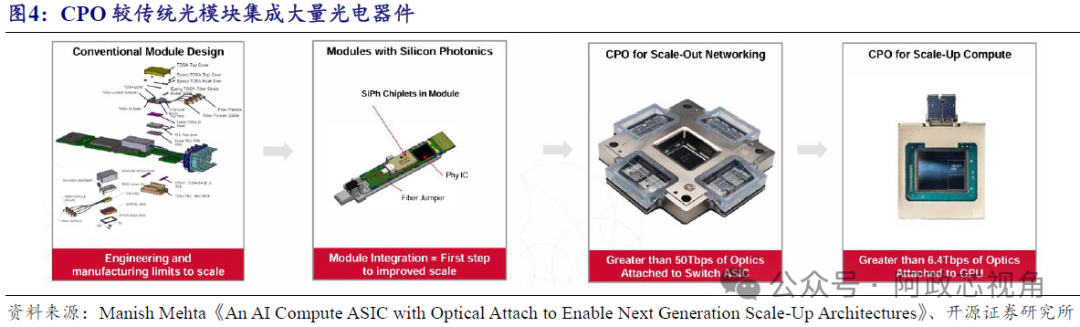

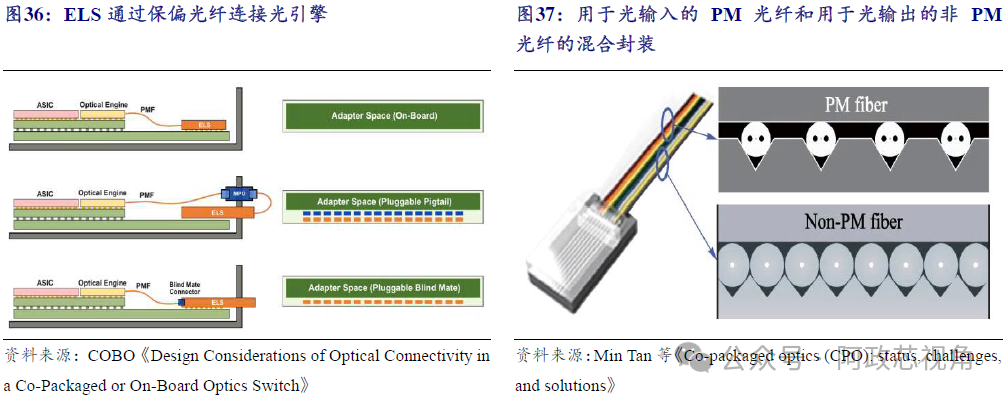

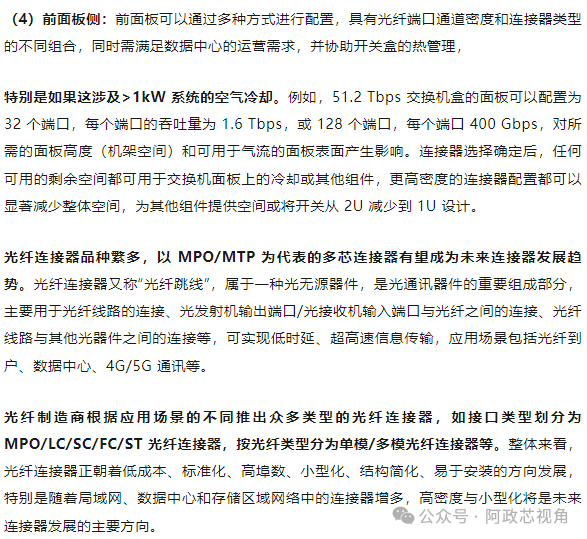

从互连架构来看,在电气连接上,通过引入更适合短距离场景 XSR SerDes,实现对电气接口的优化;在连接零部件上,CPO 相较于传统可插拔方案光互连取代铜互连,因此在交换机内部引入额外的光纤及光纤连接器,主要包括 ELS-光引擎段、光引擎-前面板段,同时前面板原光模块的电气接口转为光互连的光纤连接器。

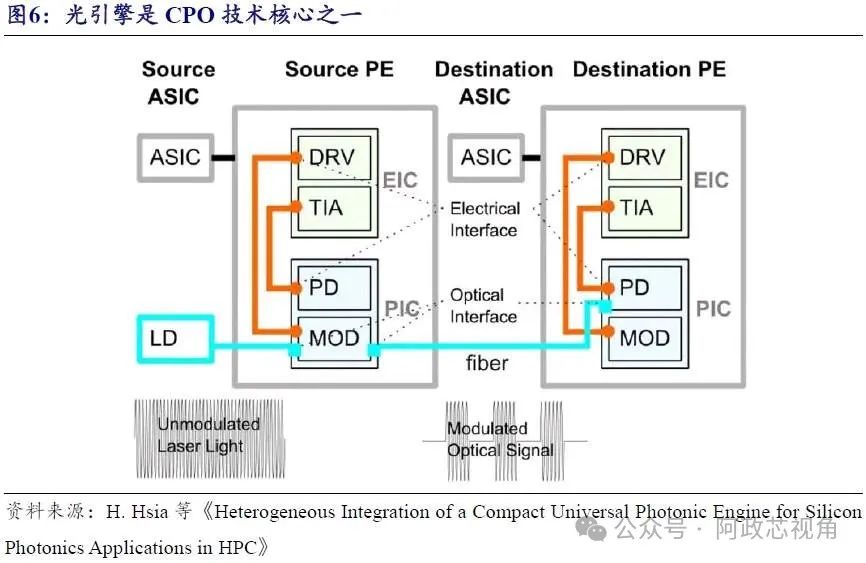

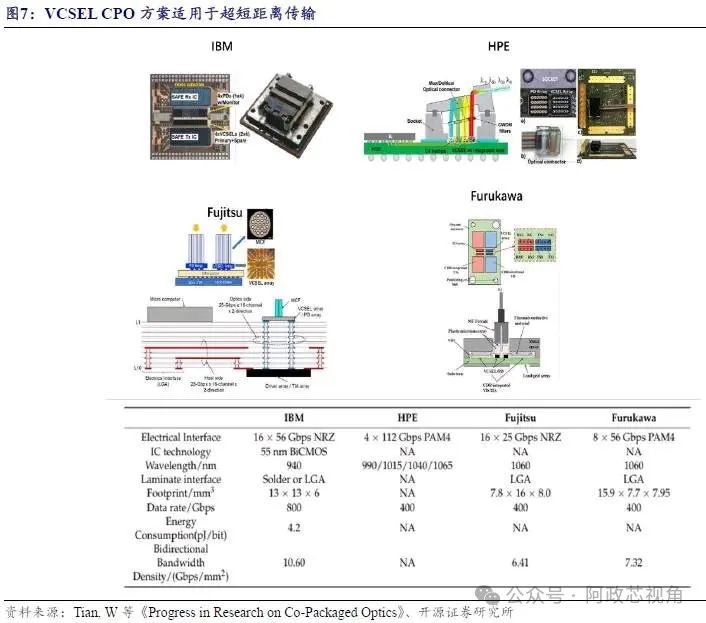

当前参与 VCSEL CPO 研究和开发的主要组织是 IBM、惠普、富士通和古河。IBM 研究院和Coherent 于2022 年联合开展MOTION 项目,项目专注于创建紧凌的光学模块,将多个波长集成在单个芯片,该模块采用了尺寸为 1.64mmx4.64mm 的芯片,没有在电子芯片内合并重新定时功能,有效地服务于低延迟应用场景。

电子芯片、VCSEL 和电源传输(PD)芯片使用 flip-mounting 安装技术贴在玻璃基板上,在最大速度下,考虑到两端的电连接器,MOTION 收发器的功耗为 4pJ/b,约为800gOSFP(FR4)模块的 1/5;惠普的 4 通道 CPO 系统于 2020 年开发,包括990/1015/1040/1065/1090nm 的 5 种波长的 VCSEL 激光器;富士通于2022 年宣布的VCSEL CPO 系统采用16 通道VCSEL 和PD 阵列。

为了实现与多芯光纤(MCF)的耦合,VCSEL 和 PD 排列成弧形,相邻通道之间的距离为 40um。1060nm VCSEL、驱动器和TIA 芯片通过interposer 连接;Furukawa 的VCSELCPO 解决方案采用两组4 通道VCSEL 和PD 阵列,驱动器和 TIA 芯片分别位于VCSEL 和PD 的两侧,光学和电气芯片都直接贴在基板上,并通过引线键合连接。

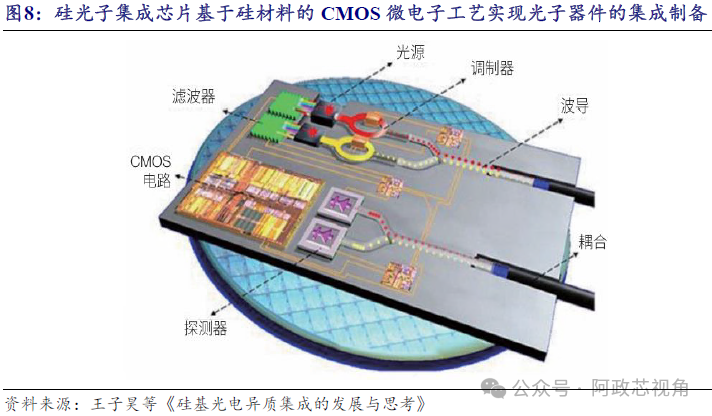

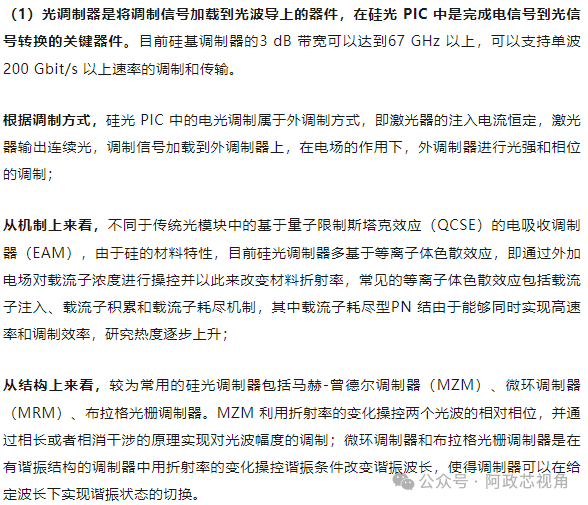

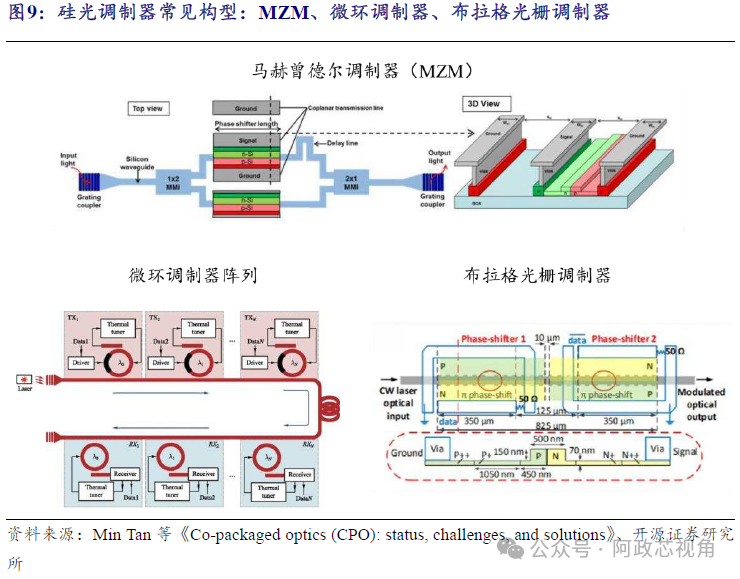

马赫-曾德尔调制器是近十年来研究最多的硅光调制器之一,一般被认为是提高下一代数据中心光网络、5G 光模块速率的主要方案。MZM 最大优点是工作带宽是全带宽,并因此得到了广泛的应用,但由于基于干涉调控,尺寸较大(百um 量级),实际应用中长度一般大于2 mm,另外反向偏置的载流子耗尽型调制器功耗较高;

微环和布拉格光栅基于谐振,尺寸可以相对较小(几十 um 量级),微环调制器凭借其高品质因子(Q 值)的环形谐振腔结构,可以实现极高的集成度与低能耗(驱压小),适合用于光波分复用系统,但是微环调制器高Q 谐振腔要求较窄的光学带宽(典型如 100pm),制造误差容忍度小,温度敏感性较高,同时微环调制器的谐振峰是周期性的,调制器级联时不同信道之间容易串扰;布拉格光栅调制器是单模谐振,因此在工作波长附近仅有一个谐振峰,信道之间不易串扰,但布拉格光栅调制器中光栅固有的反射光会对入射端口其余器件造成不良影响,因此很大程度上失去了外调制优势。

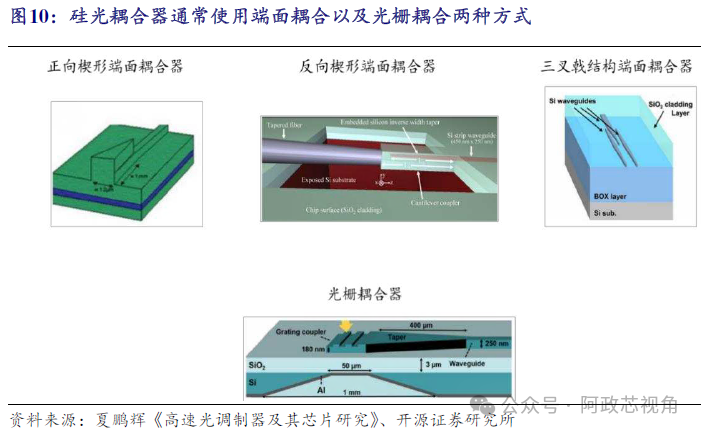

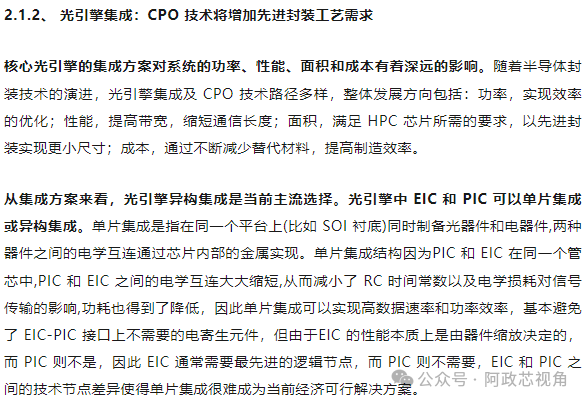

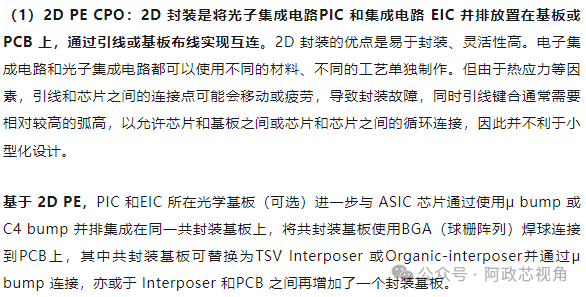

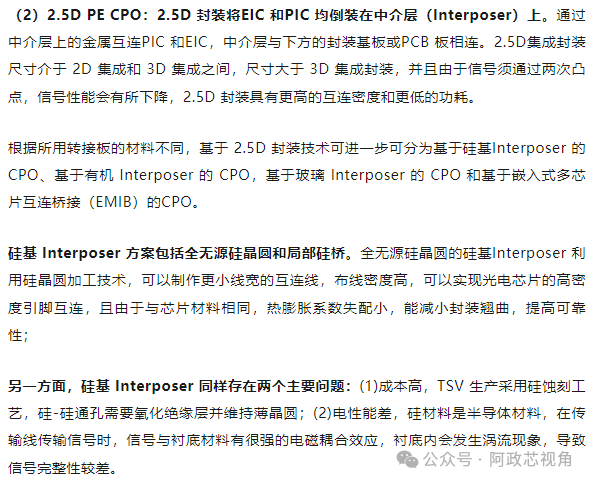

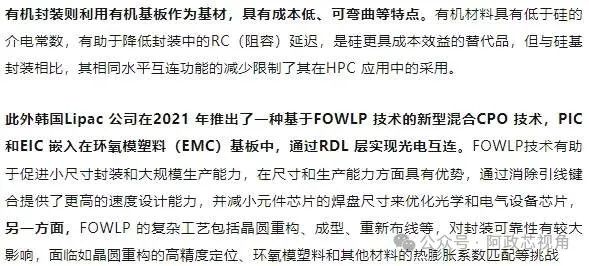

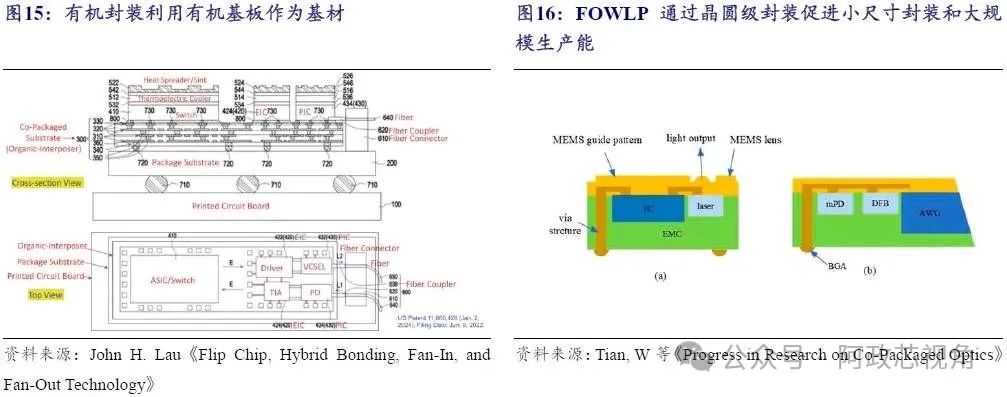

从封装结构上来看,光引擎的异构集成根据封装技术进一步可分为2D、2.5D 和3D 封装,CPO 便是 ASIC 芯片与光引擎进一步异构集成。整体来看,CPO 技术将增加先进封装工艺需求,目前封装工艺仍是限制CPO 技术发展的主要因素之一,其中先进封装技术是指一种采用先进的设计思路和先进的集成工艺技术,如硅通孔(TSV)、重布线(RDL)、倒装(Flip Chip)、凸点(Bumping)、 引线键合(Wire bonding)等对芯片进行封装级重构,能有效提升功能密度的工艺技术。

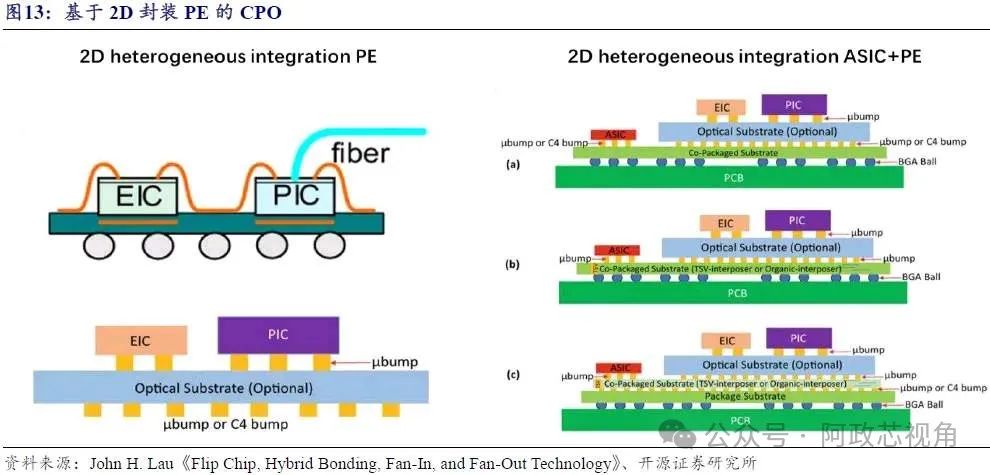

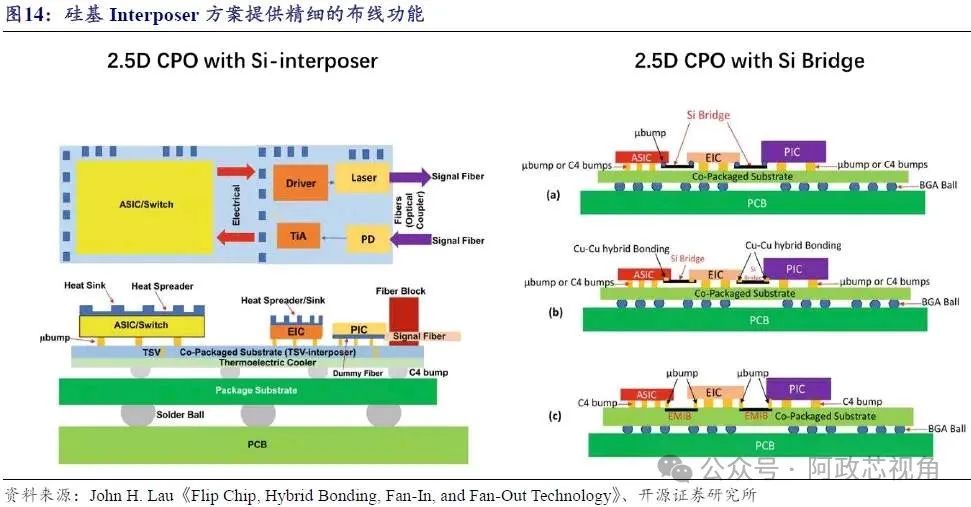

由于硅在材料和制造方面面临着成本的挑战及封装面积的限制,局部硅桥的形式日渐增加,硅桥的异构集成中, ASIC、EIC 和 PIC 之间使用μ bump/无凸点的Cu-Cu 混合键合连接的硅桥连接,同时ASIC、EIC 和PIC 使用μ bump 或 C4 bump连接到共封装基板上。

EMIB 是英特尔的一种 2.5D 封装技术,通过在有机基板中嵌入薄硅桥和多层后道互连,实现局部物理互连术可实现高密度多芯片封装(mcp)的异构集成,用于逻辑存储器和逻辑到电子收发器之间的连接,相比硅interposer 的CPO,EMIB 避免了 TSV 转接板导致的信号完整性问题,并且占用更小面积,既保证了 FPGA 与光电子芯片之间的高速、高密度通信,又有效减少了封装尺寸,有望实现成本和性能的平衡,具有正常的封装良率、不需要额外的工艺、设计简单等优点。

但 EMIB很难在每个进程之初就跟上先进技术的步伐,且 EMIB 端器件之间可能存在差异,例如 FPGA 和HBM 之间收发器的电气特性和制造工艺存在差异,从而导致两端发热不均匀等一系列问题。

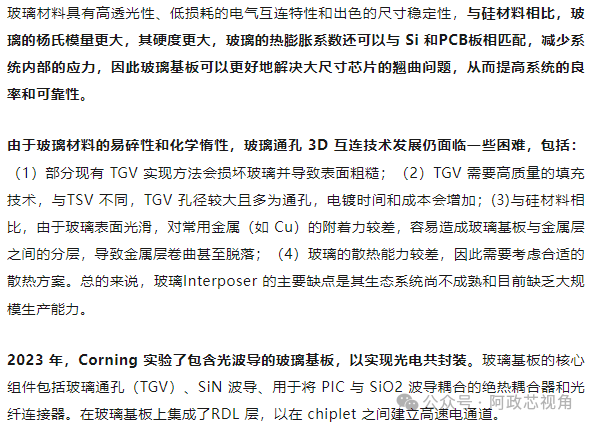

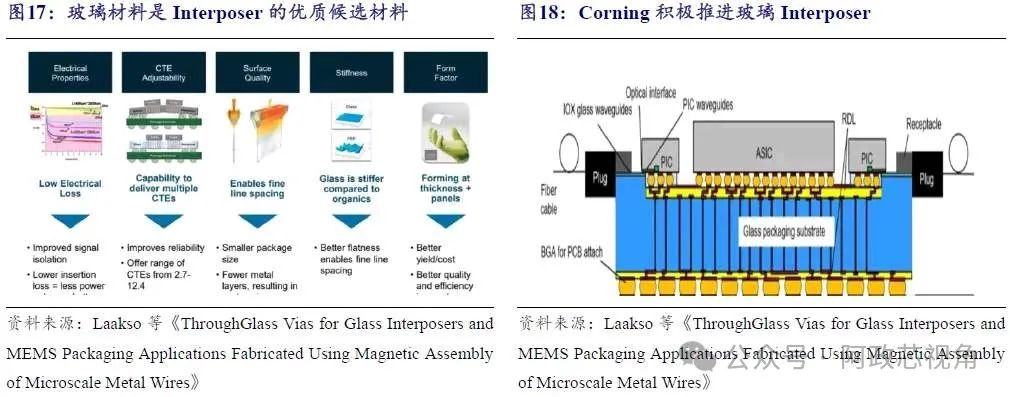

TGV 接头用于供电和接地,同一衬底上所有高分辨率线的薄膜加工简化了制造和组装,与有机衬底上的2.5D Interposer 或EMIB 配置相比,有可能降低整体封装成本。此外,玻璃基板集成了玻璃顶表面下的平面离子交换(IOX)光波导,提供了一个战略性的光学接口,允许封装的PIC 直接瞬态耦合,以实现更低的损耗。

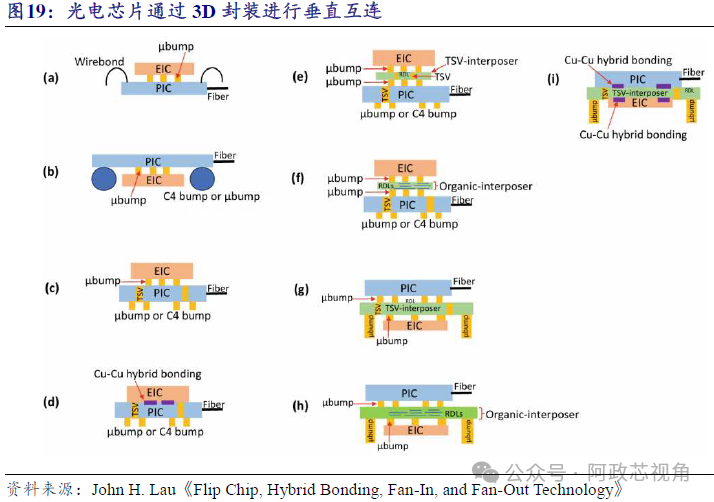

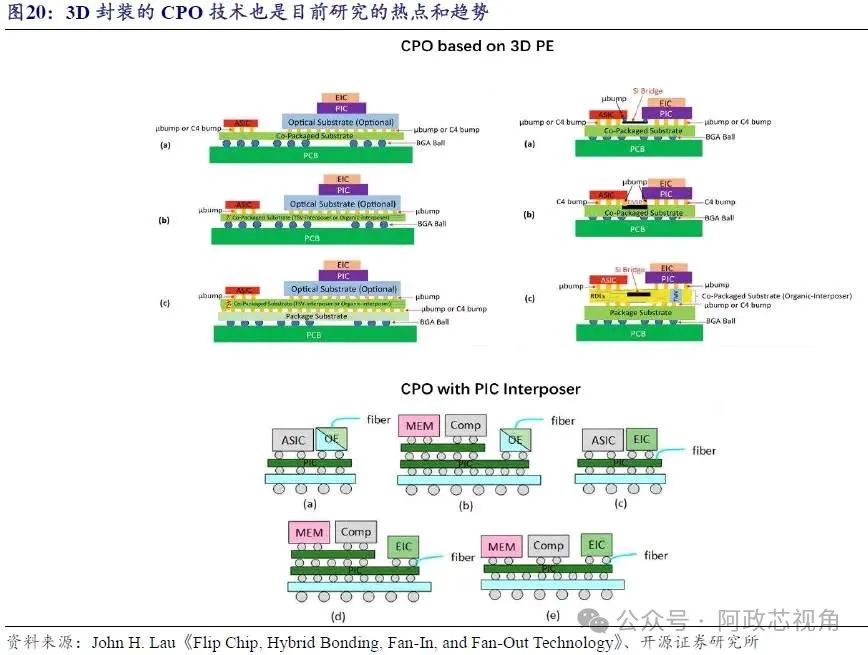

(3)3D PE CPO:3D 封装技术将光电芯片进行垂直互连,不仅能实现更短的互连距离、更高的互连密度和更好的高频性能,还能实现更低的功耗、更高的集成度和更紧凑的封装,基于3D 封装的CPO 技术也是目前CPO 技术研究的热点和趋势。从结构上来看,PIC 和 EIC 的多种 3D 异构集成同样是μ bump、C4 bump、Cu-Cu互联、TSV interposer、Organic interposer、面对面堆叠、背对背堆叠的排列组合。

基于 3D 封装的光引擎,ASIC 芯片可通过 Interposer/基板/硅桥与光引擎互联,或者以其中PIC作为Interposer,再通过金属互联和TSV实现水平和垂直的电气互连。

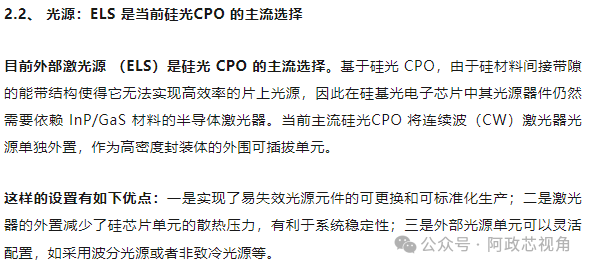

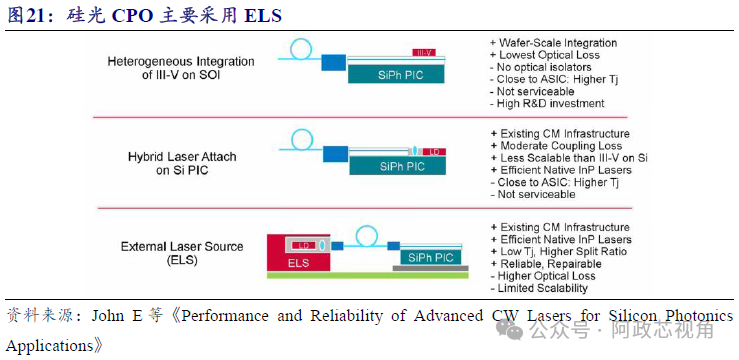

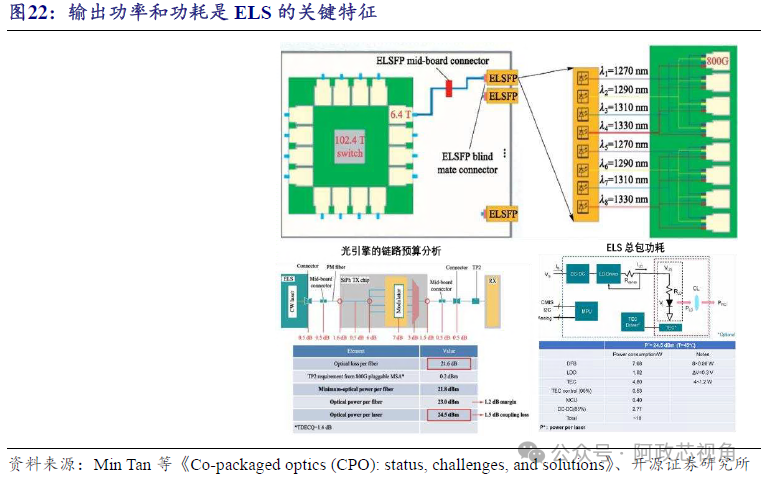

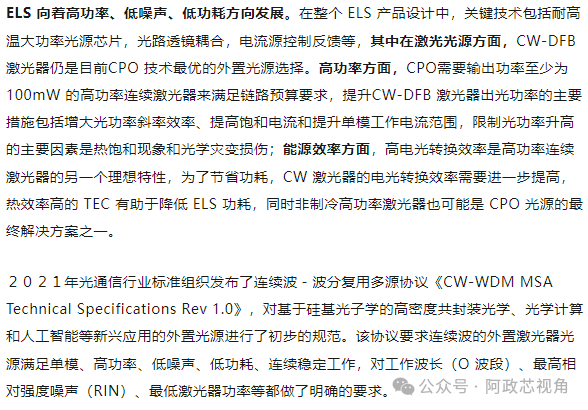

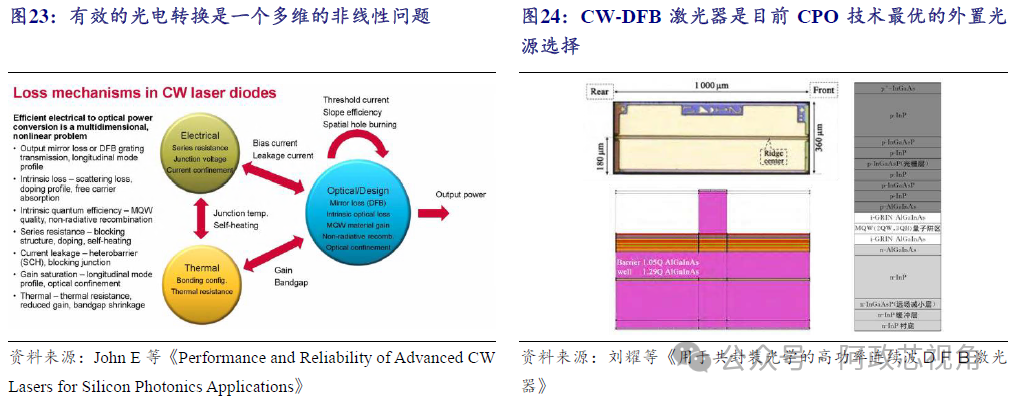

输出功率和功耗是 ELS 的关键特征。激光源作为 CPO 核心器件之一,在 CPO体系中激光器约占系统功耗的 10-20%,硅光 CPO 中 ELS 的引入带来更高的插入损耗,这些损耗需通过增加ELS 的输出功率来补偿。ELS 的输出功率主要由这几方面决定:一是光引擎的链路预算、二是 CW 激光功率分配比、三是硅光引擎损耗,包括调制器和耦合损耗。其中激光芯片的高输出功率是造成大部分功耗的根本原因,此外,热电冷却器 (TEC) 消耗额外的电力来消散激光芯片产生的热量。

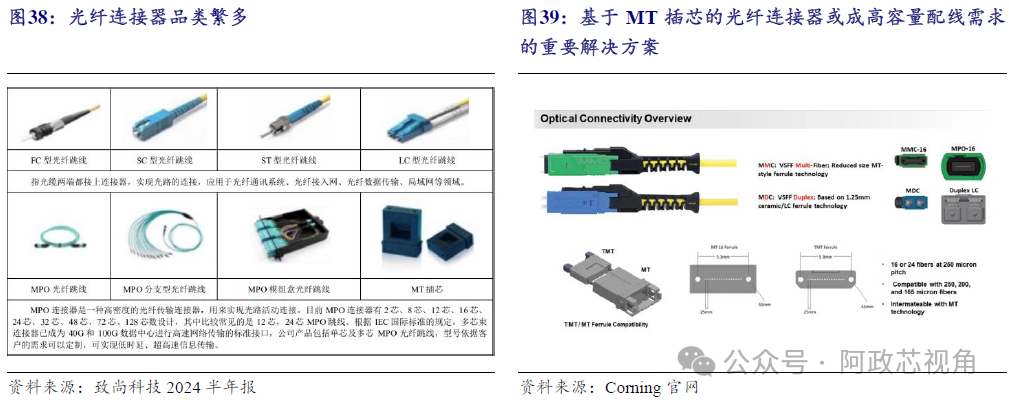

2.3、 光学互联:CPO 光链路较可插拔方案引入额外的光纤及光纤连接器

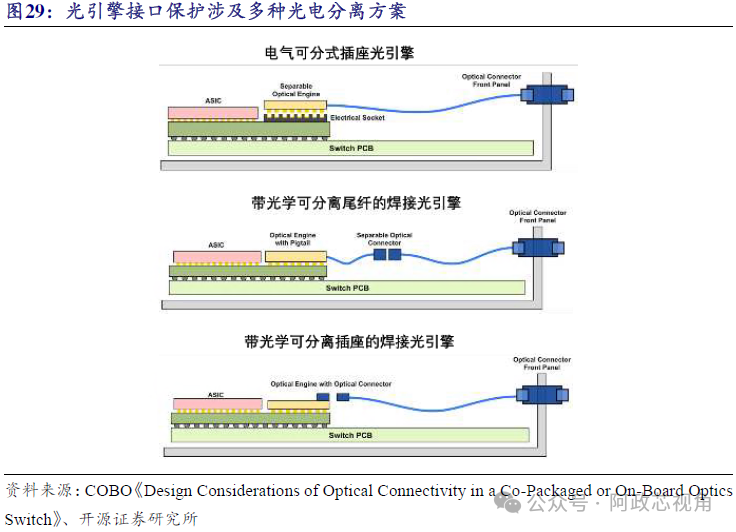

CPO 内部光纤路由的处理也是 CPO 的一大挑战。从构成上来看,CPO 系统的实现涉及各种组件的系统规模集成,包括光引擎、ASIC 封装、光纤阵列、大型体基板、电源管理组件、热组件、路由光纤组件以及外部激光源等。在CPO 内部,为最小化电气路径的距离,从而最大限度地提高电气性能并降低整体ASIC 功耗,光引擎紧密围绕ASIC 放置,CPO 内部光互连路径主要就是从光引擎到CPO 交换机机箱内部的前面板。

其连接方法和连接类型都是影响信号、热量和布线密度的总体系统要求的设计考虑因素,不同的设计选择及光纤离开光引擎的不同方向使得系统内部的光纤布线进一步复杂化,同时在安装应用中,都需注意避免对光纤玻璃表面损坏、大拉应力的应用以及破坏其涂层的完整性。

硅光光引擎通过与光纤阵列单元(FAU)耦合实现光的进出。光纤阵列(FA)是把光纤按照一定的间距排列固定起来形成的光器件,是光进出光器件的通道。光纤阵列分为单芯光纤阵列(SFA)和多芯光纤阵列(MFA),多芯 FA 的制作涉及到精确控制多个光纤之间的间距,需要一个精密的基底给光纤定位,最常用的是硅 V型槽和玻璃V 型槽,通过在V 槽上涂抹紫外胶,用一个平整的小玻璃片将光纤压入V 槽,固化后在 V 槽后的平台区涂上保护胶,最后将端面抛光成预定角度,从而完成 FA 制作,光纤阵列通常有常规 FA 、45°光纤悬出FA 、光纤转90°FA 等。

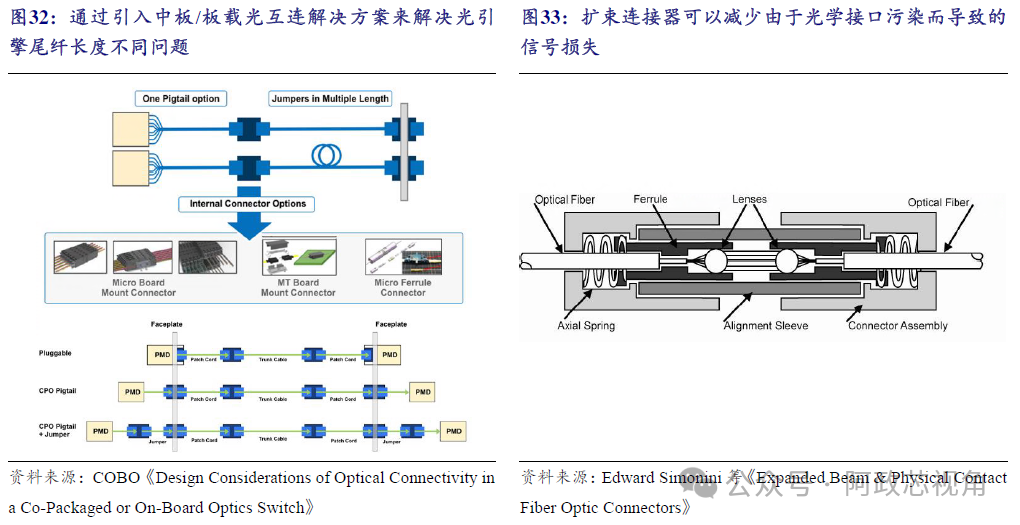

(2)光引擎—前面板:需要不同长度的光纤来路由每个光学引擎,尾纤长度的变化带来设计及安装维护的挑战。

中板/板载光互连解决方案:通过在 OE 和面板之间增加一个中板连接器,并提供各种长度的跳线,尾纤长度可以减少到只有一个设计,可以简化光引擎在面板上的安装,简化光引擎供应商的制造,并降低光引擎和附加尾纤损坏的风险。

另一方面,该方案会增加额外的连接器从而导致光损耗,由于潜在连接点数量的增加,CPO 组件将在设计中添加额外的光纤电缆和连接器,除了CPO 解决方案中包含的电缆外,还增加了一组跳线电缆,可以使用更不敏感且易于清洁的气隙或扩束连接器,来降低这些连接的组装和维护相关的运营成本。

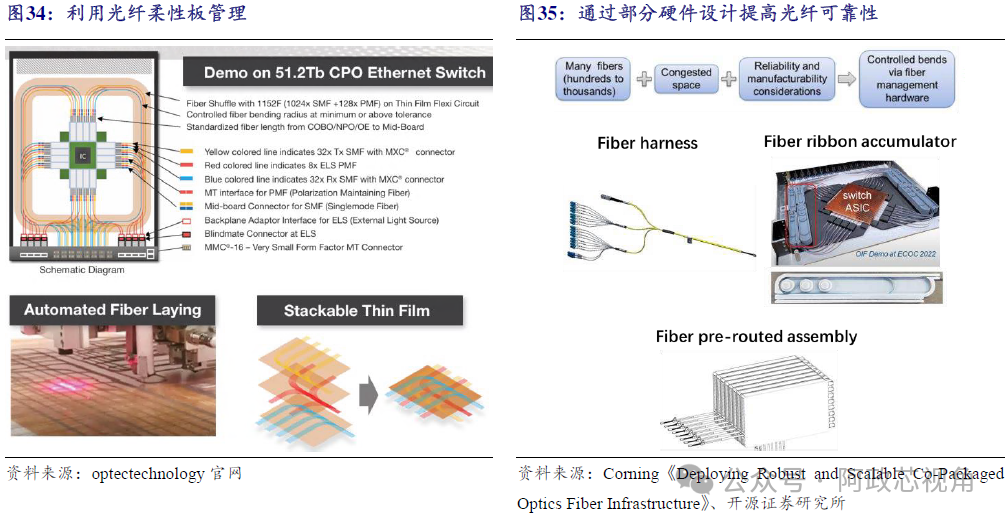

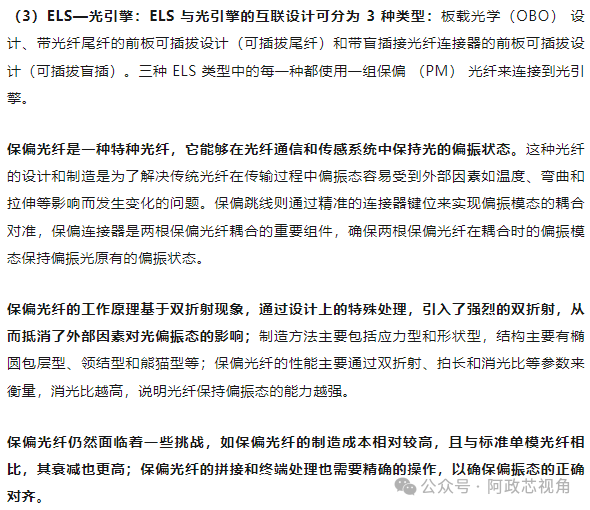

在光纤线束管理方面,还可以进一步引入光纤柔性板(Fiber Shuffle)、带状光纤(Fiber Ribbon)、光缆捆束(Fiber Harness)、光纤带集线器(Fiber ribbon accumulator)、光纤预装盒等来提高光纤的可靠性。其中光纤柔性板提供了一种专门的方法来管理电路板上的数百到数千个光纤,薄膜结构优化了空间,从而增强了密集设备中的气流,同时它是可堆叠的,可以处理多层设计。

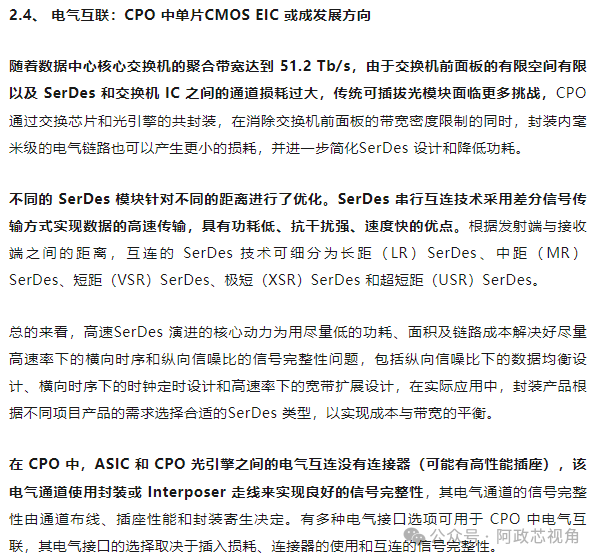

和集成化发展下的产品方向,其一端或两端为矩形状的 MT 插芯链接,通过一个插芯实现多芯光纤的并排链接。

MT(Mechanical Transfer)插芯是 MPO 光纤连接器的核心构造元素,通常用于实现多芯光纤的连接,其关键技术包括塑料成型插芯、金属导向销、插芯端面研磨抛光技术和检查技术等,对精度的要求较高。插芯一般按照金属铸模结构采用注入成型法,由模槽前方的 V 形槽确定及固定中心销位置而制造成型。MT 插芯通过导针和导针孔进行精准连接,确保了光纤连接器的高密度、高速度传输。

总的来看,与使用可插拔光模块的光链路相比,使用CPO 的光纤链路包含更多的光纤连接器。这些附加连接器包括 CPO 交换机面板上的连接器以及任何中板连接器。必须仔细考虑这些连接器的特性,以确保CPO 共封装的光学器件满足可与可插拔模块互操作;向后兼容已安装在数据中心的结构化布线。

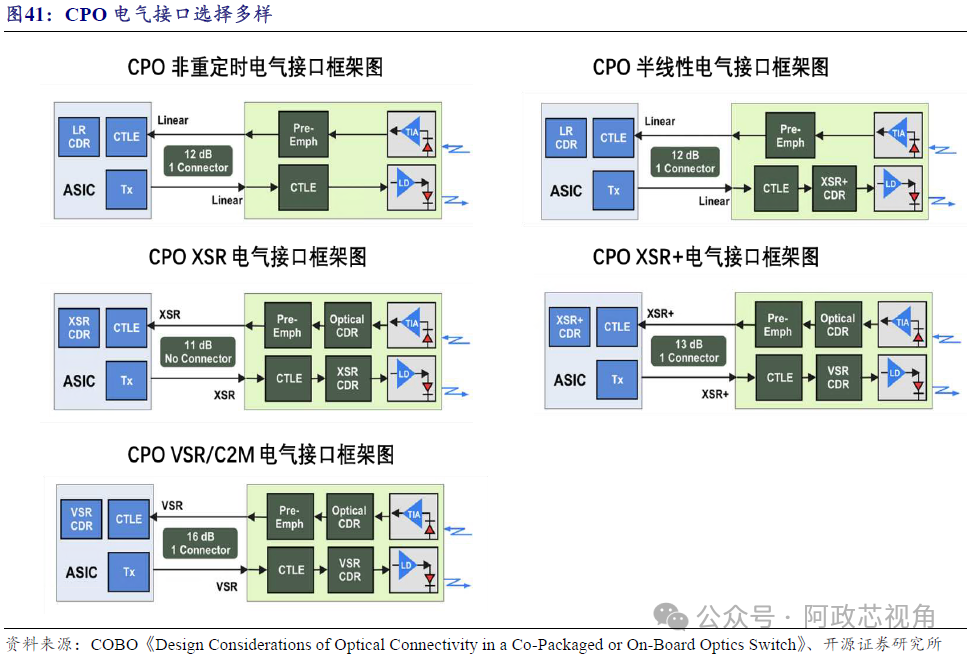

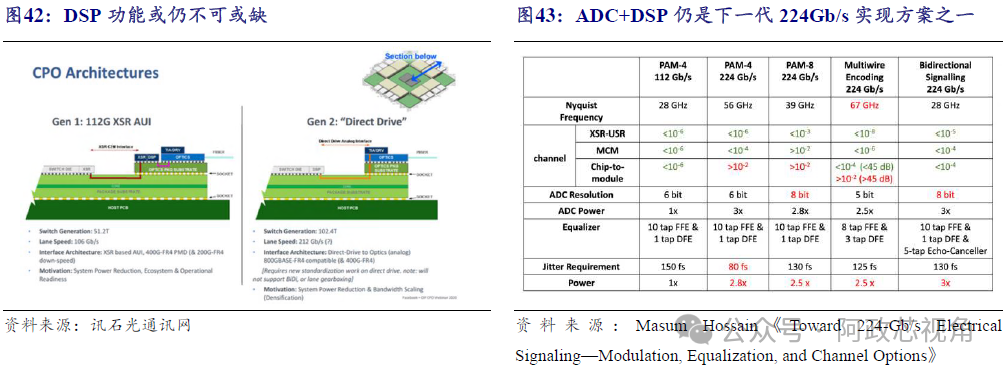

高速CPO 中DSP 功能或仍不可或缺。在传统光模块中,随着通道速度达到 50 Gb/s 及以上,在NRZ 上引入了PAM-4 调制方案 以节省一半的带宽,其中大多数后端功能(如 CDR 和 SerDes)都合并到 CMOS PHY 芯片(有时也称为 DSP)中,其中还引入了密集的数字均衡,以补偿 PAM-4 信号中信号完整性的恶化。

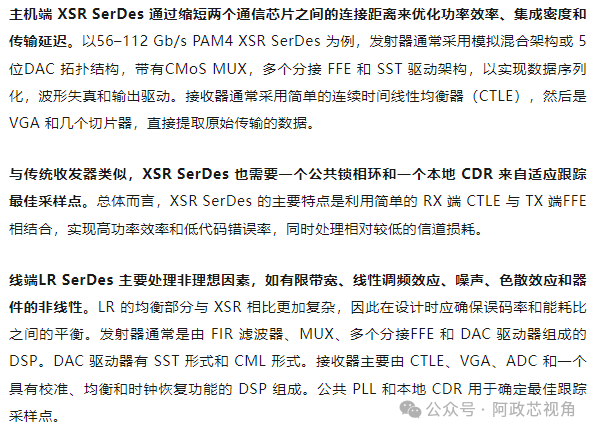

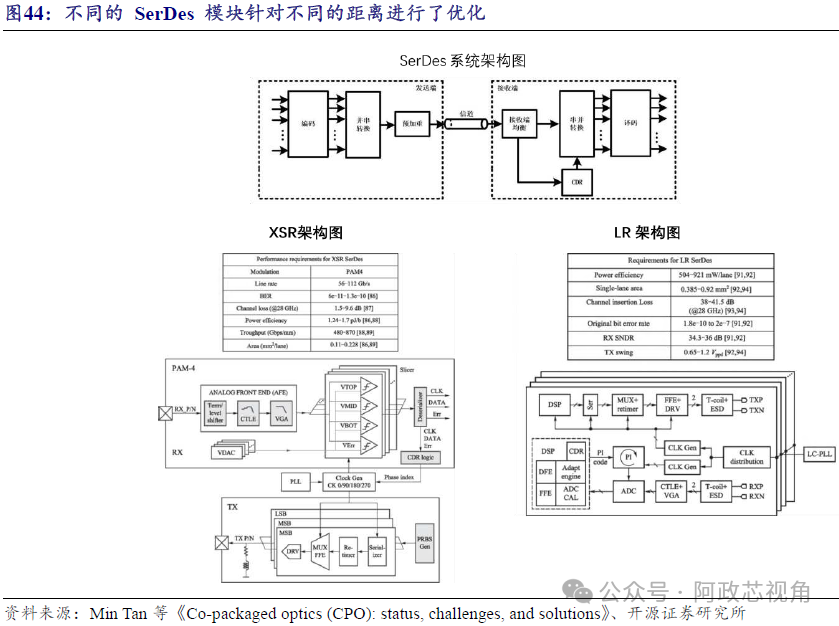

面对未来224Gb/s 高速率通信系统的众多实现方案,其中两类CPO 架构可供参考,一种是交换芯片Die 上引出短距的XSR 接口,通过XSR 接口与芯片基板上的光部分进行电气互连,用于信号调制的DSP 部分与光部分放在一起,另一种则是将DSP部分进一步集成到交换芯片 Die 上,从而简化芯片基板上的光部分,降低芯片内部光部分的功耗。在第一种架构中,重定时芯片的主机侧通过 XSR SerDes 连接到ASIC,重定时芯片的线路侧通过 LR SerDes 连接到光引擎。

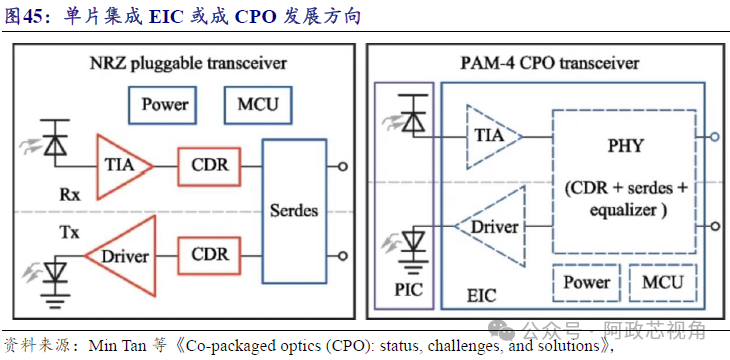

单片 CMOS EIC 或成为重要发展方向。对于需要极高集成度和功耗的 CPO 应用来说,一方面,EIC 单片集成方法或是不可避免的,这需要将模拟 TIA 和Driver进一步集成到 CMOS EIC 芯片中,另一方面,这要求接收器设计技术从模拟优化的 SiGe 转向数字优化的 CMOS,需要克服噪声、带宽和线性度等问题的技术挑战。总的来看,随着这些技术与低功耗和低成本的 CPO 本征优势相结合,单片 CMOS 电子器件或成为未来重要发展方向。

申明:感谢原创作者的辛勤付出。本号转载的文章均会在文中注明,若遇到版权问题请联系我们处理。

----与智者为伍 为创新赋能----

联系邮箱:uestcwxd@126.com

QQ:493826566