RZT2H是多核处理器,启动时,需要一个“主核”先启动,然后主核根据规则,加载和启动其他内核。本文以T2H内部的CR52双核为例,说明T2H多核启动流程。

LSI reset release时,其内置的BOOTROM总是从CR52_0开始执行,即我们可以把CR52_0定义为主核。如果系统配置为程序从External XSPI_FLASH 启动,BOOTROM首先根据存放在external Flash起始位置的Parameter中的定义,从Flash中加载Loader程序。

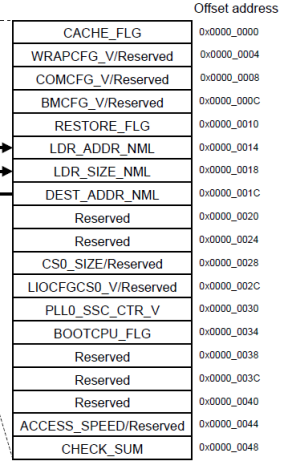

Parameters for the Loader:

存放在External Memory区域的起始位置,存放着与程序加载相关的关键信息,如例如在各个启动模式下,启动期间的CPU缓存设置,用于与外部存储器通信的引导外设(xSPI或SDHI)的配置以及加载程序的size等等。

Parameters for Loader的结构如下:

点击查看大图

除了上述信息,其中DSET_ADDR_NML是跟多核启动相关的关键参数;该参数决定Loader Program的加载地址,而BOOTROM根据这个地址决定接下来在哪个核上,从哪个地址开始执行LOADER程序。

这里补充一下T2H程序结构和基本加载启动流程:

T2H平台,烧录到External Flash上的内容逻辑上分成3部分:

上述的Parameter for Loader;

Loader program;

Application program;

启动时,BOOTROM根据Parameter for Loader从Flash加载Loader program到指定位置开始执行,然后Loader program再加载Application program并跳转执行。

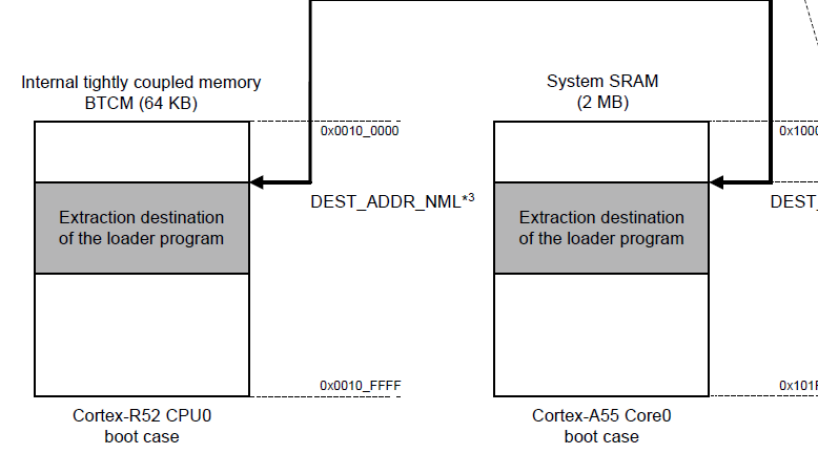

在T2H多核架构下(4xCA55+2xCR52)Loader parameter中的:DEST_ADDR_NML有2个可能的地址范围,即BTCM7或者7System SRAM:

点击查看大图

如果BOOTROM判断到加载地址是在BTCM中,那CR52_0继续执行(second boot CPU仍然是CR52_0),从加载地址开始执行LOADER PROGRAM,并完成整个启动流程。

如果BOOTROM判断到加载地址是SYSTEM,系统会认为second boot CPU是CA55_0,BOOTROM 就会Reset release CA55_0,并把CR52_0转换到WFI状态,然后让CA55_0执行Loader program。

以上介绍了在T2H多核系统中的主核First boot CPU和Second boot CPU的启动过程,但是其他的Core此时都还是在Reset 状态,等待 Second boot CPU为其加载程序和释放。

接下来以52双核为例,说明CR52_0如何完成自身程序加载和加载并启动CR52_1的过程;

在这个示例中,CR52_0用作Second boot CPU,以下步骤是CR52_0的Loader Program需要完成的工作:

根据FSP时钟树,配置LSI的各个Clock;

初始化Loader Program的Data段和BSS段;

配置ADDRESS_EXPANDER_INIT:

Address EXPANDER的作用是:通过映射的方法,使能32 bit Master访问4G area之外的地址空间,详见UM 13.4.5;

TrustedZone 400初始化;

COPY应用程序的PRG段/DATA段/BSS段,到相应的运行RAM空间。如果需要启动其他内核,则把其他内核的PRG/DATA,也COPY到对应RAM区域,然后Release目标内核;

核间通信用到的信号量初始化;

Master MPU初始化;

GIC初始化和系统定义的中断的初始化配置;

TFU初始化;

Main()跳转应用;

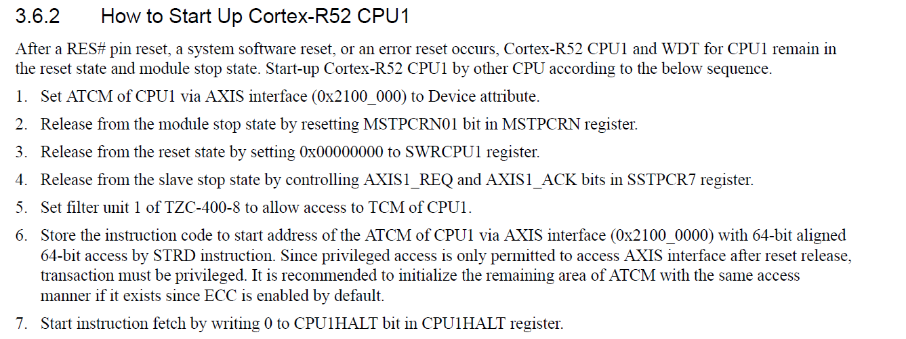

其中步骤5中启动目标CPU(CR52_1)

的步骤如下图:

上述步骤中需要特别强调的地方:

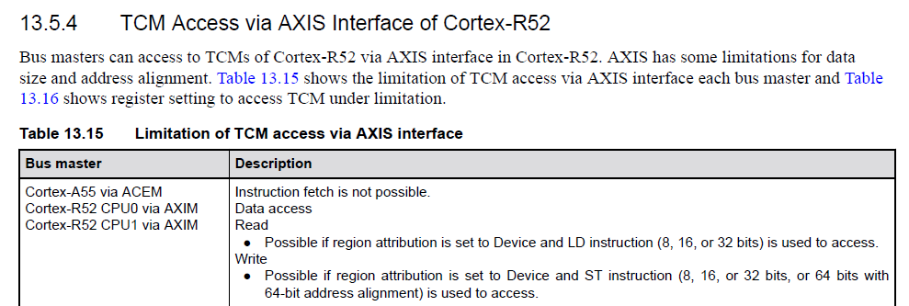

启动过程,需要从CR52_0访问CR52_1的ATCM空间。根据T2H的架构,这个访问只能通过AXI总线,且必须把CR52_1的ATCM region通过MPU配置为Device属性,并且只能使用LD和ST指令;

点击查看大图

对应到代码中,上面的7个步骤在函数SystemInit()文件startup.c中都能找到对应的实现;

重点说明函数bsp_cpu_reset_release()该函数实现上述步骤的2,3,4,6,7;

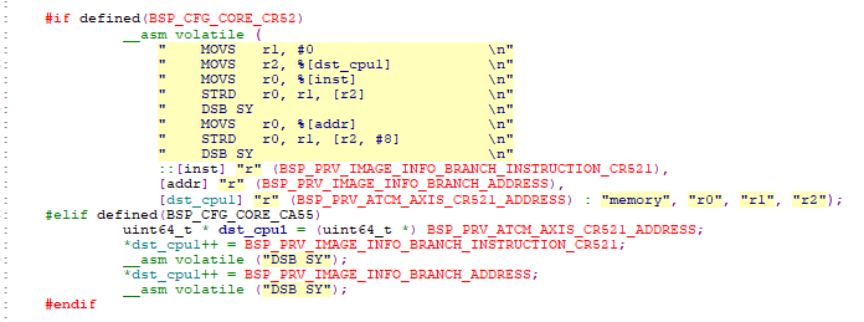

重点分析步骤6:

代码段如下:

点击查看大图

这段代码完成的动作:

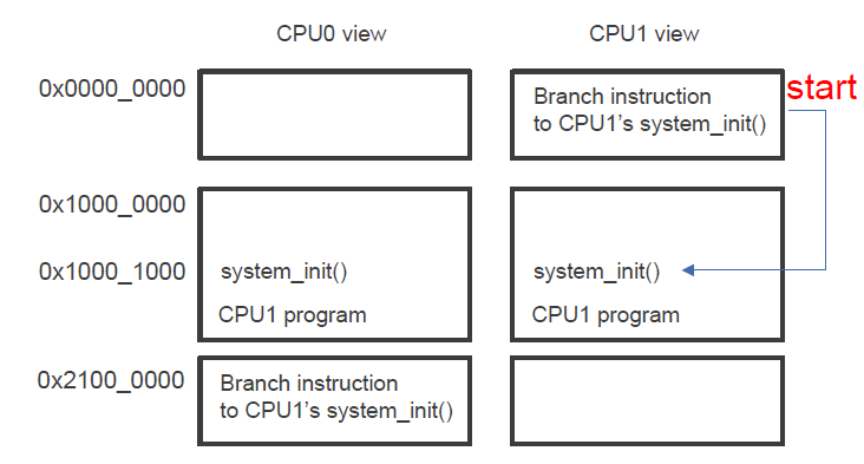

把1st分支指令[inst]经AXIS接口复制到CR52_1 ATCM的起始地址(dst_cpu1:0x2100_000);

复制跳转指令要用到的目标地址(addr);

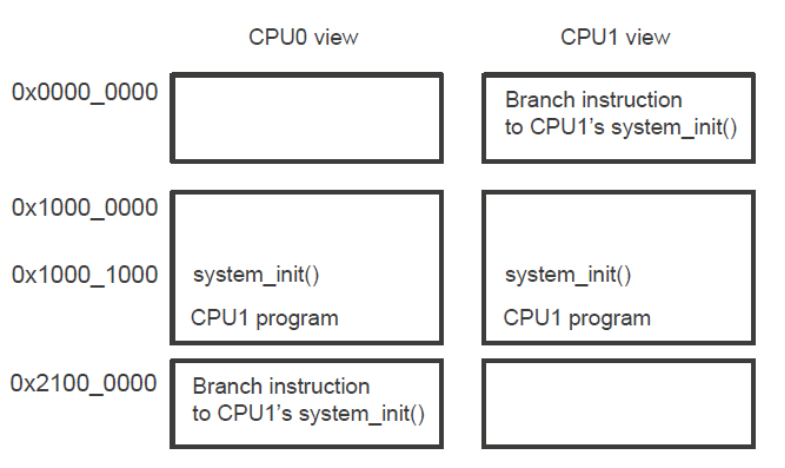

操作到的存储地址如图示:

点击查看大图

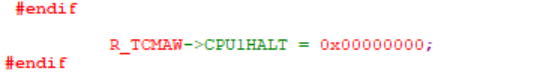

最后步骤7:

CR52_1跳转到入口函数system_init,开始执行:

点击查看大图

以上,以双CR52 Core为例,说明了T2H多核系统的BOOT流程。

如您在使用瑞萨MCU/MPU产品中有任何问题,可识别下方二维码或复制网址到浏览器中打开,进入瑞萨技术论坛寻找答案或获取在线技术支持。

https://community-ja.renesas.com/zh/forums-groups/mcu-mpu/

近期活动一览

1

广州、北京、苏州虚位以待!瑞萨工业以太网技术日席位预约ing

——点击预约,抢占技术前哨 4.09登陆西安

2

板卡评测 | RA4L1功能评估活动开启

——邀你探索RA4L1的奥秘,报名截止4月3日

1

END

1

推荐阅读

视频教程 | RZ/T2H——实现核间通信

工业MPU新标杆,多协议工业以太网+运动控制 - 瑞萨RZ/T2H 新产品量产上市

支持EtherCAT协议的工业用微处理器新选择——瑞萨RZ/T2L评估套件评测(软件篇)